零基础学FPGA(十五)Testbenth 很重要,前仿真全过程笔记(上篇)

时间:02-19

来源:互联网

点击:

上一篇文章我介绍了一下一片简易CPU的设计,今天的课程我讲仿真,也即前仿真。这次课程,小墨同学将和大家从建立工程开始,一步步梳理testbench的书写过程,帮助大家对仿真有一个深刻的概念。以后在做项目时,不要动不动就把程序下到板子里调试,看问题不对再去改程序,再下到板子里调试,如此往返,会浪费大量的时间,简单的项目还好,但是到了大型项目的话,是不可能有这么多时间让我们这样调的。因此,小墨同学在这里说,testbench很重要,做好了仿真,可以为我们节约大量的开发时间。

下面我们开始吧~

一、什么是testbench?

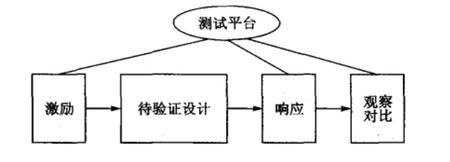

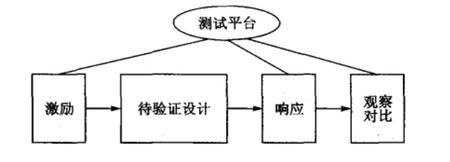

从字面意思上来理解,testbench就是一个测试平台,我们之前已经设计好了我们需要的cpu模块,我们怎么知道我们设计的对于不对呢?我们可以给其施加一个测试激励,例如,给他送时钟和复位信号,由于时钟和复位信号是我们自定义的,因此我们可以产生任意频率的时钟信号和在任意时间给系统复位。

当然我们还可以观察我们cpu的输出,将我们想要观察的输出信号引出来甚至是反馈到cpu内部,都可以,testbench没有像RTL代码设计那样严谨,我们可以在符合语法规则的前提下,随意编写我们的测试文件,有些在RTL代码中不可综合的语句,我们可以在testbench中实现。

二、testbench的结构

小墨同学认为testbench的结构可以分为这几个方面:

1.要先对接口进行例化,即模块之间的链接关系

2.对我们的设计添加激励

3.观察设计输出是否符合要求

三、测试模块设计

要测试我们的cpu需要ROM和RAM模块,这就需要我们先做好这两个模块

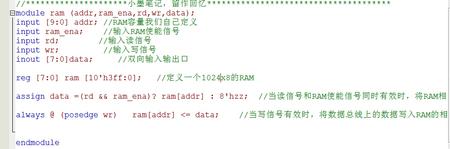

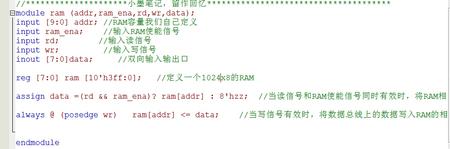

这里定义了一个 1024 x 8 的RAM

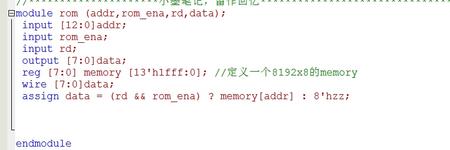

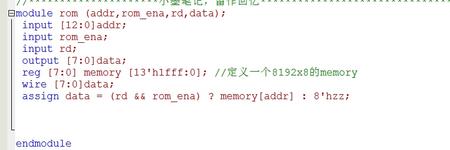

再定义一个8192 x 8 的ROM

ROM和RAM都还没有装入数据,等会我们会调用函数给他们装数据

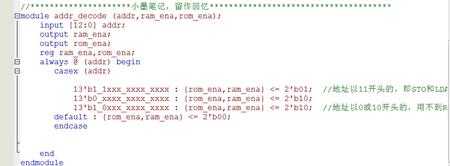

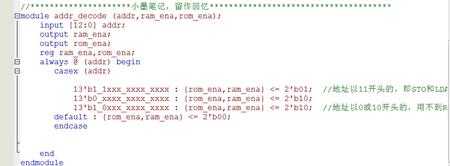

接下来是地址译码器,来控制ROM和RAM的打开与关闭

各模块建立好之后我们就开始仿真了

四、仿真

这次教学我们用的是modelsim SE 10.0 版本进行教学,以下是小墨同学习惯的仿真过程,因个人习惯不同,各位朋友可以按照你们 的方法来做

我习惯直接先在quartus II中建一个.v文件将其保存在原来的工程文件目录中,并命名为cpu_top.v,直接在这里写测试代码

下面大家可以跟着小墨的步骤一起做,来完成cpu 的仿真过程了

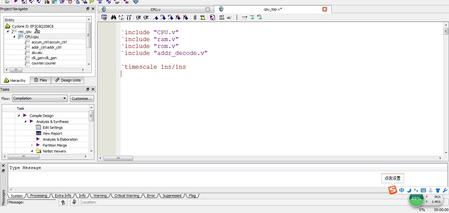

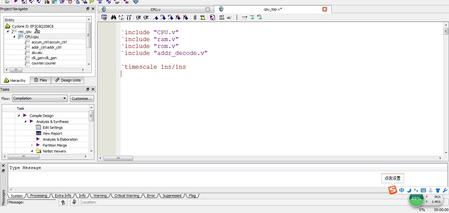

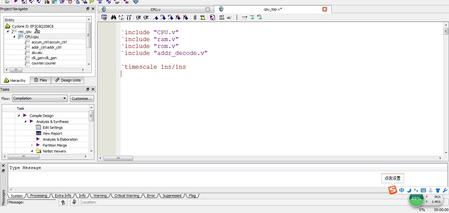

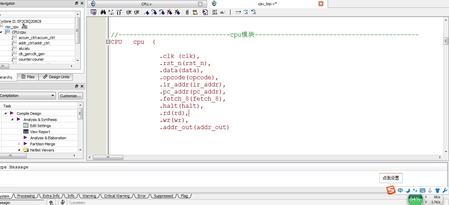

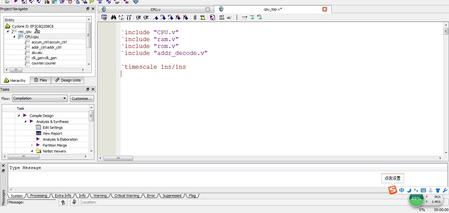

1. 首先,我们需要将我们刚写好的那几个模块包含进去,即CPU模块,ROM模块,RAM模块,地址译码器模块,并写好时间测量度,见下图

2.定义顶层模块

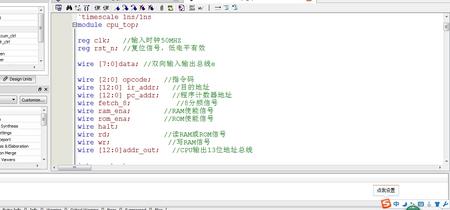

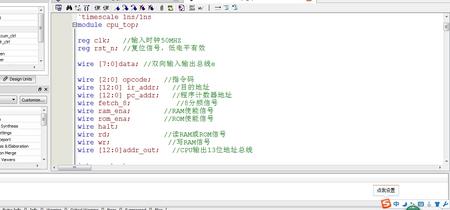

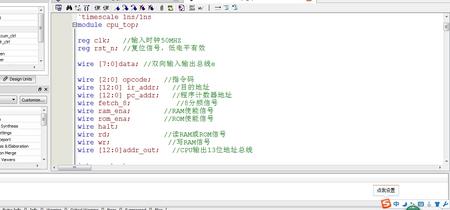

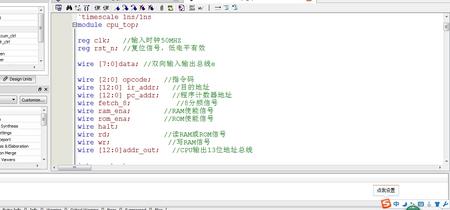

由于我们的设计只有两个输入,即时钟模块和复位模块,凡是输入信号在testbench中通一定义成reg型变量,凡是输出或者双向输入输出信号通一定义成wire型变量,我们的设计只有输入没有输出,故只定义输入和连线即可

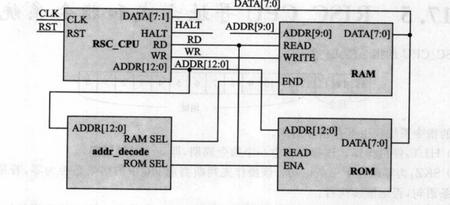

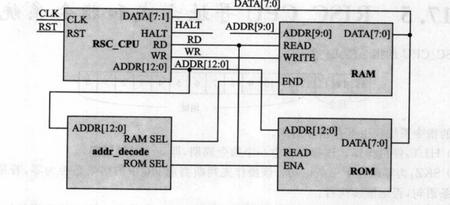

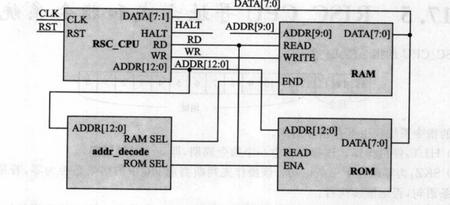

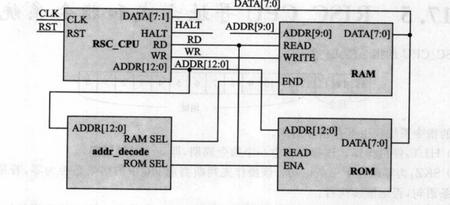

下图便是我们要组成的测试顶层模块图,我们定义的wire型变量,实际就是我们顶层模块中,模块模块与模块间的连线。而这些连线就是我们cpu的输出,这样我们就可以用我们的测试模块来测试我们的cpu是否能正确工作

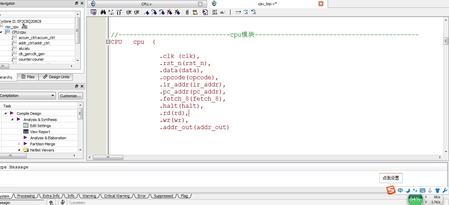

3. 元件例化

就是将各个模块连接起来即可,这里就不做太多的说明了,因为以前都写过很多次了

4.测试激励的书写

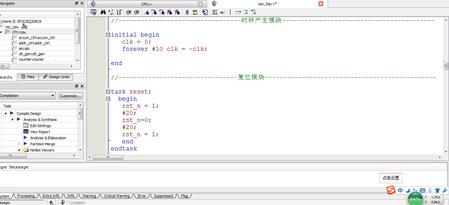

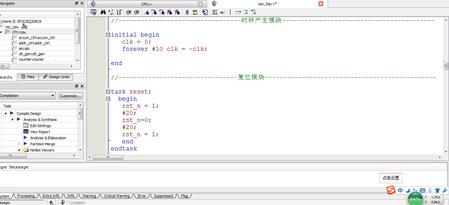

小墨同学习惯上上来先写好时钟产生模块和复位模块.并将复位模块用task任务封装,这样我们在测试过程中就可以随时调用复位任务进行复位

时钟为50Mhz,复位时间为20ns

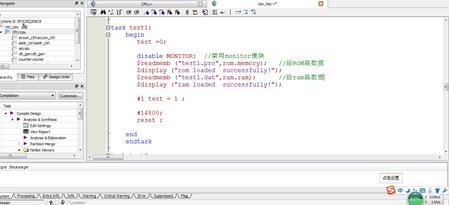

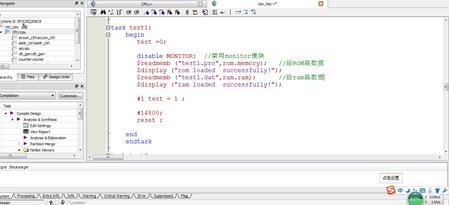

然后,我们再用task封装我们需要的模块,我们来想一下,上电后,CPU会从ROM中读两个时钟周期的数据是吧,但是我们的ROM现在还是空的,所以我们需要一个任务是往ROM中装入程序,给ROM中装数据我们可以用系统函数$readmemb,即打开一个文件,并将其中的数据送到我们之前定义的ROM中去

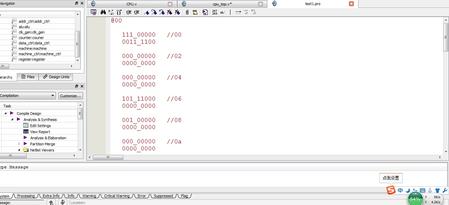

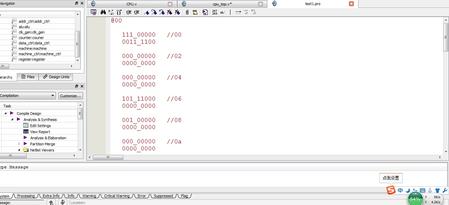

而test1.pro文件时需要我们自己定义的,我们可以在quartusII中再新建一个.v文件,在里面写上我们自己定义的程序,并将其保存为.pro文件即可,至于写什么程序,是我们随便定义的,大家可以参考我之前在上一篇文章中上传的程序中,有一个test1.pro文件,打开之后可以看到是一些16位的数字码,这些码就是我们ROM的地址,从第一行开始,每8位数据位一个地址,注意我们每个地址的高三位是用下划线隔开的,这表明前三位是指令码,这三位会被状态机进行译码,控制CPU执行相应的操作

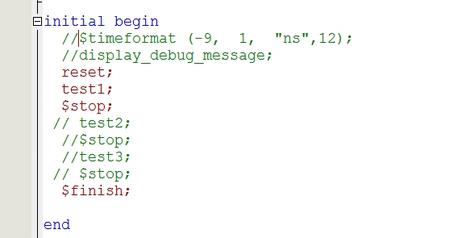

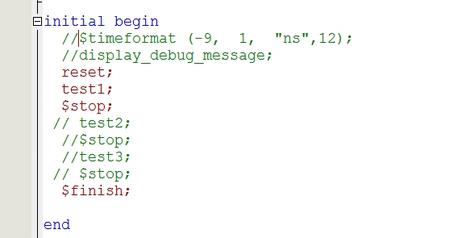

装完ROM和RAM的数据之后,按说就可以了进行波形仿真了,因为cpu是自动读取数据的,下面我们先来做第一步仿真,我先把之后的代码注释掉,大家先看没有被注释掉的代码

里面都是我们之前封装好的函数,刚开始进行复位,然后进行第一步测试,之后停止

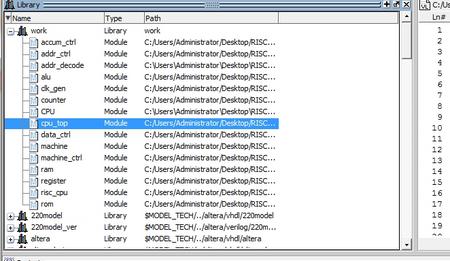

将其保存之后,小墨同学习惯将cpu_top.v文件用modelsim打开,并默认为用其打开,打开后见下图

然后,file——new——library——ok即建好一个库

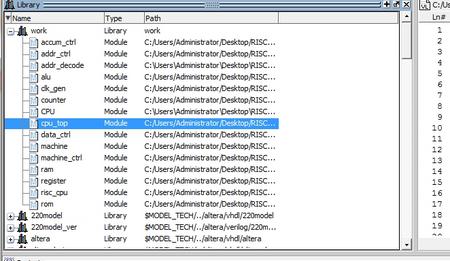

点击左上角的编译按钮,将我们之前写好的所有.v文件全部都编译进去

看到transcript一栏显示编译成功后即可,若没有transcript一栏,可以选择菜单中的view——transcript即可,若显示有红色错误,那就请读者按照它的要求进行修改代码,这说明你的代码有问题,一般是连接问题

编译成功后,双击cpu_top就可以开始波形仿真了

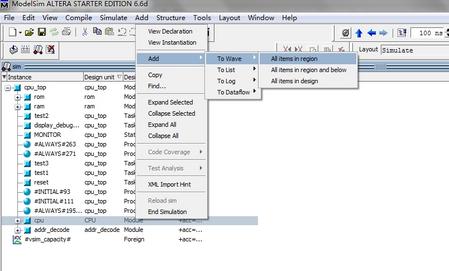

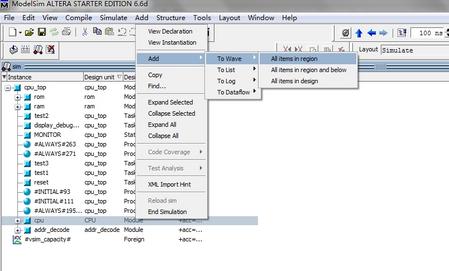

进入仿真页面后,我们右击cpu模块将其加入至波形

请大家看下一篇文章,小墨同学会给大家继续讲解

下面我们开始吧~

一、什么是testbench?

从字面意思上来理解,testbench就是一个测试平台,我们之前已经设计好了我们需要的cpu模块,我们怎么知道我们设计的对于不对呢?我们可以给其施加一个测试激励,例如,给他送时钟和复位信号,由于时钟和复位信号是我们自定义的,因此我们可以产生任意频率的时钟信号和在任意时间给系统复位。

当然我们还可以观察我们cpu的输出,将我们想要观察的输出信号引出来甚至是反馈到cpu内部,都可以,testbench没有像RTL代码设计那样严谨,我们可以在符合语法规则的前提下,随意编写我们的测试文件,有些在RTL代码中不可综合的语句,我们可以在testbench中实现。

二、testbench的结构

小墨同学认为testbench的结构可以分为这几个方面:

1.要先对接口进行例化,即模块之间的链接关系

2.对我们的设计添加激励

3.观察设计输出是否符合要求

三、测试模块设计

要测试我们的cpu需要ROM和RAM模块,这就需要我们先做好这两个模块

这里定义了一个 1024 x 8 的RAM

再定义一个8192 x 8 的ROM

ROM和RAM都还没有装入数据,等会我们会调用函数给他们装数据

接下来是地址译码器,来控制ROM和RAM的打开与关闭

各模块建立好之后我们就开始仿真了

四、仿真

这次教学我们用的是modelsim SE 10.0 版本进行教学,以下是小墨同学习惯的仿真过程,因个人习惯不同,各位朋友可以按照你们 的方法来做

我习惯直接先在quartus II中建一个.v文件将其保存在原来的工程文件目录中,并命名为cpu_top.v,直接在这里写测试代码

下面大家可以跟着小墨的步骤一起做,来完成cpu 的仿真过程了

1. 首先,我们需要将我们刚写好的那几个模块包含进去,即CPU模块,ROM模块,RAM模块,地址译码器模块,并写好时间测量度,见下图

2.定义顶层模块

由于我们的设计只有两个输入,即时钟模块和复位模块,凡是输入信号在testbench中通一定义成reg型变量,凡是输出或者双向输入输出信号通一定义成wire型变量,我们的设计只有输入没有输出,故只定义输入和连线即可

下图便是我们要组成的测试顶层模块图,我们定义的wire型变量,实际就是我们顶层模块中,模块模块与模块间的连线。而这些连线就是我们cpu的输出,这样我们就可以用我们的测试模块来测试我们的cpu是否能正确工作

3. 元件例化

就是将各个模块连接起来即可,这里就不做太多的说明了,因为以前都写过很多次了

4.测试激励的书写

小墨同学习惯上上来先写好时钟产生模块和复位模块.并将复位模块用task任务封装,这样我们在测试过程中就可以随时调用复位任务进行复位

时钟为50Mhz,复位时间为20ns

然后,我们再用task封装我们需要的模块,我们来想一下,上电后,CPU会从ROM中读两个时钟周期的数据是吧,但是我们的ROM现在还是空的,所以我们需要一个任务是往ROM中装入程序,给ROM中装数据我们可以用系统函数$readmemb,即打开一个文件,并将其中的数据送到我们之前定义的ROM中去

而test1.pro文件时需要我们自己定义的,我们可以在quartusII中再新建一个.v文件,在里面写上我们自己定义的程序,并将其保存为.pro文件即可,至于写什么程序,是我们随便定义的,大家可以参考我之前在上一篇文章中上传的程序中,有一个test1.pro文件,打开之后可以看到是一些16位的数字码,这些码就是我们ROM的地址,从第一行开始,每8位数据位一个地址,注意我们每个地址的高三位是用下划线隔开的,这表明前三位是指令码,这三位会被状态机进行译码,控制CPU执行相应的操作

装完ROM和RAM的数据之后,按说就可以了进行波形仿真了,因为cpu是自动读取数据的,下面我们先来做第一步仿真,我先把之后的代码注释掉,大家先看没有被注释掉的代码

里面都是我们之前封装好的函数,刚开始进行复位,然后进行第一步测试,之后停止

将其保存之后,小墨同学习惯将cpu_top.v文件用modelsim打开,并默认为用其打开,打开后见下图

然后,file——new——library——ok即建好一个库

点击左上角的编译按钮,将我们之前写好的所有.v文件全部都编译进去

看到transcript一栏显示编译成功后即可,若没有transcript一栏,可以选择菜单中的view——transcript即可,若显示有红色错误,那就请读者按照它的要求进行修改代码,这说明你的代码有问题,一般是连接问题

编译成功后,双击cpu_top就可以开始波形仿真了

进入仿真页面后,我们右击cpu模块将其加入至波形

请大家看下一篇文章,小墨同学会给大家继续讲解

仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)