ISE时序约束笔记3——Global Timing Constraints

时间:02-19

来源:互联网

点击:

问题思考

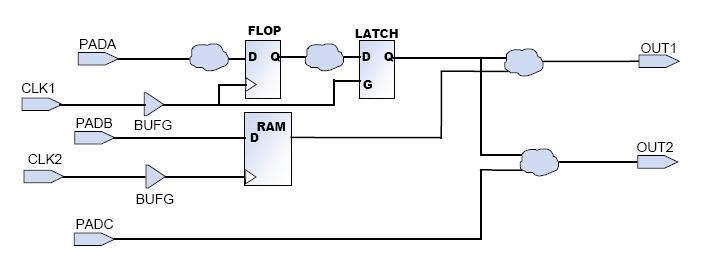

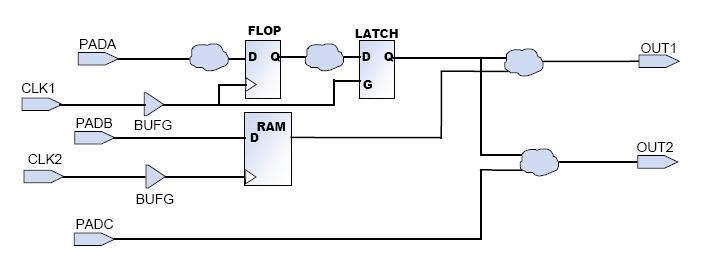

哪些路径是由CLK1进行周期约束?

哪些路径是由pad-to-pad进行约束?

OFFSET约束

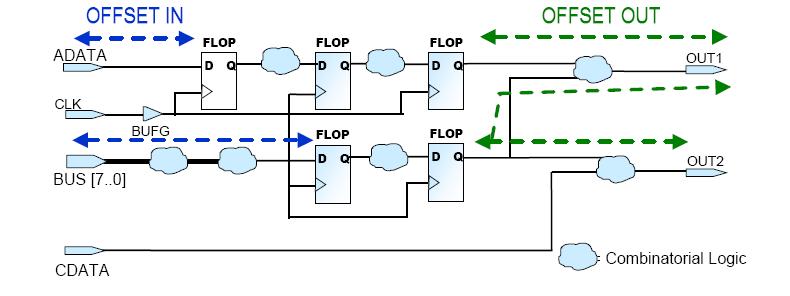

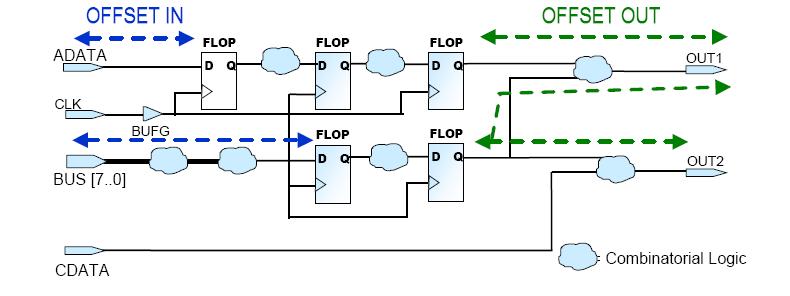

OFFSET约束覆盖以下路径:

——从input pads到同步单元(OFFSET IN)

——从同步单元到output pads(OFFSET OUT)

OFFSET约束特性

OFFSET约束自动计算时钟分布延时

1. 提供最准确的时序信息

2. 大量增加输入信号到达同步单元的时间(时钟和数据路径并行)

3. 大量减少输出信号到达输出管脚的时间(时钟和数据路径先后)

OFFSET约束也可以解释时钟输入抖动——使用抖动确定关联的周期约束

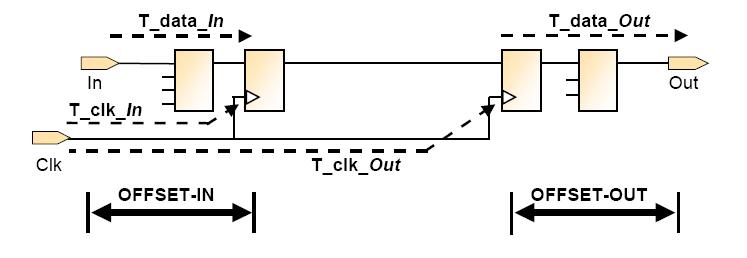

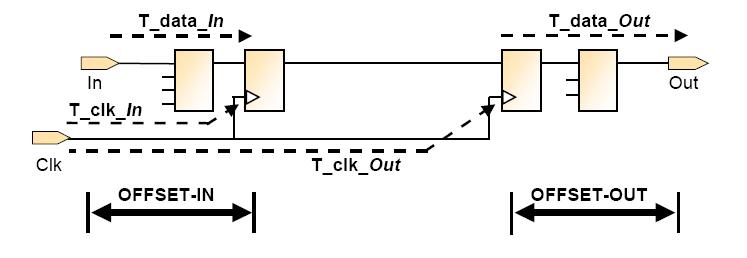

时钟延时

数据路径延时和时钟分布延时都需要在OFFSET计算中使用到

——OFFSET IN = T_data_in – T_clk_in

——OFFSET OUT = T_data_out + T_clk_out

哪些路径是由CLK1进行周期约束?

哪些路径是由pad-to-pad进行约束?

OFFSET约束

OFFSET约束覆盖以下路径:

——从input pads到同步单元(OFFSET IN)

——从同步单元到output pads(OFFSET OUT)

OFFSET约束特性

OFFSET约束自动计算时钟分布延时

1. 提供最准确的时序信息

2. 大量增加输入信号到达同步单元的时间(时钟和数据路径并行)

3. 大量减少输出信号到达输出管脚的时间(时钟和数据路径先后)

OFFSET约束也可以解释时钟输入抖动——使用抖动确定关联的周期约束

时钟延时

数据路径延时和时钟分布延时都需要在OFFSET计算中使用到

——OFFSET IN = T_data_in – T_clk_in

——OFFSET OUT = T_data_out + T_clk_out

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- IP存储让应用和存储走的“更近”(06-09)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)