零基础学FPGA (二十一)SOPC进阶,自定义AD转换IP核设计全流程

时间:01-28

来源:互联网

点击:

四、Avalon-MM总线接口设计

我们知道,我们设计的这个IP核是要挂到Avalon-MM总线上的,作为一个从机,总线需要通过片选信号来访问总线上挂的这些IP,因此,我们也需要给我们的IP设计一个和总线通信的接口

我们设计AD转换的IP核的片选信号低电平有效,当片选信号有效的时候,如果再来一个读信号,那么,数据就会被总线读走,送至CPU

五、自定义IP

好了,下面我们就可以来定义我们自己的IP了

先将我们刚才设计好的AD转换的.V文件复制到我们硬件系统的目录中,并养成一个好的习惯,新建一个文件夹,并命名为IP,以后我们设计的IP都可以放到里面

打开我们之前硬件系统的sopc builder,双击左上角的NEW component ,在HDL file一栏中添加我们的adc.v文件,

在signal一栏中,根据端口的类型配置端口,时钟复位信号不用说,其中我们的与总线接口部分的端口属于总线的从机端口,我们需要把它定义为avalon_slave_0端口类型,信号类型设置为低电平片选,低电平读就好,其他端口设置为conduit类型,信号类型设置为export,因为我们是用来输出到外部器件的端口

在接口一栏中,我们可以设置一些相关参数,一般为默认就好,为了我们数据的稳定性,我们可以把读延时周期设置为4个,保证它有足够的时间去处理数据

然后点击finish,双击我们生成的IP核将它添加到系统工程中即可,然后重新生成硬件系统

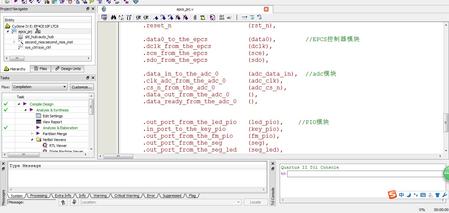

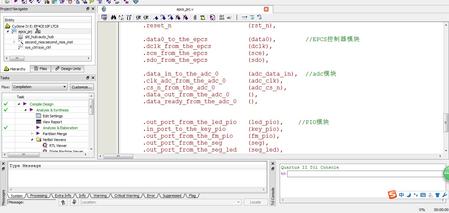

六、硬件系统生成

将生成的新的硬件系统的例化接口声明好,这样在我们的设计顶层又多了这样一个模块,按照惯例分析综合,时序约束,分配管脚,这样我们的硬件系统就设计好了

七、软件部分

因为我的硬件系统上没有AD芯片,这里就只简单说一下软件代码,不做下板调试了

软件部分只讲一下主函数部分,看下图

代码很简单,就是每隔一段时间将采集到的值在窗口打印,不过有个问题需要解释一下,有人会问,我们在自定义IP的时候不是定义了片选端和读信号么,为什么我们没有对它进行操作就可以读数据了呢?

其实我们是不需要对我们的外设进行片选或者读写使能的,因为我们的avalon-MM总线一次只能访问一个从机,我们给出了我们AD转换的IP的地址,就默认片选了这个模块了,又因为我们调用了IO操作的读函数,在定义信号的时候我们定义的是低电平,这样其实就是总线默认帮我们选好了,我们只需要给它一个地址,那么数据就会自动的传到总线上去。

我们知道,我们设计的这个IP核是要挂到Avalon-MM总线上的,作为一个从机,总线需要通过片选信号来访问总线上挂的这些IP,因此,我们也需要给我们的IP设计一个和总线通信的接口

我们设计AD转换的IP核的片选信号低电平有效,当片选信号有效的时候,如果再来一个读信号,那么,数据就会被总线读走,送至CPU

五、自定义IP

好了,下面我们就可以来定义我们自己的IP了

先将我们刚才设计好的AD转换的.V文件复制到我们硬件系统的目录中,并养成一个好的习惯,新建一个文件夹,并命名为IP,以后我们设计的IP都可以放到里面

打开我们之前硬件系统的sopc builder,双击左上角的NEW component ,在HDL file一栏中添加我们的adc.v文件,

在signal一栏中,根据端口的类型配置端口,时钟复位信号不用说,其中我们的与总线接口部分的端口属于总线的从机端口,我们需要把它定义为avalon_slave_0端口类型,信号类型设置为低电平片选,低电平读就好,其他端口设置为conduit类型,信号类型设置为export,因为我们是用来输出到外部器件的端口

在接口一栏中,我们可以设置一些相关参数,一般为默认就好,为了我们数据的稳定性,我们可以把读延时周期设置为4个,保证它有足够的时间去处理数据

然后点击finish,双击我们生成的IP核将它添加到系统工程中即可,然后重新生成硬件系统

六、硬件系统生成

将生成的新的硬件系统的例化接口声明好,这样在我们的设计顶层又多了这样一个模块,按照惯例分析综合,时序约束,分配管脚,这样我们的硬件系统就设计好了

七、软件部分

因为我的硬件系统上没有AD芯片,这里就只简单说一下软件代码,不做下板调试了

软件部分只讲一下主函数部分,看下图

代码很简单,就是每隔一段时间将采集到的值在窗口打印,不过有个问题需要解释一下,有人会问,我们在自定义IP的时候不是定义了片选端和读信号么,为什么我们没有对它进行操作就可以读数据了呢?

其实我们是不需要对我们的外设进行片选或者读写使能的,因为我们的avalon-MM总线一次只能访问一个从机,我们给出了我们AD转换的IP的地址,就默认片选了这个模块了,又因为我们调用了IO操作的读函数,在定义信号的时候我们定义的是低电平,这样其实就是总线默认帮我们选好了,我们只需要给它一个地址,那么数据就会自动的传到总线上去。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)