零基础学FPGA (二十四)必会! 从静态时序分析到SDRAM时序收敛(上篇)

时间:01-28

来源:互联网

点击:

五、关于虚拟时钟

上图中,细心的朋友可能会看到,第一行有一个SDRAM_CLK,这个时钟是怎么来的呢?这个时钟,其实就是我们给外部的芯片模拟了一个时钟,因为外部器件的时钟是我们PLL生成,送到外部管脚去的,并不是我们FPGA的内部时钟,既然不是内部时钟,那么我们就无法对其进行约束,我们只能定义这么一个虚拟的时钟,来尽可能模拟SDRAM的工作时钟。 例如,输入的时候,源寄存器在SDRAM中,目的寄存器在FPGA中,数据的传输是在SDRAM工作时钟下进行的,但是时序分析工具不知道这个时钟,所以我们定义一个虚拟时钟,连接好它的路径,即从哪输出,输到哪,这里的话就是从PLL的clk2输出,到SDRAM的时钟输入引脚了。因为这里是时序约束模型为源同步时序模型,即时钟都是由FPGA产生,在不是源同步时序模型的情况下,就不需要指明虚拟时钟的源和目的,只需要指明周期即可。

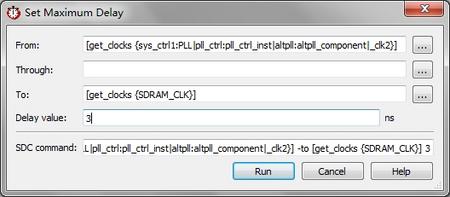

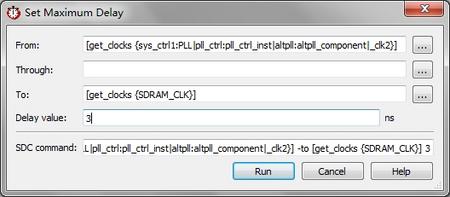

既然是模拟,那我们也应该考虑到这个时钟从PLL输出,到FPGA引脚的这段时间的延时,我们对其进行最大,最小延时约束

同理,我们约束最小值为0ns,这里就不做演示了,方法是一样的

六、I/O时序约束

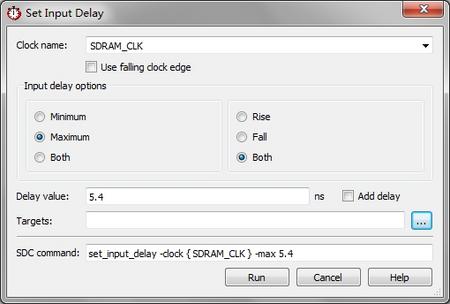

由于篇幅所限,这里就不能一点点的做了,只举个例子吧,做最大输入延时的约束,我们点击 constraints ———> set input delay

时钟名字我们选的就是我们生成的虚拟时钟,为什么呢?因为我们做的是IO约束,即FPGA和SDRAM互相交换数据,既然交换数据肯定是建立在时钟的基础上的,这个时钟,就是虚拟时钟。这个地方比较难懂了,我理解的也不是太好。毕竟我们是要看得是时序报告,时序报告就是建立在虚拟时钟的基础上的一个模拟过程。先理解到这里吧,也不知道该怎么解释了,还请看到的大神给指点一二吧~

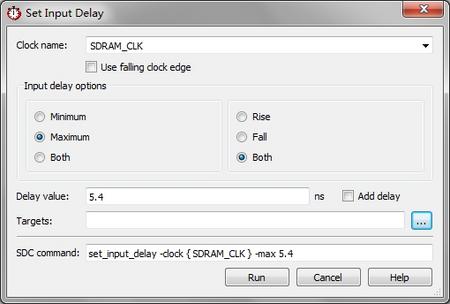

下面我们做最大输入延时的约束,设置我们最大的输入延时为5.4ns

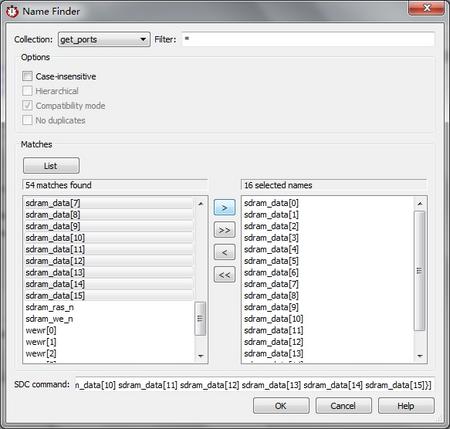

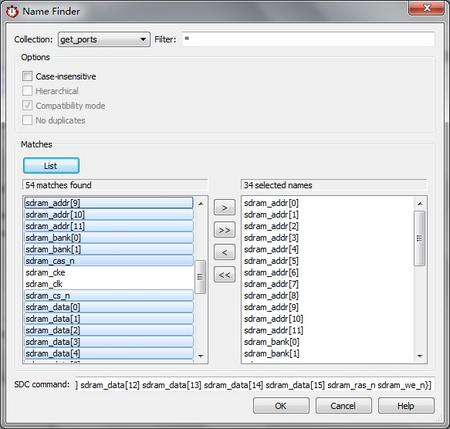

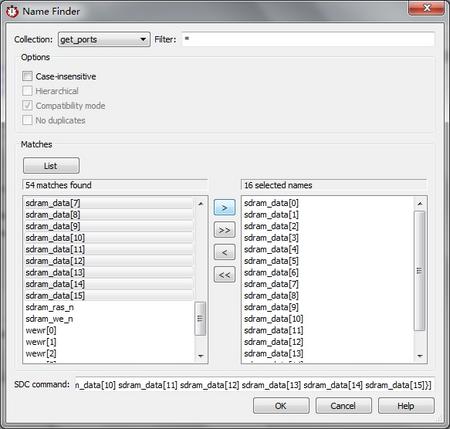

设置输入路径,因为只有SDRAM_data路径是双向的,做输入的时候仅考虑这个路径即可

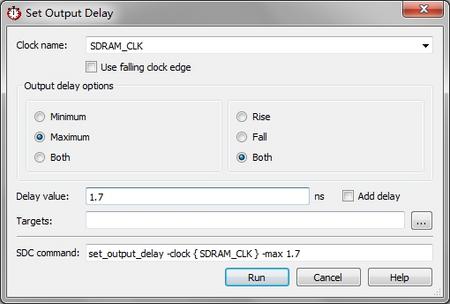

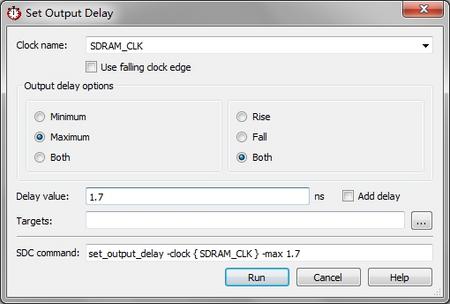

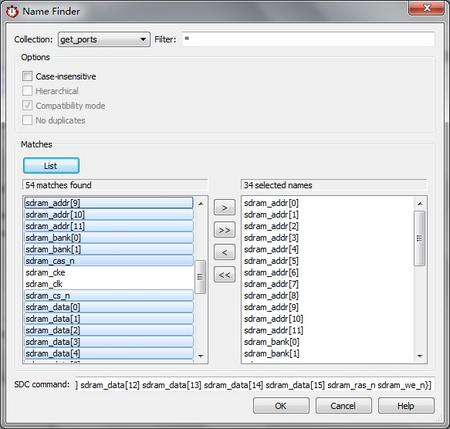

然后我们再做一个输出最大延时的约束,输出最大延时为1.7ns ,输出路径包括除了时钟和时钟有效信号sdram_cke信号外的所有的SDRAM引脚,当然也包括sdram_data信号,为什么不包括cke信号呢?因为cke信号自始至终没有多少次的变化,也就是说对时序要求不严格,对于这种信号,类似还有片选信号,数码管片选,位选等,我们只需对其进行false路径约束即可,即对时序没有严格要求的路径

剩下的路径我就不再做了,都是一样的,将所有路径约束好之后,我们需要开始调sdram工作时钟的相位偏移了

由于篇幅所限,剩下的内容我放到下篇中讲,谢谢大家~

上图中,细心的朋友可能会看到,第一行有一个SDRAM_CLK,这个时钟是怎么来的呢?这个时钟,其实就是我们给外部的芯片模拟了一个时钟,因为外部器件的时钟是我们PLL生成,送到外部管脚去的,并不是我们FPGA的内部时钟,既然不是内部时钟,那么我们就无法对其进行约束,我们只能定义这么一个虚拟的时钟,来尽可能模拟SDRAM的工作时钟。 例如,输入的时候,源寄存器在SDRAM中,目的寄存器在FPGA中,数据的传输是在SDRAM工作时钟下进行的,但是时序分析工具不知道这个时钟,所以我们定义一个虚拟时钟,连接好它的路径,即从哪输出,输到哪,这里的话就是从PLL的clk2输出,到SDRAM的时钟输入引脚了。因为这里是时序约束模型为源同步时序模型,即时钟都是由FPGA产生,在不是源同步时序模型的情况下,就不需要指明虚拟时钟的源和目的,只需要指明周期即可。

既然是模拟,那我们也应该考虑到这个时钟从PLL输出,到FPGA引脚的这段时间的延时,我们对其进行最大,最小延时约束

同理,我们约束最小值为0ns,这里就不做演示了,方法是一样的

六、I/O时序约束

由于篇幅所限,这里就不能一点点的做了,只举个例子吧,做最大输入延时的约束,我们点击 constraints ———> set input delay

时钟名字我们选的就是我们生成的虚拟时钟,为什么呢?因为我们做的是IO约束,即FPGA和SDRAM互相交换数据,既然交换数据肯定是建立在时钟的基础上的,这个时钟,就是虚拟时钟。这个地方比较难懂了,我理解的也不是太好。毕竟我们是要看得是时序报告,时序报告就是建立在虚拟时钟的基础上的一个模拟过程。先理解到这里吧,也不知道该怎么解释了,还请看到的大神给指点一二吧~

下面我们做最大输入延时的约束,设置我们最大的输入延时为5.4ns

设置输入路径,因为只有SDRAM_data路径是双向的,做输入的时候仅考虑这个路径即可

然后我们再做一个输出最大延时的约束,输出最大延时为1.7ns ,输出路径包括除了时钟和时钟有效信号sdram_cke信号外的所有的SDRAM引脚,当然也包括sdram_data信号,为什么不包括cke信号呢?因为cke信号自始至终没有多少次的变化,也就是说对时序要求不严格,对于这种信号,类似还有片选信号,数码管片选,位选等,我们只需对其进行false路径约束即可,即对时序没有严格要求的路径

剩下的路径我就不再做了,都是一样的,将所有路径约束好之后,我们需要开始调sdram工作时钟的相位偏移了

由于篇幅所限,剩下的内容我放到下篇中讲,谢谢大家~

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)