零基础学FPGA (二十四)必会! 从静态时序分析到SDRAM时序收敛(上篇)

时间:01-28

来源:互联网

点击:

下面我们进入正题,今天我们讲时序

一、从静态时序分析说起

我理解的静态时序分析,就是我们在不加激励的情况下,通过对电路进行时序的延迟计算,预计电路的工作流程,对电路提出我们需要的一些约束条件,比如我们需要从A寄存器到B寄存器的延迟不能大于10ns,如果我们不添加时序约束,综合工具可能会有好几条路径,按照它自己的要求来布局布线,那么从A寄存器到B寄存器的时间就有可能是20ns或者15ns之类的路径,而我们需要的是不能大于10ns,因此,我们需要添加时序约束,再根据特定的时序模型,使我们的系统达到设计要求。

这里的时间延迟可能包括我们的PCB板的走线延迟,也包括FPGA内部的走线延迟,时钟延迟等等,这里我们添加的时序约束,就相当于我们在没有下板之前,通过计算,来模拟仿真下板后的延迟情况,并通过时序报告查看有哪些违规路径,以及建立保持时间不平衡的情况,通过时序优化使其达到一个稳定状态的过程。

小墨在做SDRAM时序约束的时候深有体会,即使我们老老实实的按照时序计算公式将延时计算出来添加到工程中去,时序报告也显示时序收敛并且也几乎达到了建立保持时间的平衡状态,前后仿真也没什么问题,以为一切就绪了,但是下板后就是跑不起来,最后我还是改动了一下约束参数,有时候甚至改动幅度与计算幅度相比较大,当然还是在保证时序收敛的情况下,下板之后竟然跑起来了,可能是我第一次接触时序这个高大上的概念,经验不足吧,有的时候真是碰运气....当然等会我将源码共享的时候,大家还需要自己进行时序约束,因为我们的FPGA芯片型号,PCB布局,SDRAM型号都不太一样,那么跑起来是件很困难的事情,所以大家还需要自己亲自学一下这部分的知识,自己去摸索。

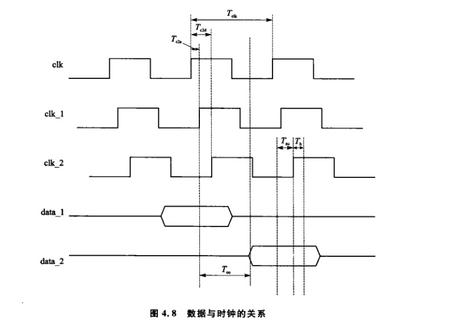

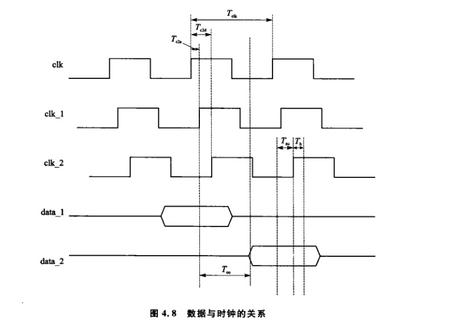

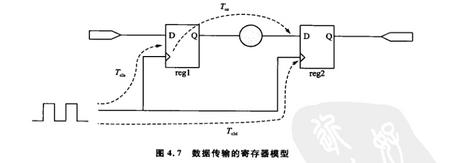

我们直接来看这个图,

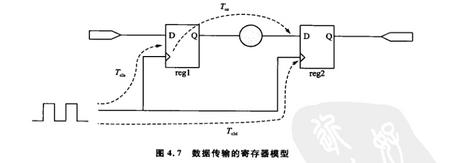

要看懂这个图,当然还需要有一个模型

时序图上的第一个时钟,即我们的源时钟,或者说是我们的晶振时钟,从晶振到达源寄存器,这段路程肯定是有延迟的,我们把这段延迟叫做Tc2s,也即我们的clk1.

时序图上的第二个时钟,是我们的源时钟到达目的寄存器的时钟,即我们的锁存寄存器的时钟,它到目的寄存器的延迟,我们称为Tc2d,也即我们的clk2

clk1 到达源寄存器的时候,将输入的数据锁存器到源寄存器,目的寄存器没有锁存值,等到第二个时钟周期,clk2 到达目的寄存器的时候,将源寄存器的输出数据锁存,数据必须在clk2 到达之前保持稳定,从数据到达目的寄存器到clk2到达这段时间,称为建立时间,当然,数据被锁存之后,还需要保持稳定一段时间,这段时间称为保持时间。

从数据被源寄存器锁存开始,到数据出现在目的寄存器的这段时间,我们称为数据的传输时间Tco

我们做这样一个考虑,如果Tco很长,也就是说,数据从被源寄存器捕获,到出现在目的寄存器的延时时间较长,甚至长到clk2到达目的寄存器的时候还没有到达,那么,我们就说这段路径,建立时间违规,数据不能被正确捕获,这时候,我们就可以给其添加约束,让数据在多少纳秒之内到达,保证数据被捕获,然后综合工具就会根据我们的要求,寻找最佳路径,从而保证建立时间足够长。

同理,假设Tco很短,短到clk2到来的时候,本来应该被捕获的数据,还没有保持一定的稳定时间,就被下一个要捕获的数据给覆盖了,或者说我们捕获到的是下一个要捕获的数据,从而造成保持时间违规

所以,Tco的时间既不能太长,也不能太短,必须在一个合理的范围内,尽量让目的寄存器的捕获时钟在数据的有效窗口内,所以,建立保持时间必须满足下列公式,公式的由来完全来自于时序图

其中,Tc2d - Tc2s叫做时钟偏斜,这两个公式,是我们下面分析SDRAM时序的两个重要公式

再来看一下这两个公式,既然我们要做时序分析,得要知道我们要分析的是哪一部分吧,Tclk我们无法改变,就是系统时钟嘛,时钟偏斜我们也改变不了,因为对于一个特定的FPGA器件,时钟偏斜相对固定,所以我们可以改变的就是Tco,怎么改变呢,就是添加我们的时序约束,让综合工具按照我们的要求寻找符合我们约束的路径,从而满足建立保持时间的要求。

二、输入输出模型以及I/O约束

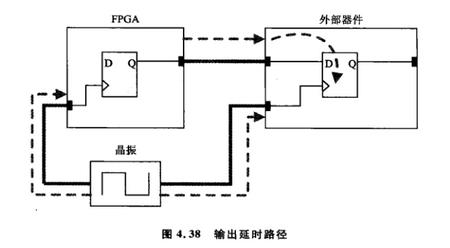

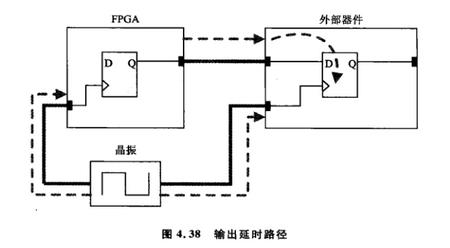

1、先来看输出模型

当然这个输出模型并不是很符合我们的FPGA 和SDRAM的输出模型,是我从网上找来的一张图片,不过没关系,做一下修改就好了。

我们的源时钟需要进入FPGA的PLL中,然后输出给我们的FPGA做内部时钟,在输出到外部做SDRAM的工作时钟,所以上图中,晶振到外部器件的时钟路径,应该是PLL的输出到SDRAM的输出路径

还有,我们之前做的静态时序分析,是基于在FPGA内部的,所以数据的延迟时间只有Tco一个参数,然而,我们的这个输出模型,是源寄存器在FPGA内部,而目的寄存器在我们的SDRAM内部,所以,我们的数据输出路径的延迟,还需要加上一部分,即我们的外部PCB走线延迟

这样,我们的输入延迟 = 数据在FPGA内部传输延迟 Tco + 外部PCB走线延迟

带入我们的静态时序分析的建立时间公式得

Tco Th

即 Tco > Th - 外部PCB走线延时 + 最大时钟网络延时

其中,最小输出延时 = Th - 外部PCB走线延时 + 最大时钟网络延时

即 Tco > 最小输出延时

一、从静态时序分析说起

我理解的静态时序分析,就是我们在不加激励的情况下,通过对电路进行时序的延迟计算,预计电路的工作流程,对电路提出我们需要的一些约束条件,比如我们需要从A寄存器到B寄存器的延迟不能大于10ns,如果我们不添加时序约束,综合工具可能会有好几条路径,按照它自己的要求来布局布线,那么从A寄存器到B寄存器的时间就有可能是20ns或者15ns之类的路径,而我们需要的是不能大于10ns,因此,我们需要添加时序约束,再根据特定的时序模型,使我们的系统达到设计要求。

这里的时间延迟可能包括我们的PCB板的走线延迟,也包括FPGA内部的走线延迟,时钟延迟等等,这里我们添加的时序约束,就相当于我们在没有下板之前,通过计算,来模拟仿真下板后的延迟情况,并通过时序报告查看有哪些违规路径,以及建立保持时间不平衡的情况,通过时序优化使其达到一个稳定状态的过程。

小墨在做SDRAM时序约束的时候深有体会,即使我们老老实实的按照时序计算公式将延时计算出来添加到工程中去,时序报告也显示时序收敛并且也几乎达到了建立保持时间的平衡状态,前后仿真也没什么问题,以为一切就绪了,但是下板后就是跑不起来,最后我还是改动了一下约束参数,有时候甚至改动幅度与计算幅度相比较大,当然还是在保证时序收敛的情况下,下板之后竟然跑起来了,可能是我第一次接触时序这个高大上的概念,经验不足吧,有的时候真是碰运气....当然等会我将源码共享的时候,大家还需要自己进行时序约束,因为我们的FPGA芯片型号,PCB布局,SDRAM型号都不太一样,那么跑起来是件很困难的事情,所以大家还需要自己亲自学一下这部分的知识,自己去摸索。

我们直接来看这个图,

要看懂这个图,当然还需要有一个模型

时序图上的第一个时钟,即我们的源时钟,或者说是我们的晶振时钟,从晶振到达源寄存器,这段路程肯定是有延迟的,我们把这段延迟叫做Tc2s,也即我们的clk1.

时序图上的第二个时钟,是我们的源时钟到达目的寄存器的时钟,即我们的锁存寄存器的时钟,它到目的寄存器的延迟,我们称为Tc2d,也即我们的clk2

clk1 到达源寄存器的时候,将输入的数据锁存器到源寄存器,目的寄存器没有锁存值,等到第二个时钟周期,clk2 到达目的寄存器的时候,将源寄存器的输出数据锁存,数据必须在clk2 到达之前保持稳定,从数据到达目的寄存器到clk2到达这段时间,称为建立时间,当然,数据被锁存之后,还需要保持稳定一段时间,这段时间称为保持时间。

从数据被源寄存器锁存开始,到数据出现在目的寄存器的这段时间,我们称为数据的传输时间Tco

我们做这样一个考虑,如果Tco很长,也就是说,数据从被源寄存器捕获,到出现在目的寄存器的延时时间较长,甚至长到clk2到达目的寄存器的时候还没有到达,那么,我们就说这段路径,建立时间违规,数据不能被正确捕获,这时候,我们就可以给其添加约束,让数据在多少纳秒之内到达,保证数据被捕获,然后综合工具就会根据我们的要求,寻找最佳路径,从而保证建立时间足够长。

同理,假设Tco很短,短到clk2到来的时候,本来应该被捕获的数据,还没有保持一定的稳定时间,就被下一个要捕获的数据给覆盖了,或者说我们捕获到的是下一个要捕获的数据,从而造成保持时间违规

所以,Tco的时间既不能太长,也不能太短,必须在一个合理的范围内,尽量让目的寄存器的捕获时钟在数据的有效窗口内,所以,建立保持时间必须满足下列公式,公式的由来完全来自于时序图

其中,Tc2d - Tc2s叫做时钟偏斜,这两个公式,是我们下面分析SDRAM时序的两个重要公式

再来看一下这两个公式,既然我们要做时序分析,得要知道我们要分析的是哪一部分吧,Tclk我们无法改变,就是系统时钟嘛,时钟偏斜我们也改变不了,因为对于一个特定的FPGA器件,时钟偏斜相对固定,所以我们可以改变的就是Tco,怎么改变呢,就是添加我们的时序约束,让综合工具按照我们的要求寻找符合我们约束的路径,从而满足建立保持时间的要求。

二、输入输出模型以及I/O约束

1、先来看输出模型

当然这个输出模型并不是很符合我们的FPGA 和SDRAM的输出模型,是我从网上找来的一张图片,不过没关系,做一下修改就好了。

我们的源时钟需要进入FPGA的PLL中,然后输出给我们的FPGA做内部时钟,在输出到外部做SDRAM的工作时钟,所以上图中,晶振到外部器件的时钟路径,应该是PLL的输出到SDRAM的输出路径

还有,我们之前做的静态时序分析,是基于在FPGA内部的,所以数据的延迟时间只有Tco一个参数,然而,我们的这个输出模型,是源寄存器在FPGA内部,而目的寄存器在我们的SDRAM内部,所以,我们的数据输出路径的延迟,还需要加上一部分,即我们的外部PCB走线延迟

这样,我们的输入延迟 = 数据在FPGA内部传输延迟 Tco + 外部PCB走线延迟

带入我们的静态时序分析的建立时间公式得

Tco Th

即 Tco > Th - 外部PCB走线延时 + 最大时钟网络延时

其中,最小输出延时 = Th - 外部PCB走线延时 + 最大时钟网络延时

即 Tco > 最小输出延时

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)