FPGA 101 手把手课堂:Vivado IPI 为 Aurora 设计开放 FPGA 共享资源

时间:01-20

来源:互联网

点击:

3x4 单信道设计的最优信道选择 | ||

| GTQ2 | Master1_3 | Master1_4 |

| Slave2_3 | Slave2_4 | |

| GTQ1 | Slave2_1 | Slave2_2 |

| Slave1_4 | Master1_2 | |

| GTQ0 | Slave1_3 | Slave1_2 |

| Master1_1 | Slave1_1 | |

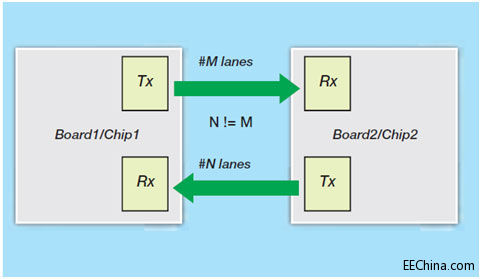

图 4–用 Aurora 实现跨链路的非对称数据传输

7 系列 Aurora 内核需要一个额外的动态重配置端口 (DRP) 时钟输入,否则将需要使用一个 BUFG。如果 Aurora 的自由运行时钟频率选定在允许的 DRP 时钟范围内,那么 Aurora 输出的自由运行时钟可以重复使用并连接回到 DRP 时钟。这样您可节省所生成设计中的 BUFG 数量。

在为多个 Aurora 设计选择线路速率时,您应记住:

如果线路速率是整数倍数,便于时钟推导和在多条链路之间共享,这样您就可共享时钟资源。如果将共享逻辑特性延伸到谐波线路速率,您就可以通过少量的额外时钟分频器为从机 Aurora 内核生成所需的输入频率。

未来机遇

Aurora 具有很高的灵活性,可用来创建多种系统配置和应用。在赛灵思 Vivado IP Integrator 这样的强大工具帮助下,较高的设计输入生产力和系统级资源共享正在加速 All Programmable 应用领域的创新。凭借赛灵思 UltraScale 架构,具备更多 GT 通道的器件可受益于更强的 GT 线路速率支持,因此能够实现更多的设计可能性和更高的资源利用率。

表 5–在 48 条单信道设计中使用共享逻辑特性所实现的资源优势

48 条单信道设计 | ||

| 资源 | 无共享逻辑 | 有共享逻辑 |

| MMCME2_ADV | 48 | 4 |

| IBUFDS_GTE2 | 48 | 4 |

| GTE2_COMMON | 48 | 12 |

| GTXE2_CHANNEL | 48 | 48 |

如需评估 Aurora 内核,敬请查看IP Catalog、IPI 和 Aurora 产品 Web 页面:http://china.xilinx. com/products/design_resources/conn_ central/grouping/aurora.htm.

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)