FPGA 101 手把手课堂:Vivado IPI 为 Aurora 设计开放 FPGA 共享资源

时间:01-20

来源:互联网

点击:

赛灵思的 IP Integrator 工具可帮助您改善设计输入生产力和多核 Aurora 设计的资源优化。

作者:

K Krishna Deepak

赛灵思高级设计工程师

kde@xilinx.com

Dinesh Kumar

赛灵思高级工程经理

dineshk@xilinx.com

Jayaram PVSS

赛灵思高级工程经理

jayaram@xilinx.com

Ketan Mehta

赛灵思高级IP产品经理

ketanm@xilinx.com

客户在必须由单个 FPGA 实现的大型设计中使用多个知识产权 (IP) 实例时,面临的主要挑战之一是如何在整个系统中有效共享资源。赛灵思 Aurora 串行通信内核的共享逻辑特性使用户可以在多个实例中共享资源。Vivado 设计套件中的 IP Integrator 工具对于充分利用共享资源至关重要。

电子行业正快速转向高速串行连接解决方案,同时逐渐舍弃并行通信标准。行业标准串行协议具有固定的线路速率和确定的信道宽度,有时无法充分利用千兆位串行收发器的功能。

Aurora 是赛灵思的高速串行通信协议,一直在行业内非常受欢迎。当某些应用领域中的行业协议实现过程太过复杂或者太耗费资源时,Aurora 通常是首选方案。Aurora 能实现低成本、高数据速率的可扩展IP解决方案,可用于灵活地构建高速串行数据通道。

需要同时对线路速率和通道宽度进行扩展的高性能系统和应用正在期待将 Aurora 作为解决方案。此外,Aurora 还被应用于 ASIC 设计以及包含多块 FPGA 的系统(用背板传输千兆位的数据)中。Aurora 采用简单的帧结构,并具有协议扩展流量控制功能,可用于封装现有协议的数据。它的电气要求与产品设备兼容。赛灵思提供 Aurora 64b66b 和 Aurora 8b10b 内核,作为 Vivado 设计套件 IP 目录的一部分。

Vivado IP Integrator (IPI) 是用于复杂多核系统中资源优化的重要工具。就这一点而言,IPI 将帮助您充分利用 Aurora 64b66b 和 Aurora 8b10b 内核中的共享资源,尤其是“共享逻辑”特性。为了方便起见,我们重点介绍 Aurora 64b66b IP,同时您要了解类似技术也适用于 Aurora 8b10b 内核。

AURORA 的共享资源一览

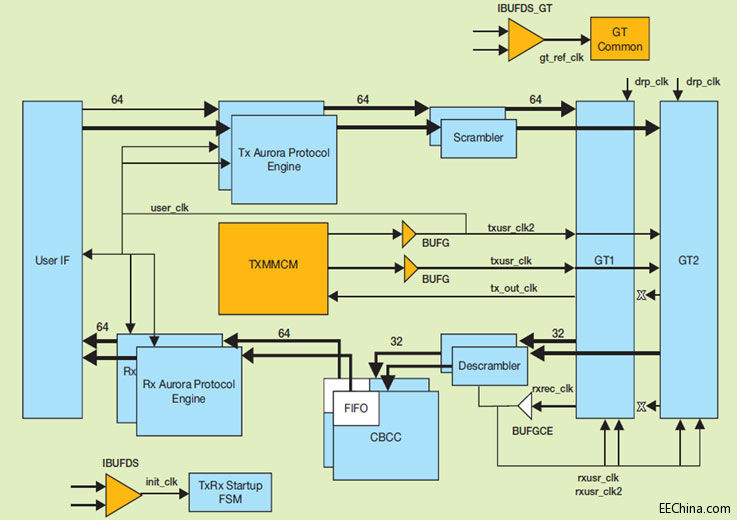

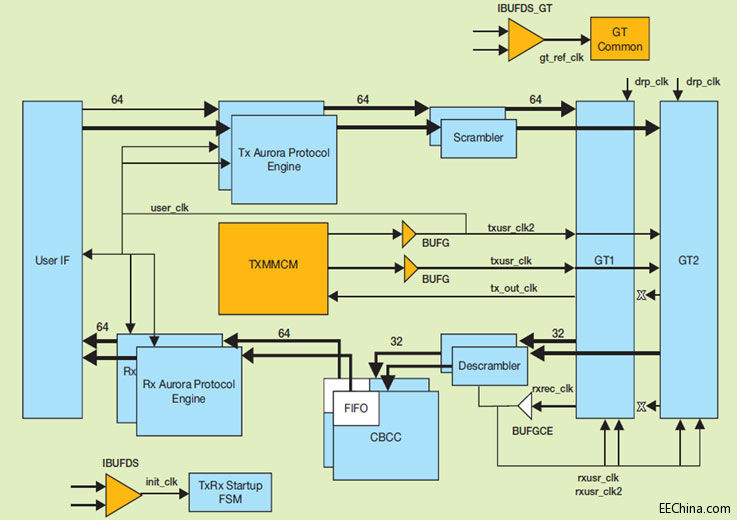

图 1 是 Aurora 64b66b 内核的典型方框图。突出显示部分为时钟资源,例如混合模式时钟管理器 (MMCM)、BUFG 和 IBUFDS;以及千兆位收发器 (GT) 资源,例如 GT common 和 GT 通道,在图中标示为赛灵思 7 系列器件双路设计的 GT1 和 GT2。

图 1–用橙色突出显示的 Aurora 64b66b 内核中的共享资源

就像 Kintex-7 FPGA KC705 评估套件那样,典型 16 路 Aurora 64b66b 内核所需的时钟和 GT 资源已在表 1 中列出。

FPGA 中的时钟和 GT 资源取决于所选的器件和封装类型。多个 IP 内核经常要求在系统级使用资源。因此,必须要优化利用这些宝贵资源,以降低系统成本和功耗。

IPI 工具将内核作为顶层模块进行可视化;标准接口之间的连接现在更加直观和智能化,在有些情况下甚至可实现自动化。正确的设计规则检查被置入工具以及 IP 周围,以确保突出显示错误连接,以便设计人员在设计输入时发现它们。该工具能自动生成顶层封装文件以及调用正确的引脚级 I/O 要求,因此可帮助系统设计人员提高生产力。如果您已经设计了定制子模块,可以考虑

AURORA 资源共享

因为多款基于 GT 的赛灵思内核都支持共享逻辑特性,Aurora 内核可配置为“内核(主机)中的共享逻辑”或“实例设计(从机)中的共享逻辑”。当在系统级进行实例化时,两种配置的组合可支持在主机与从机之间共享时钟和 GT 资源。

对于需要使用共享逻辑特性的应用,手动建立多个 IP 之间的连接有可能会产生错误,并增加总的设计输入时间。借助工具进行设计输入是一种解决该问题的方法,而赛灵思的 IP Integrator 能游刃有余地完成这个任务。

依照赛灵思应用指南 1168,“针对 Vivado IP Integrator 打包定制 AXI IP”(XAPP1168) 对设计进行打包,并在 IPI 中使用子模块。

Aurora 的共享逻辑特性不仅可让用户在多个实例中共享资源,而且还能在相同 GT Quad 封装中使用 GT 通道,无需编辑 GT common、PLL、时钟以及相关模块。唯一的约束是“共享”内核的线路速率应该相同(允许存在谐波,只要您能接受其对时钟资源的影响即可)。

典型的共享逻辑设计在一个 Guad 中包含一个主机以及一个或多个从机实例。与大多数其它通信 IP 不同,Aurora不仅限于单个 Guad 共享。Aurora 内核的共享逻辑定义可扩展用于任意数量的受支持信道。

下面的一些实例展示了 Aurora 共享逻辑特性的应用情况。

多个单信道设计

单部 FPGA 中的多个单信道设计与多信道设计的不同之处在于前者需要通道绑定。我们可以直观地看到多个单信道设计所需的资源会在系统级线性增加。让我们考虑不同情况,并了解共享逻辑特性如何在每种情况下起作用。

我们首先从包含四条单信道的设计开始。通过实例化四个单信道 Aurora 内核,您可直接构建这类设计。如果我们实际执行该实现方案,会发现每个 Aurora 设计都有一个 GT common 实例;因此,该设计的布局和资源利用会遍及四个 GT Guad。这种方法消耗太多资源,不一定总是可行。

表 1–Kintex-7 FPGA KC705 评估套件上的时钟和 GT 资源利用率

作者:

K Krishna Deepak

赛灵思高级设计工程师

kde@xilinx.com

Dinesh Kumar

赛灵思高级工程经理

dineshk@xilinx.com

Jayaram PVSS

赛灵思高级工程经理

jayaram@xilinx.com

Ketan Mehta

赛灵思高级IP产品经理

ketanm@xilinx.com

客户在必须由单个 FPGA 实现的大型设计中使用多个知识产权 (IP) 实例时,面临的主要挑战之一是如何在整个系统中有效共享资源。赛灵思 Aurora 串行通信内核的共享逻辑特性使用户可以在多个实例中共享资源。Vivado 设计套件中的 IP Integrator 工具对于充分利用共享资源至关重要。

电子行业正快速转向高速串行连接解决方案,同时逐渐舍弃并行通信标准。行业标准串行协议具有固定的线路速率和确定的信道宽度,有时无法充分利用千兆位串行收发器的功能。

Aurora 是赛灵思的高速串行通信协议,一直在行业内非常受欢迎。当某些应用领域中的行业协议实现过程太过复杂或者太耗费资源时,Aurora 通常是首选方案。Aurora 能实现低成本、高数据速率的可扩展IP解决方案,可用于灵活地构建高速串行数据通道。

需要同时对线路速率和通道宽度进行扩展的高性能系统和应用正在期待将 Aurora 作为解决方案。此外,Aurora 还被应用于 ASIC 设计以及包含多块 FPGA 的系统(用背板传输千兆位的数据)中。Aurora 采用简单的帧结构,并具有协议扩展流量控制功能,可用于封装现有协议的数据。它的电气要求与产品设备兼容。赛灵思提供 Aurora 64b66b 和 Aurora 8b10b 内核,作为 Vivado 设计套件 IP 目录的一部分。

Vivado IP Integrator (IPI) 是用于复杂多核系统中资源优化的重要工具。就这一点而言,IPI 将帮助您充分利用 Aurora 64b66b 和 Aurora 8b10b 内核中的共享资源,尤其是“共享逻辑”特性。为了方便起见,我们重点介绍 Aurora 64b66b IP,同时您要了解类似技术也适用于 Aurora 8b10b 内核。

AURORA 的共享资源一览

图 1 是 Aurora 64b66b 内核的典型方框图。突出显示部分为时钟资源,例如混合模式时钟管理器 (MMCM)、BUFG 和 IBUFDS;以及千兆位收发器 (GT) 资源,例如 GT common 和 GT 通道,在图中标示为赛灵思 7 系列器件双路设计的 GT1 和 GT2。

图 1–用橙色突出显示的 Aurora 64b66b 内核中的共享资源

就像 Kintex-7 FPGA KC705 评估套件那样,典型 16 路 Aurora 64b66b 内核所需的时钟和 GT 资源已在表 1 中列出。

FPGA 中的时钟和 GT 资源取决于所选的器件和封装类型。多个 IP 内核经常要求在系统级使用资源。因此,必须要优化利用这些宝贵资源,以降低系统成本和功耗。

IPI 工具将内核作为顶层模块进行可视化;标准接口之间的连接现在更加直观和智能化,在有些情况下甚至可实现自动化。正确的设计规则检查被置入工具以及 IP 周围,以确保突出显示错误连接,以便设计人员在设计输入时发现它们。该工具能自动生成顶层封装文件以及调用正确的引脚级 I/O 要求,因此可帮助系统设计人员提高生产力。如果您已经设计了定制子模块,可以考虑

AURORA 资源共享

因为多款基于 GT 的赛灵思内核都支持共享逻辑特性,Aurora 内核可配置为“内核(主机)中的共享逻辑”或“实例设计(从机)中的共享逻辑”。当在系统级进行实例化时,两种配置的组合可支持在主机与从机之间共享时钟和 GT 资源。

对于需要使用共享逻辑特性的应用,手动建立多个 IP 之间的连接有可能会产生错误,并增加总的设计输入时间。借助工具进行设计输入是一种解决该问题的方法,而赛灵思的 IP Integrator 能游刃有余地完成这个任务。

依照赛灵思应用指南 1168,“针对 Vivado IP Integrator 打包定制 AXI IP”(XAPP1168) 对设计进行打包,并在 IPI 中使用子模块。

Aurora 的共享逻辑特性不仅可让用户在多个实例中共享资源,而且还能在相同 GT Quad 封装中使用 GT 通道,无需编辑 GT common、PLL、时钟以及相关模块。唯一的约束是“共享”内核的线路速率应该相同(允许存在谐波,只要您能接受其对时钟资源的影响即可)。

典型的共享逻辑设计在一个 Guad 中包含一个主机以及一个或多个从机实例。与大多数其它通信 IP 不同,Aurora不仅限于单个 Guad 共享。Aurora 内核的共享逻辑定义可扩展用于任意数量的受支持信道。

下面的一些实例展示了 Aurora 共享逻辑特性的应用情况。

多个单信道设计

单部 FPGA 中的多个单信道设计与多信道设计的不同之处在于前者需要通道绑定。我们可以直观地看到多个单信道设计所需的资源会在系统级线性增加。让我们考虑不同情况,并了解共享逻辑特性如何在每种情况下起作用。

我们首先从包含四条单信道的设计开始。通过实例化四个单信道 Aurora 内核,您可直接构建这类设计。如果我们实际执行该实现方案,会发现每个 Aurora 设计都有一个 GT common 实例;因此,该设计的布局和资源利用会遍及四个 GT Guad。这种方法消耗太多资源,不一定总是可行。

表 1–Kintex-7 FPGA KC705 评估套件上的时钟和 GT 资源利用率

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)