采用三栅极技术FPGA的突破性优势

时间:12-07

来源:互联网

点击:

量产中的三栅极器件

尽管对三栅极晶体管优点的研究和了解已经持续了一段时间,但其接受与实现的最终动力将是技术与可制造性,以及性价比。

极小几何尺寸下(40nm、28nm、22nm或20nm乃至更低)的先进半导体制造需要相当的研发开支,从而将该技术限制在少数有数十亿美元资本开支能力的公司。于是,只有少数公司能够从已知的3D晶体管技术优势中获利。Intel公司是唯一一家已在22nm下完成这种设计与制造技术转换的企业,可以在量产水平上,提供有关三栅极晶体管的全部成熟及可制造性的数据。到2013年第一季度时,该数据已经包括了1亿单位的基于三栅极晶体管的产品。

为了获得该技术在制造与设计方面的成熟度,针对3D栅极结构的多个问题与特性已经被认可并予以解决。这些包括对传统平面设计中未予模型化的新的寄生电容值的建模,布局的依赖效应,以及用现有光刻设备来生成近距离翘片的双模技术。

电子设计自动化(EDA)社区也是半导体设计者了解FinFET与三栅极设计技术的重要场合。2013年,Cadence与Synopsys等很多公司都做了大量的宣传及用户教育工作,中心内容是三栅极的影响,以及未来半导体产品设计中的灵活性。

对FPGA及其他半导体器件性能的影响

对FPGA电子产品的设计者而言,三栅极技术的主要优势是:摩尔定律持续适用于晶体管密度、性能、功耗以及单位晶体管成本的稳步改进。它支撑着消费电子行业、计算平台开发、软件复杂性的提高、存储器与存储容量的增长、移动设备创意与发展,以及商务自动化与生产效率。

此外,该技术极大改善了对半导体静态与动态功耗的控制。对于FPGA用户,在当前的竞争性设计结点上,可编程逻辑推进到14nm技术甚至更低,就能具备较ASIC与ASSP设计方案更强大的竞争力,而在可编程性、性能、灵活性、开放计算语言(OpenCL)软件设计输入,以及DSP、收发器、硬化处理器和可配置I/O的集成方面,甚至有着更明显的优势。

Intel公司根据三栅极技术在微处理器产品中量产的情况,向自己的普通投资者社区说明了他们能获得的明确利益。该数据包括:从32nm平面转到22nm三栅极设计时,单管动态功耗减少了50%以上;与32nm平面设计相比,22nm三栅极的缺陷密度曲线得到了改善;而从32nm平面转到22nm三栅极设计时,SEU发生率降低至1/4至1/10。

Intel在晶体管技术方面的领先地位

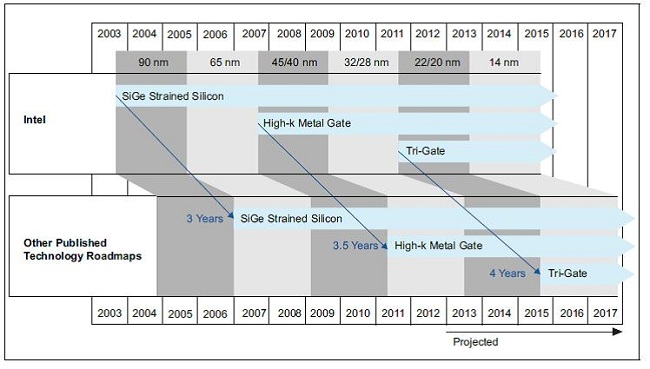

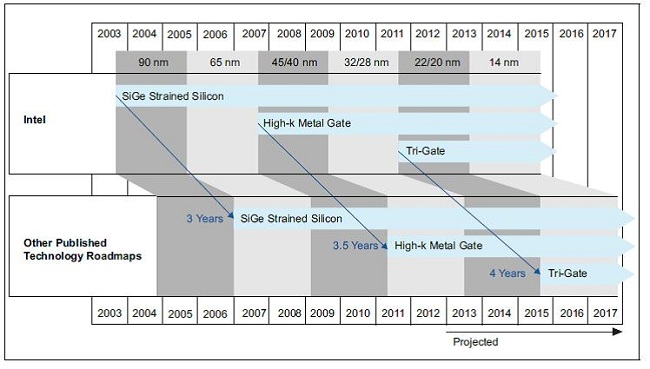

在包括Intel的开发者论坛以及投资者的研讨会在内的多个公开论坛上,Intel都以一系列与摩尔定律同步的进展表明了自己已有的技术领导地位。如图3所示,Intel在应变硅与高K金属栅极技术的量产实现方面,拥有多年制造领先地位。对于3D三栅极晶体管技术,Intel于2011年将22nm的三栅极技术投入生产,预计领先时间多达四年。

图3:Intel在晶体管技术方面的领先地位

Intel公司CEO Paul Otellini在2013年4月16日的业绩发布会上表示:“在(2013年)一季度,我们交付了第1亿片采用我们革命性3D晶体管技术的22nm(三栅极)处理器,而业内其他人还在努力交付自己的第一片产品。”

Intel公司14nm技术的推出将获得另一个领先优势,这可以回溯到它对工艺与微架构的极著名的“Tick-Tock(工艺年-构架年)”战略。产品推出的“Tick”周期要依赖于CPU产品中微架构变动的实现,其后是半导体工艺制造几何尺寸缩减“Tock”周期。Intel在从22nm转到14nm时坚定地致力于全工艺尺度微缩;而其他制造商开发的半导体技术工艺则尚不明确,他们的工艺路线图不知是否包括了工艺微缩的优势。

从Altera的FPGA获得三栅极技术的好处

只有Altera 14nm工艺高密度高性能FPGA的用户,才可能充分利用Intel三栅极技术的显著优势。这是本文所述两家公司专有制造合作关系的结果。

三栅极硅技术的巨大优势将使Altera能够提供难以想象的高性能FPGA与SoC产品。这包括与其他高端FPGA相比,其核心性能实现了历史性的翻番,将FPGA带入GHz的性能水平。通过工艺、架构与软件的共同进步,整体的静态与动态功耗值都将减少70%。

虽然Intel公司尚未公开14nm制造工艺的详情以及日程表,但Altera用户现在就可以着手将三栅极技术的高性能与低功耗优势用于FPGA设计中。可以开始设计的是Arria 10的20nm FPGA器件组合。然后,用户可以使用管脚对管脚(pin-for-pin)式设计迁移路径,从Arria 10 FPGA与SoC产品迁移到Stratix 10 FPGA与SoC产品(一旦可用)。

这样,无论您是FPGA用户还是系统架构师,都可以着手设计出能够同时兼容Arria 10和Stratix 10系列的产品,而尽量减少变更、修改和再工程化的工作量。于是,您就能用20nm工艺技术和降功耗技术,将最高性能和最低功耗的FPGA推向市场;然后,再利用Intel公司14nm三栅极制造工艺,就可以将这些相同产品推进到以往不可想象的性能与功率效率。

尽管对三栅极晶体管优点的研究和了解已经持续了一段时间,但其接受与实现的最终动力将是技术与可制造性,以及性价比。

极小几何尺寸下(40nm、28nm、22nm或20nm乃至更低)的先进半导体制造需要相当的研发开支,从而将该技术限制在少数有数十亿美元资本开支能力的公司。于是,只有少数公司能够从已知的3D晶体管技术优势中获利。Intel公司是唯一一家已在22nm下完成这种设计与制造技术转换的企业,可以在量产水平上,提供有关三栅极晶体管的全部成熟及可制造性的数据。到2013年第一季度时,该数据已经包括了1亿单位的基于三栅极晶体管的产品。

为了获得该技术在制造与设计方面的成熟度,针对3D栅极结构的多个问题与特性已经被认可并予以解决。这些包括对传统平面设计中未予模型化的新的寄生电容值的建模,布局的依赖效应,以及用现有光刻设备来生成近距离翘片的双模技术。

电子设计自动化(EDA)社区也是半导体设计者了解FinFET与三栅极设计技术的重要场合。2013年,Cadence与Synopsys等很多公司都做了大量的宣传及用户教育工作,中心内容是三栅极的影响,以及未来半导体产品设计中的灵活性。

对FPGA及其他半导体器件性能的影响

对FPGA电子产品的设计者而言,三栅极技术的主要优势是:摩尔定律持续适用于晶体管密度、性能、功耗以及单位晶体管成本的稳步改进。它支撑着消费电子行业、计算平台开发、软件复杂性的提高、存储器与存储容量的增长、移动设备创意与发展,以及商务自动化与生产效率。

此外,该技术极大改善了对半导体静态与动态功耗的控制。对于FPGA用户,在当前的竞争性设计结点上,可编程逻辑推进到14nm技术甚至更低,就能具备较ASIC与ASSP设计方案更强大的竞争力,而在可编程性、性能、灵活性、开放计算语言(OpenCL)软件设计输入,以及DSP、收发器、硬化处理器和可配置I/O的集成方面,甚至有着更明显的优势。

Intel公司根据三栅极技术在微处理器产品中量产的情况,向自己的普通投资者社区说明了他们能获得的明确利益。该数据包括:从32nm平面转到22nm三栅极设计时,单管动态功耗减少了50%以上;与32nm平面设计相比,22nm三栅极的缺陷密度曲线得到了改善;而从32nm平面转到22nm三栅极设计时,SEU发生率降低至1/4至1/10。

Intel在晶体管技术方面的领先地位

在包括Intel的开发者论坛以及投资者的研讨会在内的多个公开论坛上,Intel都以一系列与摩尔定律同步的进展表明了自己已有的技术领导地位。如图3所示,Intel在应变硅与高K金属栅极技术的量产实现方面,拥有多年制造领先地位。对于3D三栅极晶体管技术,Intel于2011年将22nm的三栅极技术投入生产,预计领先时间多达四年。

图3:Intel在晶体管技术方面的领先地位

Intel公司CEO Paul Otellini在2013年4月16日的业绩发布会上表示:“在(2013年)一季度,我们交付了第1亿片采用我们革命性3D晶体管技术的22nm(三栅极)处理器,而业内其他人还在努力交付自己的第一片产品。”

Intel公司14nm技术的推出将获得另一个领先优势,这可以回溯到它对工艺与微架构的极著名的“Tick-Tock(工艺年-构架年)”战略。产品推出的“Tick”周期要依赖于CPU产品中微架构变动的实现,其后是半导体工艺制造几何尺寸缩减“Tock”周期。Intel在从22nm转到14nm时坚定地致力于全工艺尺度微缩;而其他制造商开发的半导体技术工艺则尚不明确,他们的工艺路线图不知是否包括了工艺微缩的优势。

从Altera的FPGA获得三栅极技术的好处

只有Altera 14nm工艺高密度高性能FPGA的用户,才可能充分利用Intel三栅极技术的显著优势。这是本文所述两家公司专有制造合作关系的结果。

三栅极硅技术的巨大优势将使Altera能够提供难以想象的高性能FPGA与SoC产品。这包括与其他高端FPGA相比,其核心性能实现了历史性的翻番,将FPGA带入GHz的性能水平。通过工艺、架构与软件的共同进步,整体的静态与动态功耗值都将减少70%。

虽然Intel公司尚未公开14nm制造工艺的详情以及日程表,但Altera用户现在就可以着手将三栅极技术的高性能与低功耗优势用于FPGA设计中。可以开始设计的是Arria 10的20nm FPGA器件组合。然后,用户可以使用管脚对管脚(pin-for-pin)式设计迁移路径,从Arria 10 FPGA与SoC产品迁移到Stratix 10 FPGA与SoC产品(一旦可用)。

这样,无论您是FPGA用户还是系统架构师,都可以着手设计出能够同时兼容Arria 10和Stratix 10系列的产品,而尽量减少变更、修改和再工程化的工作量。于是,您就能用20nm工艺技术和降功耗技术,将最高性能和最低功耗的FPGA推向市场;然后,再利用Intel公司14nm三栅极制造工艺,就可以将这些相同产品推进到以往不可想象的性能与功率效率。

Altera FPGA 半导体 电路 MOSFET 电流 电压 电容 电子 自动化 EDA Cadence DSP 收发器 SoC 相关文章:

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 智能命令行设计及其在 SOPC 系统中的应用(08-14)

- 我的FPGA学习历程(05-23)

- 在FPGA中实现源同步LVDS接收正确字对齐(05-01)

- Altera FPGA下载配置(11-11)