FPGA系统设计的仿真验证之:SDRAM读写控制的实现与Modelsim仿真

时间:11-24

来源:互联网

点击:

7.6 典型实例13:SDRAM读写控制的实现与Modelsim仿真

7.6.1 实例的内容及目标

1.实例的主要内容

本节旨在通过分析SDRAM控制器,介绍了SDRAM的基本工作模式。最后使用Modelsim对读写控制器进行仿真,帮助读者进一步了解一个真实的器件模块是如何进行Modelsim仿真的。

2.实例目标

通过本实例,读者应达到下面的目标。

· 了解SDRAM存储器的工作模式。

· 熟悉Modelsim仿真的基本流程。

· 可独立使用Modelsim仿真新工程。

7.6.2 SDRAM简介

在高速实时或者非实时信号处理系统当中,常常使用大容量存储器实现数据缓存。而大容量存储器的控制与使用是整个系统实现过程中的重点和难点之一。

SDRAM(同步动态随即访问存储器)具有价格低廉、精密度高、读写速度快等优点,从而成为数据缓存器的首选存储介质。但是SDRAM的结构与SRAM有很大的差异,其控制时序和机制也比较复杂,这就限制了SDRAM的使用范围。

下面我们首先对SDRAM进行简单介绍。

1.SDRAM信号

SDRAM器件的信号可以分为控制、地址和数据信号3类,具体定义如表7.2所示。

表7.2 SDRAM信号

信 号 名信 号 类 型信 号 描 述

CS输入Chip Enable,使能

CLK输入Clock,时钟

CKE输入Clock Enable,时钟使能

RAS输入Row Address Strobe,行地址选通

续表

信 号 名信 号 类 型信 号 描 述

CAS输入Column Address Strobe,列地址选通

WE输入Write Enable,写使能

DQML、DQMH输入Data Mask for Lower,Upper Bytes,高低字节屏蔽

BA输入Bank Address,Bank地址

A[0:10]输入Address,地址

DQ[0:15]双向Data,数据

2.SDRAM工作特性

通常一个SDRAM 中包含几个Bank,每个Bank的存储单元是按行和列寻址的。由于这种特殊的存储结构,SDRAM有以下几个工作特性。

(1)SDRAM 的初始化。

SDRAM 在上电100~200μs 后,必须由一个初始化进程来配置SDRAM的模式寄存器,模式寄存器的值决定着SDRAM 的工作模式。

(2)访问存储单元。

为减少I/O 引脚数量,SDRAM 复用了地址线。所以在读写SDRAM 时,先由ACTIVE 命令激活要读写的Bank,并锁存行地址,然后在读写指令有效时锁存列地址。一旦Bank被激活后只有执行一次预充命令后才能再次激活同一Bank。

(3)刷新和预充。

为了提高存储密度, SDRAM 采用硅片电容存储数据,电容总是倾向于放电,因此必须有定时的刷新周期以避免数据丢失。刷新周期可由(最小刷新周期÷时钟周期)计算获得。对Bank预充电或者关闭已激活的Bank,可预充特定Bank 也可同时作用于所有Bank,A10、BA0和BA1用于选择Bank。

(4)操作控制。

SDRAM 的具体控制命令由一些专用控制引脚和地址线辅助完成。CS、RAS、CAS 和WR 在时钟上升沿的状态决定具体操作动作,地址线和Bank选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM 操作指令比较多,不像SRAM 一样只有简单的读写,具体操作指令如表7.3所示。

表7.3 SDRAM命令真值表

功 能命 令 字CSRASCASWEBAA10A[0:9]

取消器件选择DSELHXXXXXX

无操作NOPLHHHXXX

读操作READLHLHVLV

读等待/自动预充电READAPLHLHVHV

续表

功 能命 令 字CSRASCASWEBAA10A[0:9]

写操作WRITELHLLVLV

写等待/自动预充电WRITEAPLHLLVHV

Bank激活ACTLLHHVVV

对指定Bank预充电PRELLHLVLX

对所有Bank预充电PALLLLHLXHX

自动刷新CBRLLLHXXX

加载模式寄存器MRSLLLLVVV

由表7.3可以看到,虽然SDRAM的容量大、速度快,但是存在存储操作困难的问题。一般的解决方案有两种,一是直接控制SDRAM的读写时序实现数据的存储和读取,二是编写一个SDRAM的读写控制器,将SDRAM的读写简化成SRAM形式,通过几个命令完成SDRAM的读写。

3.SDRAM读写控制器

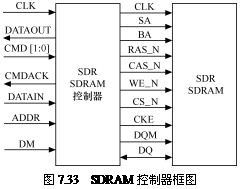

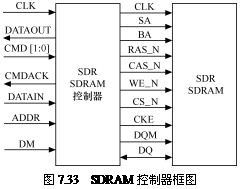

Xilinx、Altera、Lattice等较大的FPGA制造厂商都编写了自己的SDRAM接口控制器。读者可以到官方网站去申请相关的控制器源代码。下面简单介绍其中一种,如图7.33所示是该SDRAM控制器总体设计框图和外部接口信号。

在图7.33中,控制器右端接口信号均为直接与SDRAM 对应管脚相连的信号,在表7.2中已做介绍,不再重复。

控制器左端的接口信号为与FPGA 相连的系统控制接口信号,定义如下。

· CLK:系统时钟信号。

· ADDR:系统给出的SDRAM 地址信号。

· DATAIN:系统用于写入SDRAM 的数据信号。

· DATAOUT:系统用于从SDRAM读出的数据信号。

· CMD[1:0]、CMDACK:系统和控制器的命令交互信号,参见表7.3。

· DM:数据Mask信号。

一般来说,SDRAM的读写控制时序可以分为初始化、写寄存器、自动刷新、突发模式读、突发模式写、整页读以及整页写等主要操作。具体的时序图可以查阅相关的器件数据手册,这里不再列出。

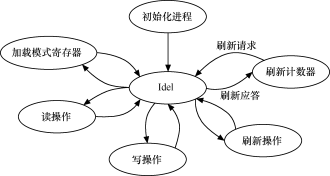

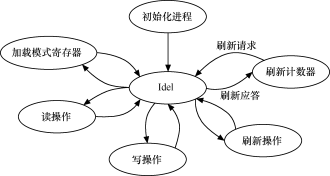

SDRAM的读写控制也可以由如图7.34所示的读写状态机表示。

在FPGA中,实现如图7.34所示的状态机,再利用已有的SDR SDRAM控制器即可实现对SDRAM器件的控制。

图7.34 SDRAM读写状态机

7.6.3 SDRAM控制器的Modelsim仿真

(1)打开ModelSim软件。

(2)创建工程。

如图7.35所示,在Modelsim中创建新工程,并设置工程的相关属性。

图7.35 创建工程

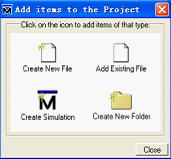

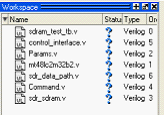

(3)添加设计输入。

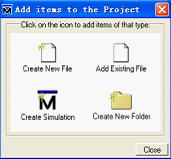

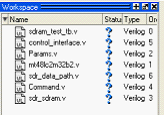

若要创建新的文件就选择【Create New File】图标,若要添加已经存在的文件就选择【Add Existing File】图标,如图7.36所示。本实例中使用已经存在的SDRAM控制器源文件作为设计输入,添加后,在Workspace浏览器中可以看到如图7.37的设计输入列表。

图7.36 添加设计输入 图7.37 SDRAM设计输入列表

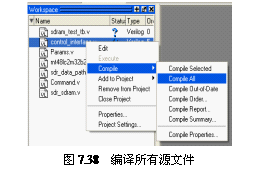

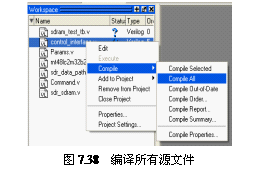

(4)编译设计输入。

如图7.38所示,在任意一个源文件上单击右键,选择“Compile”/“Compile All”,对所有的源文件进行编译。

编译后,若有错误,Modelsim会在信息栏中显示出来。这时只要双击该错误,ModelSim就会自动打开该错误所在的文件,并定位到出现错误所在的位置附近。若编译正确通过,源文件后面的蓝色问号就替换成为绿色的对号,如图7.39所示。

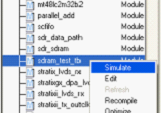

(5)仿真。

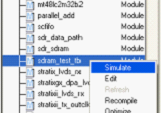

在Workspace浏览器中选择“Library”复选页,单击Work左边的小加号。在弹出的子菜单里面找到仿真模块“sdram_test_tb”。双击或右键选择“Simulate”选项,ModelSim就会自动运行仿真,如图7.40所示。

图7.39 编译正确通过 图7.40 仿真

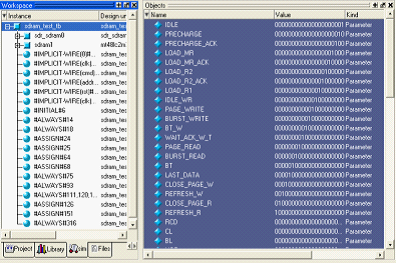

(6)观察波形。

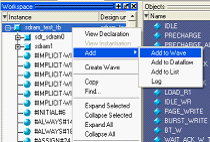

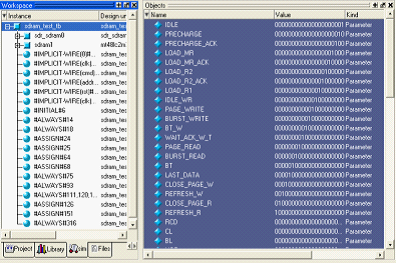

在Workspace浏览器中选择“Sim”复选页,可以看到仿真模块的实例列表,如图7.41所示。

图7.41 仿真模块实例列表

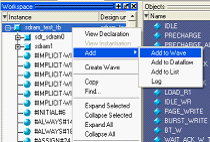

如图7.42所示,右键单击顶层测试模块,选择“Add”/“Add to Wave”选项,将该仿真模块的所有实例添加至波形观察器中。

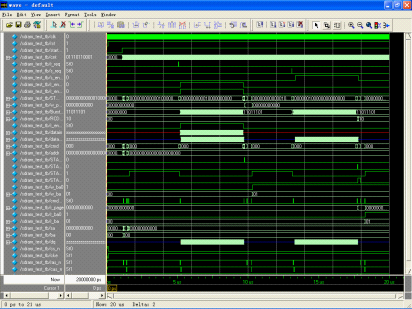

添加后,ModelSim将会自动打开一个波形观察器,并将顶层测试模块的所有寄存器和接口添加进去。回到ModelSim的界面,在命令输入窗口中键入“run 20us”,开始执行仿真,如图7.43所示。

图7.42 添加实例至波形观察器 图7.43 执行仿真

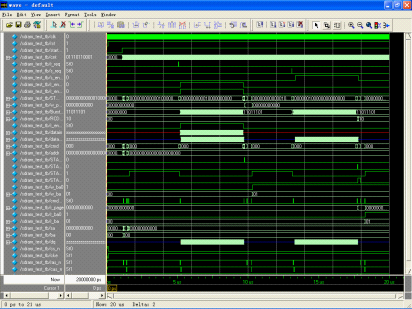

执行仿真后,经过相应的仿真时间,就可以在波形观察器中看见如图7.44所示的仿真结果。这个就是通过利用已有的SDRAM控制器及SDRAM器件模型,由用户编写对SDRAM控制器的状态机控制后得到的仿真结果。

图7.44 SDRAM控制器仿真结果

7.6.4 小结

本节对数字系统中常用的存储器SDRAM做了初步的介绍,并在Modelsim中实现了对SDRAM控制器的仿真。通过这个实例,读者能够掌握分立器件是如何与FPGA逻辑实现Modelsim联合仿真的。

在大型的系统设计中,在系统硬件实现前对系统进行仿真是非常必要的。而这个仿真又不仅仅局限在FPGA等可编程逻辑器件内部,与之相关的分立器件也是系统仿真的重要组成部分。因此掌握分立器件的联合仿真是一个非常重要的技能。

7.6.1 实例的内容及目标

1.实例的主要内容

本节旨在通过分析SDRAM控制器,介绍了SDRAM的基本工作模式。最后使用Modelsim对读写控制器进行仿真,帮助读者进一步了解一个真实的器件模块是如何进行Modelsim仿真的。

2.实例目标

通过本实例,读者应达到下面的目标。

· 了解SDRAM存储器的工作模式。

· 熟悉Modelsim仿真的基本流程。

· 可独立使用Modelsim仿真新工程。

7.6.2 SDRAM简介

在高速实时或者非实时信号处理系统当中,常常使用大容量存储器实现数据缓存。而大容量存储器的控制与使用是整个系统实现过程中的重点和难点之一。

SDRAM(同步动态随即访问存储器)具有价格低廉、精密度高、读写速度快等优点,从而成为数据缓存器的首选存储介质。但是SDRAM的结构与SRAM有很大的差异,其控制时序和机制也比较复杂,这就限制了SDRAM的使用范围。

下面我们首先对SDRAM进行简单介绍。

1.SDRAM信号

SDRAM器件的信号可以分为控制、地址和数据信号3类,具体定义如表7.2所示。

表7.2 SDRAM信号

信 号 名信 号 类 型信 号 描 述

CS输入Chip Enable,使能

CLK输入Clock,时钟

CKE输入Clock Enable,时钟使能

RAS输入Row Address Strobe,行地址选通

续表

信 号 名信 号 类 型信 号 描 述

CAS输入Column Address Strobe,列地址选通

WE输入Write Enable,写使能

DQML、DQMH输入Data Mask for Lower,Upper Bytes,高低字节屏蔽

BA输入Bank Address,Bank地址

A[0:10]输入Address,地址

DQ[0:15]双向Data,数据

2.SDRAM工作特性

通常一个SDRAM 中包含几个Bank,每个Bank的存储单元是按行和列寻址的。由于这种特殊的存储结构,SDRAM有以下几个工作特性。

(1)SDRAM 的初始化。

SDRAM 在上电100~200μs 后,必须由一个初始化进程来配置SDRAM的模式寄存器,模式寄存器的值决定着SDRAM 的工作模式。

(2)访问存储单元。

为减少I/O 引脚数量,SDRAM 复用了地址线。所以在读写SDRAM 时,先由ACTIVE 命令激活要读写的Bank,并锁存行地址,然后在读写指令有效时锁存列地址。一旦Bank被激活后只有执行一次预充命令后才能再次激活同一Bank。

(3)刷新和预充。

为了提高存储密度, SDRAM 采用硅片电容存储数据,电容总是倾向于放电,因此必须有定时的刷新周期以避免数据丢失。刷新周期可由(最小刷新周期÷时钟周期)计算获得。对Bank预充电或者关闭已激活的Bank,可预充特定Bank 也可同时作用于所有Bank,A10、BA0和BA1用于选择Bank。

(4)操作控制。

SDRAM 的具体控制命令由一些专用控制引脚和地址线辅助完成。CS、RAS、CAS 和WR 在时钟上升沿的状态决定具体操作动作,地址线和Bank选择控制线在部分操作动作中作为辅助参数输入。

由于特殊的存储结构,SDRAM 操作指令比较多,不像SRAM 一样只有简单的读写,具体操作指令如表7.3所示。

表7.3 SDRAM命令真值表

功 能命 令 字CSRASCASWEBAA10A[0:9]

取消器件选择DSELHXXXXXX

无操作NOPLHHHXXX

读操作READLHLHVLV

读等待/自动预充电READAPLHLHVHV

续表

功 能命 令 字CSRASCASWEBAA10A[0:9]

写操作WRITELHLLVLV

写等待/自动预充电WRITEAPLHLLVHV

Bank激活ACTLLHHVVV

对指定Bank预充电PRELLHLVLX

对所有Bank预充电PALLLLHLXHX

自动刷新CBRLLLHXXX

加载模式寄存器MRSLLLLVVV

由表7.3可以看到,虽然SDRAM的容量大、速度快,但是存在存储操作困难的问题。一般的解决方案有两种,一是直接控制SDRAM的读写时序实现数据的存储和读取,二是编写一个SDRAM的读写控制器,将SDRAM的读写简化成SRAM形式,通过几个命令完成SDRAM的读写。

3.SDRAM读写控制器

Xilinx、Altera、Lattice等较大的FPGA制造厂商都编写了自己的SDRAM接口控制器。读者可以到官方网站去申请相关的控制器源代码。下面简单介绍其中一种,如图7.33所示是该SDRAM控制器总体设计框图和外部接口信号。

在图7.33中,控制器右端接口信号均为直接与SDRAM 对应管脚相连的信号,在表7.2中已做介绍,不再重复。

控制器左端的接口信号为与FPGA 相连的系统控制接口信号,定义如下。

· CLK:系统时钟信号。

· ADDR:系统给出的SDRAM 地址信号。

· DATAIN:系统用于写入SDRAM 的数据信号。

· DATAOUT:系统用于从SDRAM读出的数据信号。

· CMD[1:0]、CMDACK:系统和控制器的命令交互信号,参见表7.3。

· DM:数据Mask信号。

一般来说,SDRAM的读写控制时序可以分为初始化、写寄存器、自动刷新、突发模式读、突发模式写、整页读以及整页写等主要操作。具体的时序图可以查阅相关的器件数据手册,这里不再列出。

SDRAM的读写控制也可以由如图7.34所示的读写状态机表示。

在FPGA中,实现如图7.34所示的状态机,再利用已有的SDR SDRAM控制器即可实现对SDRAM器件的控制。

图7.34 SDRAM读写状态机

7.6.3 SDRAM控制器的Modelsim仿真

(1)打开ModelSim软件。

(2)创建工程。

如图7.35所示,在Modelsim中创建新工程,并设置工程的相关属性。

图7.35 创建工程

(3)添加设计输入。

若要创建新的文件就选择【Create New File】图标,若要添加已经存在的文件就选择【Add Existing File】图标,如图7.36所示。本实例中使用已经存在的SDRAM控制器源文件作为设计输入,添加后,在Workspace浏览器中可以看到如图7.37的设计输入列表。

图7.36 添加设计输入 图7.37 SDRAM设计输入列表

(4)编译设计输入。

如图7.38所示,在任意一个源文件上单击右键,选择“Compile”/“Compile All”,对所有的源文件进行编译。

编译后,若有错误,Modelsim会在信息栏中显示出来。这时只要双击该错误,ModelSim就会自动打开该错误所在的文件,并定位到出现错误所在的位置附近。若编译正确通过,源文件后面的蓝色问号就替换成为绿色的对号,如图7.39所示。

(5)仿真。

在Workspace浏览器中选择“Library”复选页,单击Work左边的小加号。在弹出的子菜单里面找到仿真模块“sdram_test_tb”。双击或右键选择“Simulate”选项,ModelSim就会自动运行仿真,如图7.40所示。

图7.39 编译正确通过 图7.40 仿真

(6)观察波形。

在Workspace浏览器中选择“Sim”复选页,可以看到仿真模块的实例列表,如图7.41所示。

图7.41 仿真模块实例列表

如图7.42所示,右键单击顶层测试模块,选择“Add”/“Add to Wave”选项,将该仿真模块的所有实例添加至波形观察器中。

添加后,ModelSim将会自动打开一个波形观察器,并将顶层测试模块的所有寄存器和接口添加进去。回到ModelSim的界面,在命令输入窗口中键入“run 20us”,开始执行仿真,如图7.43所示。

图7.42 添加实例至波形观察器 图7.43 执行仿真

执行仿真后,经过相应的仿真时间,就可以在波形观察器中看见如图7.44所示的仿真结果。这个就是通过利用已有的SDRAM控制器及SDRAM器件模型,由用户编写对SDRAM控制器的状态机控制后得到的仿真结果。

图7.44 SDRAM控制器仿真结果

7.6.4 小结

本节对数字系统中常用的存储器SDRAM做了初步的介绍,并在Modelsim中实现了对SDRAM控制器的仿真。通过这个实例,读者能够掌握分立器件是如何与FPGA逻辑实现Modelsim联合仿真的。

在大型的系统设计中,在系统硬件实现前对系统进行仿真是非常必要的。而这个仿真又不仅仅局限在FPGA等可编程逻辑器件内部,与之相关的分立器件也是系统仿真的重要组成部分。因此掌握分立器件的联合仿真是一个非常重要的技能。

仿真 电容 CSR Xilinx Altera FPGA DAC ModelSim 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)