Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势

时间:04-13

来源:互联网

点击:

16nm ZYNQ ULTRASCALE MPSOC测试标准

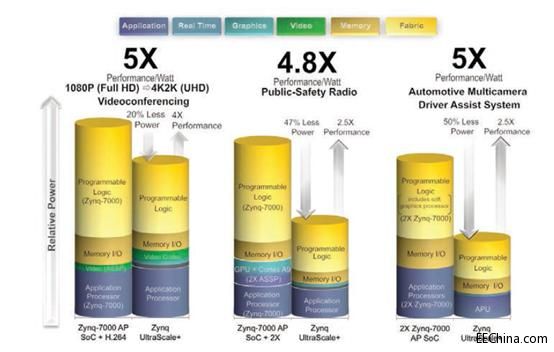

为了说明Zynq UltraScale+ MPSoC的性能功耗比优势,让我们来看一下该器件服务的众多应用中的3个应用的标准测试结果,不同颜色用于演示处理引擎的多样性(如图6所示)。

为创建一个运行全1080p视频的视频会议系统,设计人员采用一个带有独立H.264 ASSP的Zynq SoC。利用Zynq UltraScale+ MPSoC的优势,设计人员现在能够在单个Zynq UltraScale+ MPSoC中实现4Kx2K UHD系统,而且在相同功耗预算条件下,该系统相比双芯片系统而言,性能功耗比提高了5倍。

赛灵思公司高级SoC产品线经理Sumit Shah表示:“在需求使用Zynq SoC和两个ASSP的公共安全无线电应用中,现在您只需使用一个Zynq UltraScale+ MPSoC就可实现整个设计,而且相对此前的配置,系统功耗降低了47%,性能提升了2.5倍,从而实现了4.8倍的性能功耗比优势。”

Shah说,同样的,此前实现在两个28nm Zynq SoC上的汽车多摄像头驾驶员辅助系统,现在可以缩小到一个Zynq UltraScale+ MPSoC上。单芯片系统比双芯片设计的性能提升2.5倍,功耗降低50%。相对此前实现方案而言,这可将性能功耗比净提升5倍。

针对所有UltraScale Plus产品系列的早期客户参与计划正在如火如荼进行。首个流片和设计工具的早期试用版本预计将于2015年第二季度推出。公司有望在2015年第四季度开始向客户出货UltraScale+器件。

如需了解有关16nm UltraScale系列性能功耗比优势的更多信息,敬请访:china.xilinx.com/ultrascale。如需进一步了解有关Zynq UltraScale+ MPSoC的信息,敬请访问:china.xilinx.com/products/technology/ultrascale-mpsoc.html。

| 应用 | 实时 | 图形 | 视频 | 存储器 | 架构 |

| 5倍 | 4.8倍 | 5倍 | |||

| 性能功耗比 | 性能功耗比 | 性能功耗比 | |||

| 1080P(全高清) 4k2k(超高清) | 公共安全无线电 | 汽车多摄像头驾驶员辅助系统 | |||

| 视频会议 | |||||

| 功耗降低20% | 性能提升4倍 | 功耗降低47% | 性能提升2.5倍 | 功耗降低50% | |

| 性能提升2.5倍 | |||||

| 可编程逻辑(Zynq-7000) | 可编程逻辑 | 可编程逻辑(Zynq-7000) | 可编程逻辑 |

赛灵思 SoC PSoC ARM Cortex FPGA LTE 物联网 嵌入式 收发器 电源管理 解码器 无线电 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)