Xilinx 16nm UltraScale+器件实现2至5倍的性能功耗比优势

时间:04-13

来源:互联网

点击:

| 相对功耗 | 相对性能 |

| 采用UltraRAM和SmartConnnet | |

| 不足21W | |

| 48端口无线CPRI压缩和基带硬件加速 | 图像处理PCIe模块 |

| 7系列(28nm) | |

| 采用16 FinFET+的UltraScale架构 |

ZYNQ ULTRASCALE MPSOC可提供超过5倍的性能功耗比优势

尽管赛灵思原本可以采用台积公司20 nm工艺实现其第二代全可编程SoC,但公司仍会选择等待采用台积公司的16 nm FinFET工艺来实现该器件。该器件的异构多处理特性集结合16nm UltraScale架构的性能功耗比优势,可以将16nm Zynq UltraScale+ MPSoC打造成更高效的中央处理系统控制器。该器件可提供超过28 nm Zynq SoC 5倍的性能。

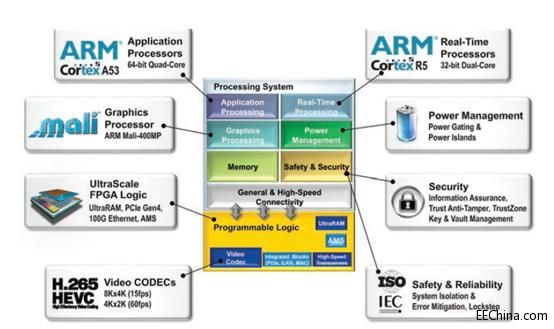

去年,赛灵思针对UltraScale MPSoC架构推出了其“为合适任务提供合适引擎”的使用模型,但保留了有关Zynq UltraScale+ MPSoC器件应有的特定内核的细节。目前公司正发布全特性集Zynq UltraScale+ MPSoC(如图5所示)。

| 应用处理器 | 实时处理器 | |

| 32位双核 | ||

| 64位四核 | ||

| 图形处理器 | 处理系统 | 电源管理 |

| ARM Mali-400MP | 电源门控和电源分区 | |

| UltraScale FPGA逻辑 | 应用处理 实时处理 | 保密性 |

| UltraARM、PCle Gen4、100G Ethernet、AMS | 图形处理 电源管理 | 信息安全保障、可信赖防纂改、 |

| Trustzone、密钥与库管理 | ||

| Video CODEC | 储存器 安全性与保密性 | 安全性与可靠性 |

| 8Kx4K (15fps) | 系统隔离 | |

| 4Kx2K (60fps) | 减少出差率、锁步 | |

| 一般和高速连接 | ||

| 可编程逻辑 |

当然,初始28nm Zynq SoC的最大增值是在单个器件中完美集成了ARM处理系统和可编程逻辑。 Zynq SoC的处理系统(PS)和可编程逻辑(PL)模块通过超过3000多个互联(峰值带宽运行速率约为84 Gbps)连接在一起。PS和PL之间的紧密相连所提供的吞吐量和性能不是一个包含FPGA和独立ASSP的双芯片系统架构能简简单单实现的。

目前借助16nm UltraScale+ MPSoC,赛灵思显著提高了处理系统和可编程逻辑之间的性能,为器件提供了超过6,000次互联(峰值带宽运行速率为500Gbps)。赛灵思公司全可编程SoC产品市场营销与管理总监Barrie Mullins指出:“这使得Zynq UltraScale+ MPSoC处理系统与逻辑系统之间的连接速率比采用28nm Zynq SoC可能实现的连接速率快6倍。而且双芯片(ASSP +FPGA)架构的系统性能远远落后于此。”

Mullins说Zynq UltraScale+ MPSoC的核心是64位四核ARM Cortex-A53处理器,其可提供2倍于 28nm Zynq SoC的双核Cortex-A9处理系统的性能。应用处理系统具有硬件虚拟化和非对称处理功能,可全面支持ARM的TrustZone®套件的安全特性。

赛灵思还为Zynq UltraScale+ MPSoC提供了一个双核ARM Cortex-R5实时处理子系统,可帮助用户向其系统添加确定性操作。实时处理器可确保为需要最高级别吞吐量、安全性和可靠性的应用提供即时系统响应。

为进一步提升处理性能,Zynq UltraScale+ MPSoC还内置了一系列的专用图形引擎。ARM Mali-400MP专用图形加速内核可帮助主CPU分担图形密集型任务。为协助GPU,赛灵思向用于视频压缩/解压缩(支持8Kx4K (15fps)和4Kx2K (60fps)的H.265视频标准)的可编程逻辑块添加了一个硬化的视频编解码器内核。DisplayPort源内核可帮助用户加速视频数据分组,同时还避免其系统使用外部DisplayPort TX发送器芯片。

Zynq UltraScale+ MPSoC还具有一系列片上存储器增强功能。该产品系列中的最大型器件,其可编程逻辑中除Block RAM外,还包含UltraRAM。同时Zynq UltraScale+ MPSoC的处理内核共享L1和L2高速缓存。

Zynq UltraScale+ MPSoC还采用具备ECC功能的位数更宽的72位DDR接口内核(64位+ECC的8位)。该接口能提供用于DDR4的2,400Mbps速率,可支持32GB容量的更大内存深度DRAM。

Zynq UltraScale+ MPSoC上的专用安全单元可提供军事级安全性,诸如安全启动、密钥与库管理,以及防纂改功能等——这些都是设备间通信以及互联控制应用的标准需求。此外,Zynq UltraScale+ MPSoC的可编程逻辑系统还采用了针对150G Interlaken、100G Ethernet MAC和PCIe Gen4的集成连接功能块。板载模拟混合信号(AMS) 内核有助于设计团队利用系统监控器(System Monitor)测试其系统。

借助所有这些功能,不是任何应用都会用到MPSoC中的每个引擎。因此,赛灵思为Zynq UltraScale+ MPSoC提供了一个极其灵活的专用电源管理单元(PMU)。该内核使用户能够控制电源域和分区(粗/细精度),仅为系统正使用的处理单元供电。而且,设计团队能够对该内核进行编程,以实现动态操作,从而确保系统仅运行执行给定任务所需的功能,进而降低功耗。PMU还可实现众多安全性和可靠性,比如信号和误差的检测与缓解、安全状态模式,以及系统隔离与保护。

Myron表示,归功于上述探讨的16nm新增的所有这些处理功能,采用Zynq Ultra-Scale+ MPSoC构建的设计相比采用28nm Zynq SoC实现的设计,性能功耗比优势平均提升5倍。

赛灵思 SoC PSoC ARM Cortex FPGA LTE 物联网 嵌入式 收发器 电源管理 解码器 无线电 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)