FPGA 101:用Vivado HLS为软件提速

时间:07-09

来源:互联网

点击:

清除瓶颈

我对结果非常满意,我希望能用这款芯片与工具集的组合做更多事情。我并没有探索所有的可能性。例如,Vivado HLS还支持AXI主接口。AXI会允许加速器从外部存储器复制矩阵(尽管这样也可能存在安全问题)。不过我强烈建议所有面临代码瓶颈的人都能考虑这个工具集。这里提供足够的培训课程、资源和材料以实现快速匀变,其中包括Doulos提供的课程、资源和材料。如需了解更多信息,敬请访问:www.doulos.com。

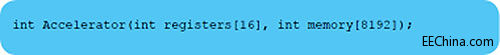

图1 – 调用加速器示例

图2 – 寄存器汇总表地址 寄存器名称 目录 位元 内容

0 Matrix0_ptr RW 32 Matrix 0数据地址

4 Matrix0_shape RW 32 Matrix 0行 Matrix 0列 8 Matrix1_ptr RW 32 Matrix 1数据地址

12 Matrix1_shape RW 32 Matrix 1行 Matrix 1列 16 Matrix2-ptr RW 32 Matrix 2数据地址

20 Matrix2_shape RW 32 Matrix 2行 Matrix 2列 24 Matrix3_ptr RW 32 Matrix 3数据地址

28 Matrix3_shape RW 32 Matrix 3行 Matrix 3列 32 -reserved- - 32 36 -reserved- - 32 40 Command RW 32 0 enum 44 Status RW 32 0 enum 8192 × 32存储器

图3 – 加速器函数API

SoC 赛灵思 FPGA ARM Cortex C语言 Linux 仿真 相关文章:

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 基于Actel FPGA的PWM IP的应用(09-17)

- FPGA中的处理器IP概述(04-14)

- 用于测试SDRAM控制器的PDMA(07-01)

- 设计工具是FPGA在SoC设计中继续应用的关键(07-19)

- 基于FPGA的软件验证推动ASIC与SoC原型设计技术的发展(07-22)