基于逻辑分析内核的FPGA电路内调试

时间:01-20

来源:互联网

点击:

随着FPGA融入越来越多的能力,对有效调试工具的需求将变得至关重要。对内部可视能力的事前周密计划将能使研制组采用正确的调试战略,以更快完成他们的设计任务。

“我知道我的设计中存在一个问题,但我没有很快找到问题所需要的内部可视能力。”由于缺乏足够的内部可视能力,调试FPGA基系统可能会受挫。使用通常包含整个系统的较大FPGA时,调试的可视能力成为很大的问题。为获得内部可视能力,设计工程师必须把一些引脚专门用作调试引脚,而不是实际用于设计。哪些工具可用于进行内部FPGA迹线测量?又有哪些技术可用固定的引脚数最大化内部可视能力?

FPGA设计工程师有两种进行内部迹线测量的方法:

1. 把结点路由至引脚,使用传统的外部逻辑分析仪测试。

2. 把一个逻辑分析仪内核插入FPGA 设计,通过JTAG把由内部FPGA存储器保存的迹线捕获路由输出。

逻辑分析

FPGA开发者要在设计前期作出重要的判定,他们有意识或无意识地确定如何能够调试他们的设计。得到内部FPGA可视能力的最常用方法是使用逻辑分析仪,把感兴趣的内部结点路由至分析仪探测的引脚。这种方法提供深存储器迹线,在这里问题成因和其影响可能有很大的时间间隔。逻辑分析仪能很好测量可能逃逸仿真的异步事件。一个例子是具有非相关频率的两个或多个时钟域交互影响。逻辑分析仪提供强大的触发,所得到的测量结果能建立与其它系统事件的时间相关。

传统逻辑分析仪提供状态和定时模式,因此可同步或异步地捕获数据。在定时模式,设计工程师能看到信号跃变间的关系。在状态模式,设计工程师有能力观察相对于状态时钟的总线。当调试总线值至关重要的数据路径时,状态模式是特别有用的。

有效的真实世界测量需要事先周密的计划。使用传统逻辑分析仪要顾及的主要权衡是把结点路由输出至可探测的引脚。传统逻辑分析仪只能观察到路由至引脚的信号。由于还不知道潜在的电路内调试问题,设计工程师只能把很少几个引脚用于调试。这样少的引脚数可能不足以提供解决手头问题的足够可视能力,从而延误项目的完成。

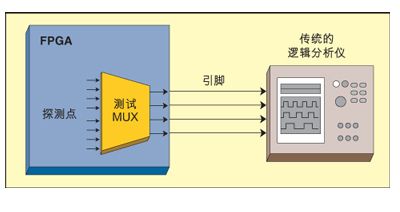

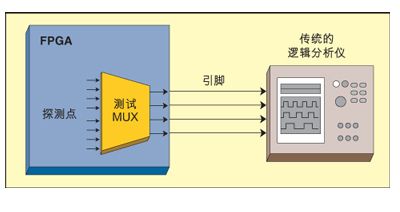

保持内部可视能力,同时减少专用于调试引脚数的一种方法是在设计中插入开关多路转换器(见图1)。例如当 FPGA 设计进入电路时,可能需要观察128个内部结点,这就需要一次跟踪32个通道。在这种情况下,可在FPGA设计中实现多路转换器,在给定时间内路由出32个结点。为编程多路转换器,设计工程师可下载新的配置文件,使用JTAG或通过多路转换器上的控制线经路由切换各信号。在设计阶段,必须仔细规划测试多路转换器插入。否则设计工程师可能止步于不能同时访问需要调试的结点。

图1: 测试多路转换器的插入使设计工程师有能力路由出内部信号的子集,图中为Agilent 16702B所捕获的迹线。

最小化调试专用引脚数的第二种方法是时分复用(TDM)。TDM复用常用于设计原型,此时把多片FPGA 作为单片ASIC的原型,从而用于最小化调试专用引脚数。这项技术最适合用于处理较慢的内部电路。假定使用8位总线的50MHz设计(时钟沿间为20ns)需要电路内的可视能力。使用100MHz在第一个10ns期间采样低4bit,在第二个10ns期间采样高4位。这样仅用4个引脚,就可在每个20ns周期内捕获到全部8位的调试信息。在捕获迹线后,组合相继的4位捕获就可重建8位迹线。TDM复用也有一些缺点。如果用传统逻辑分析仪捕获迹线,触发就变得非常复杂和容易出错。例如在8位码型上的触发就包括把逻辑分析仪设置到寻找跟随规定4位码型后的另一特定4位码型。但逻辑分析仪不知道哪一个4位是 8位组的开始,因此要在与触发设置相匹配的条件上触发-而不是使用者所中意的触发条件。

采用TDM复用时得到的测量结果有精确的周期。但设计工程师却丢失了时钟周期间的定时关系信息。通常单端引脚的速度和逻辑分析仪收集迹线的采集速度(状态模式)限制了压缩比。例如如果最大单端引脚速度是200MHz,内部电路运行于高达100 MHz,那么可实现的最大压缩比是2:1。

随着给定FPGA设计的成熟,它可能会增强和改变。原来专门用于调试的引脚会被用于设计增强。或开始就限制了设计的引脚。另一种调试技术为这类情况带来价值。

逻辑分析内核

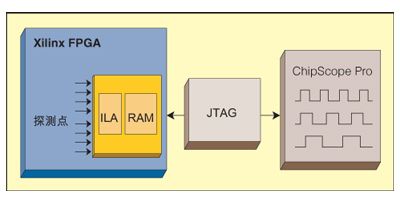

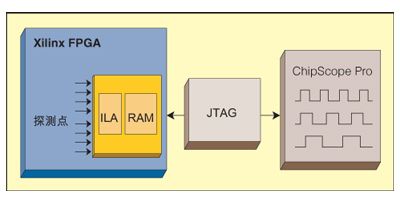

现在大多数FPGA 厂商也提供逻辑分析(见图2)。这些 IP在合成前或合成后插入FPGA。内核包含触发电路,以及用于设置测量和内部RAM,以保存迹线的资源。插入设计的逻辑分析内核改变了设计的定时,因此大多数设计工程师都把内核永久性地留在设计内。

图2: 从 JTAG 下载逻辑分析仪的配置,图中的例子是 Xilinx ChipScopePro。

对于电路内配置,可通过JTAG访问内核,以及为观察而把捕获数据传送到PC。如果内核消耗不到5%的可用资源,FPGA 内核就能充分发挥作用。如果 FPGA的尺寸使内核要消耗超过10%的资源,设计工程师在使用这种方法时将会遇到很多问题。

逻辑分析内核有三项主要优点。

1. 它们的使用不增加引脚。可通过FPGA 上已有的专门JTAG引脚访问。即使没有其它可用引脚,这种调试方法也能得到内部可视能力。

2. 简单的探测。探测包括把结点路由到内部逻辑分析仪的输入。不需要担心为得到有效信息,应如何连接到电路板上,也不存在信号完整性问题。

3. 逻辑分析内核是便宜的。FPGA厂商把他们的业务模型建立于用硅片所获取价值的基础上。所以所用的调试IP 通常能以低于$1,000美元的价格获得。

使用内部逻辑分析内核也有三方面的影响。

1. 内核的尺寸限制了在大FPGA中的使用。此外由于内部FPGA存储器用于迹线,使迹线深度很浅。

2. 设计工程师必须放弃把内部存储器用于调试,存储器会由所作的设计使用。

3. 内部逻辑分析仪只工作于状态模式。它们捕获的数据与规定的时钟同步,而不能提供信号定时关系。

“我知道我的设计中存在一个问题,但我没有很快找到问题所需要的内部可视能力。”由于缺乏足够的内部可视能力,调试FPGA基系统可能会受挫。使用通常包含整个系统的较大FPGA时,调试的可视能力成为很大的问题。为获得内部可视能力,设计工程师必须把一些引脚专门用作调试引脚,而不是实际用于设计。哪些工具可用于进行内部FPGA迹线测量?又有哪些技术可用固定的引脚数最大化内部可视能力?

FPGA设计工程师有两种进行内部迹线测量的方法:

1. 把结点路由至引脚,使用传统的外部逻辑分析仪测试。

2. 把一个逻辑分析仪内核插入FPGA 设计,通过JTAG把由内部FPGA存储器保存的迹线捕获路由输出。

逻辑分析

FPGA开发者要在设计前期作出重要的判定,他们有意识或无意识地确定如何能够调试他们的设计。得到内部FPGA可视能力的最常用方法是使用逻辑分析仪,把感兴趣的内部结点路由至分析仪探测的引脚。这种方法提供深存储器迹线,在这里问题成因和其影响可能有很大的时间间隔。逻辑分析仪能很好测量可能逃逸仿真的异步事件。一个例子是具有非相关频率的两个或多个时钟域交互影响。逻辑分析仪提供强大的触发,所得到的测量结果能建立与其它系统事件的时间相关。

传统逻辑分析仪提供状态和定时模式,因此可同步或异步地捕获数据。在定时模式,设计工程师能看到信号跃变间的关系。在状态模式,设计工程师有能力观察相对于状态时钟的总线。当调试总线值至关重要的数据路径时,状态模式是特别有用的。

有效的真实世界测量需要事先周密的计划。使用传统逻辑分析仪要顾及的主要权衡是把结点路由输出至可探测的引脚。传统逻辑分析仪只能观察到路由至引脚的信号。由于还不知道潜在的电路内调试问题,设计工程师只能把很少几个引脚用于调试。这样少的引脚数可能不足以提供解决手头问题的足够可视能力,从而延误项目的完成。

保持内部可视能力,同时减少专用于调试引脚数的一种方法是在设计中插入开关多路转换器(见图1)。例如当 FPGA 设计进入电路时,可能需要观察128个内部结点,这就需要一次跟踪32个通道。在这种情况下,可在FPGA设计中实现多路转换器,在给定时间内路由出32个结点。为编程多路转换器,设计工程师可下载新的配置文件,使用JTAG或通过多路转换器上的控制线经路由切换各信号。在设计阶段,必须仔细规划测试多路转换器插入。否则设计工程师可能止步于不能同时访问需要调试的结点。

图1: 测试多路转换器的插入使设计工程师有能力路由出内部信号的子集,图中为Agilent 16702B所捕获的迹线。

最小化调试专用引脚数的第二种方法是时分复用(TDM)。TDM复用常用于设计原型,此时把多片FPGA 作为单片ASIC的原型,从而用于最小化调试专用引脚数。这项技术最适合用于处理较慢的内部电路。假定使用8位总线的50MHz设计(时钟沿间为20ns)需要电路内的可视能力。使用100MHz在第一个10ns期间采样低4bit,在第二个10ns期间采样高4位。这样仅用4个引脚,就可在每个20ns周期内捕获到全部8位的调试信息。在捕获迹线后,组合相继的4位捕获就可重建8位迹线。TDM复用也有一些缺点。如果用传统逻辑分析仪捕获迹线,触发就变得非常复杂和容易出错。例如在8位码型上的触发就包括把逻辑分析仪设置到寻找跟随规定4位码型后的另一特定4位码型。但逻辑分析仪不知道哪一个4位是 8位组的开始,因此要在与触发设置相匹配的条件上触发-而不是使用者所中意的触发条件。

采用TDM复用时得到的测量结果有精确的周期。但设计工程师却丢失了时钟周期间的定时关系信息。通常单端引脚的速度和逻辑分析仪收集迹线的采集速度(状态模式)限制了压缩比。例如如果最大单端引脚速度是200MHz,内部电路运行于高达100 MHz,那么可实现的最大压缩比是2:1。

随着给定FPGA设计的成熟,它可能会增强和改变。原来专门用于调试的引脚会被用于设计增强。或开始就限制了设计的引脚。另一种调试技术为这类情况带来价值。

逻辑分析内核

现在大多数FPGA 厂商也提供逻辑分析(见图2)。这些 IP在合成前或合成后插入FPGA。内核包含触发电路,以及用于设置测量和内部RAM,以保存迹线的资源。插入设计的逻辑分析内核改变了设计的定时,因此大多数设计工程师都把内核永久性地留在设计内。

图2: 从 JTAG 下载逻辑分析仪的配置,图中的例子是 Xilinx ChipScopePro。

对于电路内配置,可通过JTAG访问内核,以及为观察而把捕获数据传送到PC。如果内核消耗不到5%的可用资源,FPGA 内核就能充分发挥作用。如果 FPGA的尺寸使内核要消耗超过10%的资源,设计工程师在使用这种方法时将会遇到很多问题。

逻辑分析内核有三项主要优点。

1. 它们的使用不增加引脚。可通过FPGA 上已有的专门JTAG引脚访问。即使没有其它可用引脚,这种调试方法也能得到内部可视能力。

2. 简单的探测。探测包括把结点路由到内部逻辑分析仪的输入。不需要担心为得到有效信息,应如何连接到电路板上,也不存在信号完整性问题。

3. 逻辑分析内核是便宜的。FPGA厂商把他们的业务模型建立于用硅片所获取价值的基础上。所以所用的调试IP 通常能以低于$1,000美元的价格获得。

使用内部逻辑分析内核也有三方面的影响。

1. 内核的尺寸限制了在大FPGA中的使用。此外由于内部FPGA存储器用于迹线,使迹线深度很浅。

2. 设计工程师必须放弃把内部存储器用于调试,存储器会由所作的设计使用。

3. 内部逻辑分析仪只工作于状态模式。它们捕获的数据与规定的时钟同步,而不能提供信号定时关系。

FPGA 仿真 总线 电路 Xilinx 连接器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)