基于FPGA和DDS技术的正弦信号发生器设计

时间:11-09

来源:互联网

点击:

(2)FPGA处理模块实现方式

根据设计要求:要达到正弦波输出频率范围(1 kHz~10 MHz)及频率步进值100 Hz,设相位累加器的位宽为2N,sin表的大小为2P,累加器的高P位用于寻址Sin表。根据DDS工作原理,主频时钟Clock的频率为,fc=100 MHz,累加器按步进为1进行累加直至溢出一遍的频率即为频率步进值。

以M点为步长(M为频率控制字),产生信号的频率:

由于频率步进值为100 Hz,由式(1)可计算得N=20。要使输出频率达到10 MHz,由式(2)可计算得M=104 857,为了使输出的波形尽可能不失真,频率控制字位宽取17位,高三位添000,由于设计加法器为32位,则低12位添000000000000。本系统中使用的D/A转换器件的输入位宽为10,所以只取相位累加器输出的高10位可满足设计要求。整个过程的实现过程中,本系统选用Altera公司的Cyclone系列芯片,采用VHDL语言描述,利用开发软件QuartusⅡ进行综合,以实现产生l kHz~10 MHz频率范围内的各种正弦信号。

3 实验数据测试

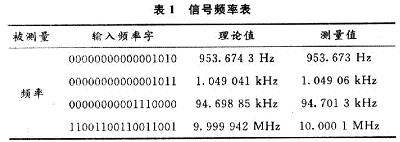

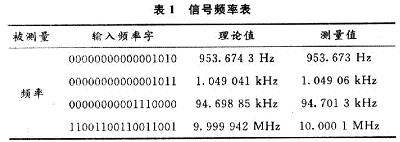

由键盘输入的是二进制频率控制字,通过数码管可以显示出十进制的频率和相位,将信号发生器的输出端和双通道数字示波器接好,任意几个频率为1 kHz~10 MHz之间的信号测试结果如表1所示。

4 结语

本系统设计时,相位字是在编程时就固定的,输出正弦信号的频率变化是由频率字变化引起的,而频率字的预置是通过键盘输入的,因此能够得到频率变化的正弦信号,这样的信号源能够很好地满足需要变频信号的情况,因此,实用性较强。通过理论计算和实际测量相比较可以看出,基于FPGA的DDS技术实现正弦信号发生器输出正弦信号频率范围较宽、分辨率高、幅度和频率的精度较高。另外,本系统还很容易扩展,不需要对硬件电路进行较大的修改,只需要修改相应的程序便可实现相应的功能,比如产生PSK,ASK信号等。但是它也有局限性,主要表现在输出杂散大,这是由于DDS采用全数字结构,不可避免地引入杂散,主要来源有三个:相位累加器相位舍位误差造成的杂散;幅度量化误差造成的杂散和DAC非线性造成的杂散。

根据设计要求:要达到正弦波输出频率范围(1 kHz~10 MHz)及频率步进值100 Hz,设相位累加器的位宽为2N,sin表的大小为2P,累加器的高P位用于寻址Sin表。根据DDS工作原理,主频时钟Clock的频率为,fc=100 MHz,累加器按步进为1进行累加直至溢出一遍的频率即为频率步进值。

以M点为步长(M为频率控制字),产生信号的频率:

由于频率步进值为100 Hz,由式(1)可计算得N=20。要使输出频率达到10 MHz,由式(2)可计算得M=104 857,为了使输出的波形尽可能不失真,频率控制字位宽取17位,高三位添000,由于设计加法器为32位,则低12位添000000000000。本系统中使用的D/A转换器件的输入位宽为10,所以只取相位累加器输出的高10位可满足设计要求。整个过程的实现过程中,本系统选用Altera公司的Cyclone系列芯片,采用VHDL语言描述,利用开发软件QuartusⅡ进行综合,以实现产生l kHz~10 MHz频率范围内的各种正弦信号。

3 实验数据测试

由键盘输入的是二进制频率控制字,通过数码管可以显示出十进制的频率和相位,将信号发生器的输出端和双通道数字示波器接好,任意几个频率为1 kHz~10 MHz之间的信号测试结果如表1所示。

4 结语

本系统设计时,相位字是在编程时就固定的,输出正弦信号的频率变化是由频率字变化引起的,而频率字的预置是通过键盘输入的,因此能够得到频率变化的正弦信号,这样的信号源能够很好地满足需要变频信号的情况,因此,实用性较强。通过理论计算和实际测量相比较可以看出,基于FPGA的DDS技术实现正弦信号发生器输出正弦信号频率范围较宽、分辨率高、幅度和频率的精度较高。另外,本系统还很容易扩展,不需要对硬件电路进行较大的修改,只需要修改相应的程序便可实现相应的功能,比如产生PSK,ASK信号等。但是它也有局限性,主要表现在输出杂散大,这是由于DDS采用全数字结构,不可避免地引入杂散,主要来源有三个:相位累加器相位舍位误差造成的杂散;幅度量化误差造成的杂散和DAC非线性造成的杂散。

电子 信号发生器 电路 FPGA 振荡器 滤波器 低通滤波器 单片机 LED Altera VHDL Quartus 示波器 DAC 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)