基于FPGA和DDS技术的正弦信号发生器设计

时间:11-09

来源:互联网

点击:

1971年,美国学者J. Tierney等人撰写的《A Digital Frequency Synthesizer》一文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新合成原理。限于当时的技术,没有得到重视,但随着微电子技术的迅速发展,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术的佼佼者,具体体现在相对带宽宽,频率转换时间短,频率分辨率高,输出相位连续,可产生多种调制信号,控制灵活方便。因此,对于正弦信号发生器的设计,可以采用DDS,即直接数字频率合成方案实现。DDS的输出频率是数字可调的,完全能实现频率为1 kHz~10 MHz之间的正弦信号,这是实际应用中产生可调频率正弦信号波形较为理想的方案。实现DDS常用3种技术方案:高性能DDS单片电路的解决方案;低频正弦波DDS单片电路的解决方案;自行设计的基于FPGA芯片的解决方案。虽然有的专用DDS芯片的功能也比较多,但控制方式却是固定的,因此不一定满足用户需求。而基于FPGA则可以根据需要方便地实现各种比较复杂的调频、调相和调幅功能,具有良好的实用性。专用DDS芯片由于采用特定的集成工艺,内部数字信号抖动很小,可以输出高质量的模拟信号;利用FPGA也能输出较高质量的信号,虽然达不到专用DDS芯片的水平,但信号精度误差非常小,能满足大多数信号源要求。DDS是本系统的关键技术,在介绍本系统之前,先单独介绍DDS的原理。

1 DDS电路工作原理

1.1 DDS的工作原理

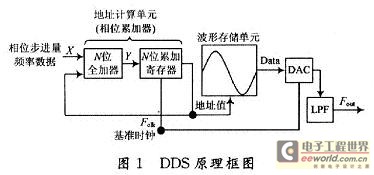

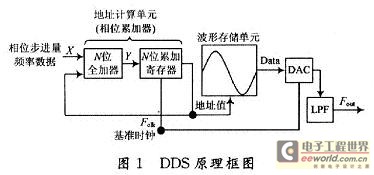

DDS的工作原理是以数控振荡器的方式产生频率、相位可控制的正弦波。如图1所示,电路一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和低通滤波器(LPF)。频率累加器对输入信号进行累加运算,产生频率控制数据X(frequency data或相位步进量)。相位累加器由N位全加器和N位累加寄存器级联而成,对代表频率的二进制码进行累加运算,是典型的反馈电路,产生累加结果Y。幅度/相位转换电路实质上是一个波形寄存器,以供查表使用。读出的波形数据送入D/A转换器和低通滤波器转换成符合要求的模拟信号。

1.2 具体工作过程

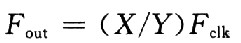

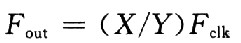

信号产生过程:如图1所示,N位加法器将频率控制数据X与累加寄存器输出的累加相位数据在时钟脉冲Fclk控制下相加,把相加后的结果Y送至累加寄存器的输入端。累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据X相加;另一方面将这个值作为取样地址值送入幅度/相位转换电路(即图1中的波形存储器),幅度/相位转换电路根据这个地址输出相应的波形数据。最后经D/A转换器和低通滤波器将波形数据处理成所需要的模拟波形。相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器加满量时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS信号的一频率周期。DDS输出信号的频率由下式给定:

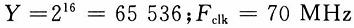

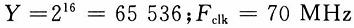

假定基准时钟为70 MHz,累加器为16位,则:

再假定X=4 096,则Fout=(4 096/65 536)×70=4.375 MHz。

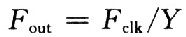

可见,通过设定相位累加器位数、频率控制字X和基准时钟的值,就可以产生任一频率的输出。DDS的频率分辨率定义为:

由于基准时钟一般固定,因此相位累加器的位数就决定了频率分辨率。如上面的例子,相位累加器为16位,那么频率分辨率就可以认为是16位。位数越多,分频率越高。

2 正弦信号发生器系统结构设计及实现

2.1 系统结构图

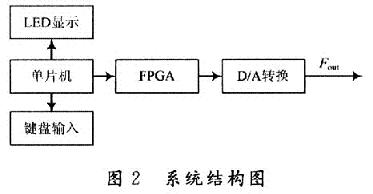

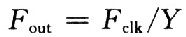

正弦信号发生器系统结构图如图2所示。

2.2 单元电路

2.2.1 单片机控制模块实现方式

单片机实现部分主要处理数据输入及数据显示,此模块以AT89S51为中心,控制键盘输入和LED显示,其中键盘输入值作为频率控制字送给FPGA处理。单片机的P1口直接与键盘连接,无键按下时为高电平,当有键按下时就变为低电平。可以设计键1为“0”值键、键2为“1”值键,满足频率控制字以二进制进行输入;键3为输入确定键;键4和键5为频率步进控制键,键4为加100 Hz键,键5为减100 Hz键,当键3按下时将输入设置的频率控制字以二进制数形式送至P2口,然后通过串行口输出并驱动LED静态显示。PO.O和PO.1及PO.2控制数据输出的先后顺序。此模块功能具体实现可通过汇编语言编程后下载到单片机调试并实现,限于篇幅,具体程序不在此展现,只展示设计思路。

2.2.2 FPGA处理模块

(1)FPGA处理模块控制原理

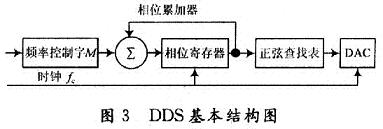

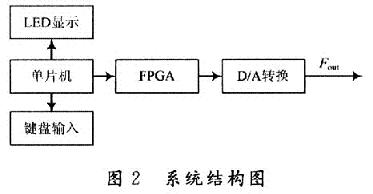

FPGA处理模块是本系统的核心,系统结构图中FPGA模块里的DDS基本结构图如图3所示。

图3中DDS工作原理为:相位累加器由32位加法器与32位累加寄存器级联构成。在时钟脉冲,fc的控制下,加法器将频率控制字M与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位。

DDS采用改变寻址的步长来改变输出信号的频率,步长即为对数字波形查表的相位增量,由累加器对相位增量进行累加,累加器的值作为查表地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换,波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

1 DDS电路工作原理

1.1 DDS的工作原理

DDS的工作原理是以数控振荡器的方式产生频率、相位可控制的正弦波。如图1所示,电路一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和低通滤波器(LPF)。频率累加器对输入信号进行累加运算,产生频率控制数据X(frequency data或相位步进量)。相位累加器由N位全加器和N位累加寄存器级联而成,对代表频率的二进制码进行累加运算,是典型的反馈电路,产生累加结果Y。幅度/相位转换电路实质上是一个波形寄存器,以供查表使用。读出的波形数据送入D/A转换器和低通滤波器转换成符合要求的模拟信号。

1.2 具体工作过程

信号产生过程:如图1所示,N位加法器将频率控制数据X与累加寄存器输出的累加相位数据在时钟脉冲Fclk控制下相加,把相加后的结果Y送至累加寄存器的输入端。累加寄存器一方面将在上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据X相加;另一方面将这个值作为取样地址值送入幅度/相位转换电路(即图1中的波形存储器),幅度/相位转换电路根据这个地址输出相应的波形数据。最后经D/A转换器和低通滤波器将波形数据处理成所需要的模拟波形。相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器加满量时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS信号的一频率周期。DDS输出信号的频率由下式给定:

假定基准时钟为70 MHz,累加器为16位,则:

再假定X=4 096,则Fout=(4 096/65 536)×70=4.375 MHz。

可见,通过设定相位累加器位数、频率控制字X和基准时钟的值,就可以产生任一频率的输出。DDS的频率分辨率定义为:

由于基准时钟一般固定,因此相位累加器的位数就决定了频率分辨率。如上面的例子,相位累加器为16位,那么频率分辨率就可以认为是16位。位数越多,分频率越高。

2 正弦信号发生器系统结构设计及实现

2.1 系统结构图

正弦信号发生器系统结构图如图2所示。

2.2 单元电路

2.2.1 单片机控制模块实现方式

单片机实现部分主要处理数据输入及数据显示,此模块以AT89S51为中心,控制键盘输入和LED显示,其中键盘输入值作为频率控制字送给FPGA处理。单片机的P1口直接与键盘连接,无键按下时为高电平,当有键按下时就变为低电平。可以设计键1为“0”值键、键2为“1”值键,满足频率控制字以二进制进行输入;键3为输入确定键;键4和键5为频率步进控制键,键4为加100 Hz键,键5为减100 Hz键,当键3按下时将输入设置的频率控制字以二进制数形式送至P2口,然后通过串行口输出并驱动LED静态显示。PO.O和PO.1及PO.2控制数据输出的先后顺序。此模块功能具体实现可通过汇编语言编程后下载到单片机调试并实现,限于篇幅,具体程序不在此展现,只展示设计思路。

2.2.2 FPGA处理模块

(1)FPGA处理模块控制原理

FPGA处理模块是本系统的核心,系统结构图中FPGA模块里的DDS基本结构图如图3所示。

图3中DDS工作原理为:相位累加器由32位加法器与32位累加寄存器级联构成。在时钟脉冲,fc的控制下,加法器将频率控制字M与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位。

DDS采用改变寻址的步长来改变输出信号的频率,步长即为对数字波形查表的相位增量,由累加器对相位增量进行累加,累加器的值作为查表地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换,波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

电子 信号发生器 电路 FPGA 振荡器 滤波器 低通滤波器 单片机 LED Altera VHDL Quartus 示波器 DAC 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)