基于数据选择器和D触发器的多输入时序电路

时间:11-09

来源:互联网

点击:

在SSI时序逻辑电路设计中,遵循的设计准则是:在保证所设计的时序逻辑电路具有正确功能的前提下,触发器的激励函数应最小化,从而简化电路结构。用卡诺图法或公式法化简触发器的激励函数,在多输入变量时相当繁琐甚至难以进行。因此,需要寻求多输入时序逻辑电路简捷设计方法。本文给出多输入变量时序逻辑网络的一种新型结构:将D触发器和数据选择器进行组合,构成既有存储功能又有数据选择功能的多输入时序网络,并给出设计过程中不需要进行函数化简的设计技术。

1 基本原理

1.1 基本多输入时序网络

1.1.1 多输入时序网络的基本形式

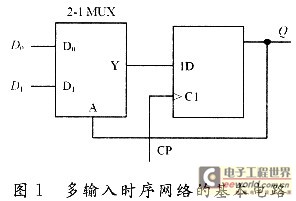

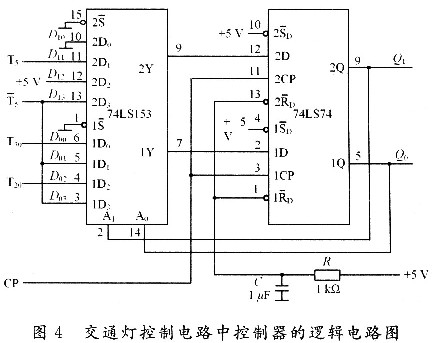

用1个D触发器和1个2选1数据选择器构成多输入时序网络的基本电路,如图1所示。

图1中,触发器的现态输出Qn作为数据选择器的A选择输入变量,数据选择器的Y输出作为触发器的D输入信号,数据选择器的输入端D0,D1作为所构成时序网络的外部信号输入端。

1.1.2 多输入时序网络基本电路的状态方程

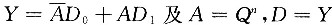

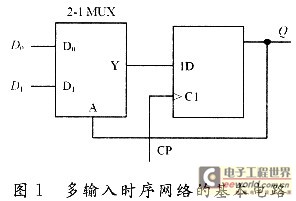

由D触发器的特性方程Qn+1=D、数据选择器的输出逻辑表达式

的关系,得多输入时序网络基本电路的状态方程:

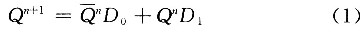

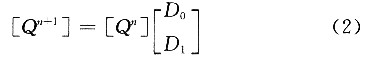

写成矩阵形式为:

1.1.3 已知状态转换关系确定时序网络输入矩阵参数的方法

由式(1)、式(2)有:

(1)现态Qn=0时,Qn+1=D0,选择输入D0,由状态转换关系确定D0。可实现所要求的状态转换:

若Qn+1=O,即状态转换为0→O,则式(2)中的输入矩阵应填D0=0;

若Qn+1=1,即状态转换为O→1,则式(2)中的输入矩阵应填D0=使状态产生变化的输入变量。

(2)现态Qn=1时,Qn+1=D1,选择输入D1,由状态转换关系确定D1可实现所要求的状态转换:

若Qn+1=1,即状态转换为1→1,则式(2)中的输入矩阵中应填D1=1;

若Qn+1=0,即状态转换为1→O,则式(2)中的输入矩阵中应填D1=使状态产生变化的输入变量取反。

1.2 2个状态变量的多输入时序网络

1.2.1 2个状态变量多输入时序网络的形式

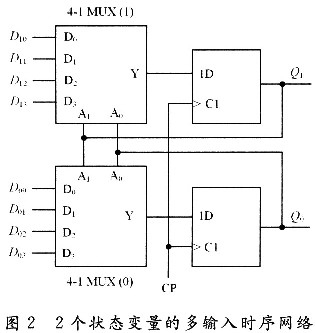

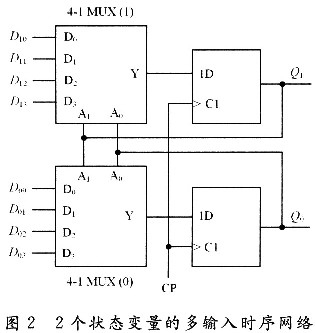

用2个D触发器和2个4选1数据选择器可构成有2个状态变量的多输入时序网络,如图2所示。

图2中,触发器的2个现态输出

作为数据选择器的A1A0选择输入变量,2个数据选择器的Y输出分别作为2个触发器的D输入信号,数据选择器的输入端D10~D13,D00~D03作为所构成时序网络的外部信号输入端。

1.2.2 两个状态变量多输入时序网络的状态方程

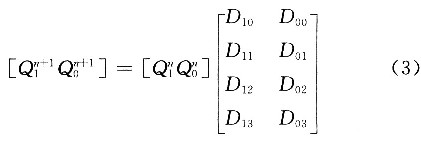

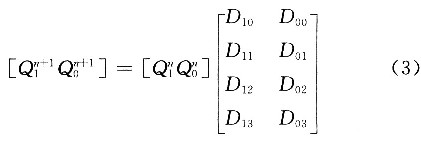

按基本多输入时序网络的分析方法,可得状态方程的矩阵形式为:

1.2.3 现态对输入信号的选择及输入矩阵参数的确定

现态的取值组合决定所选择的数据输入端,而数据输入端的输人情况又决定次态:

已知状态转换关系确定式(3)中输入矩阵参数的方法如1.1.2所述。

1.3 n个状态变量的多输入时序网络

按照D触发器的现态组合作为数据选择器的选择输入变量、数据选择器的输出作为D触发器输入信号的构成方法,用n个D触发器、n个2n选1数据选择器组合,可构成n个状态变量的多输入时序网络。

2 基于数据选择器和D触发器的多输入时序逻辑电路设计

2.1 设计步骤

采用数据选择器和D触发器构成的多输入时序网络进行多输入时序逻辑电路设计的步骤:

(1)由设计要求做出最简状态图;

(2)根据状态个数确定多输入时序网络中D触发器、数据选择器的个数及数据选择器的选择规模;

(3)根据状态转换关系确定输入矩阵的参数,即确定数据选择器输入端所接的变量或常量;

(4)画出时序逻辑图。

2.2 应用举例

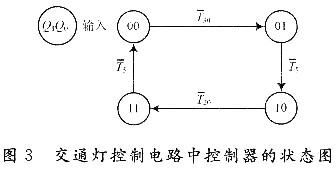

主干道、支干道十字路口交通灯控制电路中的控制器共有4个状态,在不同输入信号的作用下进行状态转换:

(1) =00状态,主干道绿灯亮、支干道红灯亮,到了规定的30 s时间隔由控制电路中的计数器向控制器输入1个T30=1的信号,控制器转到下一工作状态;

=00状态,主干道绿灯亮、支干道红灯亮,到了规定的30 s时间隔由控制电路中的计数器向控制器输入1个T30=1的信号,控制器转到下一工作状态;

(2) =01状态,主干道黄灯亮、支干道红灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到下一工作状态;

=01状态,主干道黄灯亮、支干道红灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到下一工作状态;

(3) =10状态,主干道红灯亮、支干道绿灯亮,到了规定的20 s时间隔由控制电路中的计数器向控制器输入1个T20=1的信号,控制器转到下一工作状态;

=10状态,主干道红灯亮、支干道绿灯亮,到了规定的20 s时间隔由控制电路中的计数器向控制器输入1个T20=1的信号,控制器转到下一工作状态;

(4) =11状态,主干道红灯亮、支干道黄灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到第(1)种工作状态。

=11状态,主干道红灯亮、支干道黄灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到第(1)种工作状态。

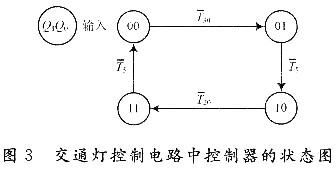

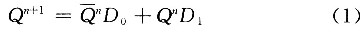

控制器的状态图如图3所示。

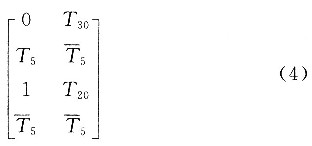

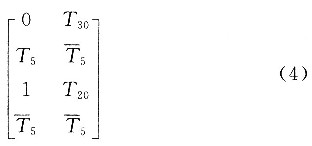

用有2个状态变量的多输入时序网络实现,由图3所示状态图的状态转换关系,可确定输入矩阵参数为:

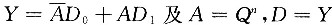

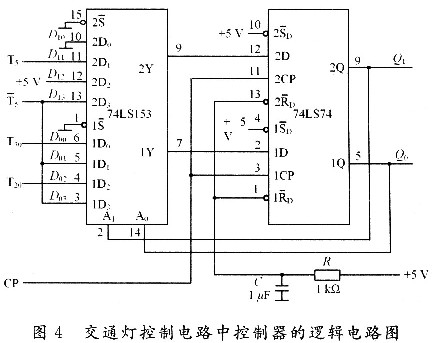

选用双D触发器74LS74和双4选1数据选择器74LSl53构成多输入时序网络并由式(4)连接输入端画出逻辑图如图4所示,其中R,C构成通电复位电路。

1 基本原理

1.1 基本多输入时序网络

1.1.1 多输入时序网络的基本形式

用1个D触发器和1个2选1数据选择器构成多输入时序网络的基本电路,如图1所示。

图1中,触发器的现态输出Qn作为数据选择器的A选择输入变量,数据选择器的Y输出作为触发器的D输入信号,数据选择器的输入端D0,D1作为所构成时序网络的外部信号输入端。

1.1.2 多输入时序网络基本电路的状态方程

由D触发器的特性方程Qn+1=D、数据选择器的输出逻辑表达式

的关系,得多输入时序网络基本电路的状态方程:

写成矩阵形式为:

1.1.3 已知状态转换关系确定时序网络输入矩阵参数的方法

由式(1)、式(2)有:

(1)现态Qn=0时,Qn+1=D0,选择输入D0,由状态转换关系确定D0。可实现所要求的状态转换:

若Qn+1=O,即状态转换为0→O,则式(2)中的输入矩阵应填D0=0;

若Qn+1=1,即状态转换为O→1,则式(2)中的输入矩阵应填D0=使状态产生变化的输入变量。

(2)现态Qn=1时,Qn+1=D1,选择输入D1,由状态转换关系确定D1可实现所要求的状态转换:

若Qn+1=1,即状态转换为1→1,则式(2)中的输入矩阵中应填D1=1;

若Qn+1=0,即状态转换为1→O,则式(2)中的输入矩阵中应填D1=使状态产生变化的输入变量取反。

1.2 2个状态变量的多输入时序网络

1.2.1 2个状态变量多输入时序网络的形式

用2个D触发器和2个4选1数据选择器可构成有2个状态变量的多输入时序网络,如图2所示。

图2中,触发器的2个现态输出

作为数据选择器的A1A0选择输入变量,2个数据选择器的Y输出分别作为2个触发器的D输入信号,数据选择器的输入端D10~D13,D00~D03作为所构成时序网络的外部信号输入端。

1.2.2 两个状态变量多输入时序网络的状态方程

按基本多输入时序网络的分析方法,可得状态方程的矩阵形式为:

1.2.3 现态对输入信号的选择及输入矩阵参数的确定

现态的取值组合决定所选择的数据输入端,而数据输入端的输人情况又决定次态:

已知状态转换关系确定式(3)中输入矩阵参数的方法如1.1.2所述。

1.3 n个状态变量的多输入时序网络

按照D触发器的现态组合作为数据选择器的选择输入变量、数据选择器的输出作为D触发器输入信号的构成方法,用n个D触发器、n个2n选1数据选择器组合,可构成n个状态变量的多输入时序网络。

2 基于数据选择器和D触发器的多输入时序逻辑电路设计

2.1 设计步骤

采用数据选择器和D触发器构成的多输入时序网络进行多输入时序逻辑电路设计的步骤:

(1)由设计要求做出最简状态图;

(2)根据状态个数确定多输入时序网络中D触发器、数据选择器的个数及数据选择器的选择规模;

(3)根据状态转换关系确定输入矩阵的参数,即确定数据选择器输入端所接的变量或常量;

(4)画出时序逻辑图。

2.2 应用举例

主干道、支干道十字路口交通灯控制电路中的控制器共有4个状态,在不同输入信号的作用下进行状态转换:

(1)

=00状态,主干道绿灯亮、支干道红灯亮,到了规定的30 s时间隔由控制电路中的计数器向控制器输入1个T30=1的信号,控制器转到下一工作状态;

=00状态,主干道绿灯亮、支干道红灯亮,到了规定的30 s时间隔由控制电路中的计数器向控制器输入1个T30=1的信号,控制器转到下一工作状态;(2)

=01状态,主干道黄灯亮、支干道红灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到下一工作状态;

=01状态,主干道黄灯亮、支干道红灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到下一工作状态;(3)

=10状态,主干道红灯亮、支干道绿灯亮,到了规定的20 s时间隔由控制电路中的计数器向控制器输入1个T20=1的信号,控制器转到下一工作状态;

=10状态,主干道红灯亮、支干道绿灯亮,到了规定的20 s时间隔由控制电路中的计数器向控制器输入1个T20=1的信号,控制器转到下一工作状态;(4)

=11状态,主干道红灯亮、支干道黄灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到第(1)种工作状态。

=11状态,主干道红灯亮、支干道黄灯亮,到了规定的5 s时间隔由控制电路中的计数器向控制器输入1个T5=1的信号,控制器转到第(1)种工作状态。控制器的状态图如图3所示。

用有2个状态变量的多输入时序网络实现,由图3所示状态图的状态转换关系,可确定输入矩阵参数为:

选用双D触发器74LS74和双4选1数据选择器74LSl53构成多输入时序网络并由式(4)连接输入端画出逻辑图如图4所示,其中R,C构成通电复位电路。

电路 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)