基于双DSP的雷场侦察图像实时压缩存储方法

时间:11-09

来源:互联网

点击:

1 引言

以直升机(有人机或无人机)为平台,利用可见光成像和红外成像传感器技术,可以昼夜进行远距离、大面积雷场侦察及其他障碍体系的侦察。当机载雷场侦察系统执行任务时,系统对接收的雷场图像进行GPS标定,同时将标定的图像实时压缩、存储和传输。该系统具有极高的实时性要求。因此,考虑在系统中采用双DSP和复杂可编程逻辑器件(CPLD)为核心来构建高速处理体系。一方面,采用双DSP体系结构可以使系统具备极高的运算处理速度,满足实时性要求,另一方面,CPLD的引入使系统的灵活性得到了很大的提高。将二者结合可使该系统充分体现新一代图像压缩系统更快速、更灵活的特点。

2 TMS320C62XX系列DSP的特点

根据图像压缩和存储系统的特点,采用美国德州仪器(TI)公司的TMS320C62xx系列定点DSP作为核心处理器。其主频为200 MHz"300 MHz,数据处理能力为1600 MI/s"2400 MI/s。它的主要特点如下:

(1)DSP内核采用超长指令字(VLIW)体系结构,8个功能单元共用32个32 bit通用寄存器,最多可在一个周期内同时执行8条32位指令,

从而大大提高了程序的执行速度;

(2)电路内部集成了l Mbit~7 Mbit片内SRAM,分为内部程序/Cache存储器和内部数据/Cache存储器,不存在片内存储器与外部存储器的总线竞争和访问速度不匹配问题,因此访问速度快,可以充分利用DSP强大的数据处理能力;

(3)具有32 bit外部存储器接口(EMIF),外部存储器可寻址空间高达52 MByte。可与SDRAM和SBRAM实现无缝连接,用于大容量高速存储。其直接异步存储器接口可与SRAM和EPROM连接,用于小容量数据存储和程序存储。

3 系统硬件设计

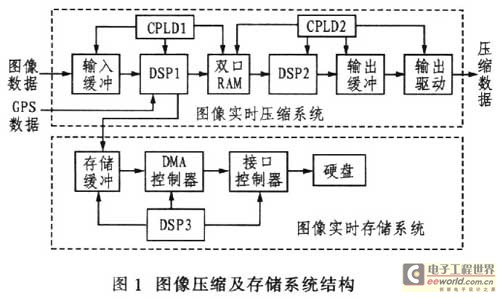

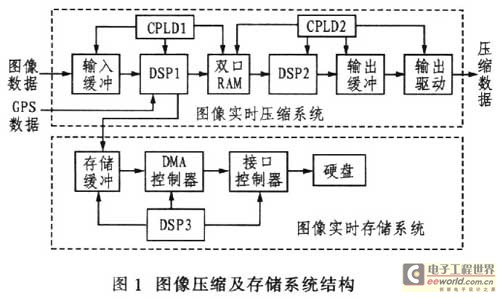

按功能划分,图像压缩及存储系统包括图像采集模块、GPS数据采集模块、CPLD逻辑控制模块、双口RAM+双DSP图像处理模块、图像实时存储模块和压缩数据输出模块。

为满足系统实时性要求,整个系统的设计使用3个DSP,其中1个用于压缩数据的实时存储,2个采用级联方式工作的DSP用于雷场图像的实时压缩和传输。系统结构如图l所示。

DSPl接收成像设备产生雷场图像数据和GPS定位系统产生定位数据,并根据GPS定位数据标定雷场图像,然后对标定后的图像进行实时压缩。DSP2对压缩后的雷场图像依次进行量化重排、信源编码和信道编码,并将编码后的图像通过数传机发送到地面。DSP3主要负责控制压缩数据的实时存储。

3.1 图像采集模块

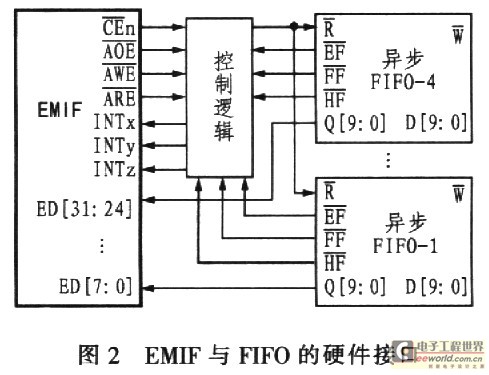

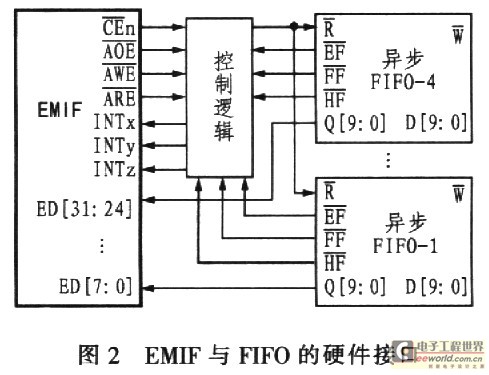

本系统采用图1所示的DSPl的EMIF来实现与可见光成像传感器和红外成像传感器之间的通信,采集雷场的可见光图像和红外图像信息。由于DSPl的EMIF接口是32位,而图像数据的输入字宽为8位,为了充分利用DSP的资源,使系统满足快速传输处理的要求,设计时在传感器和DSPl之间使用4个8位异步FIFO存储器作为图像数据的输入缓冲。FIFO与EMIF之间的硬件接口如图2所示。

图2中的控制逻辑通过图l的CPLDl来实现。CPLD1根据系统所需要的时序,控制产生EMIF的片选信号(CEn)、异步输出允许信号(AOE)、异步写允许信号(AWE)、异步读允许信号(ARE),同时通过接收FIFO的空标志(EF)、满标志(FF)及半满标志(HF)来产生DSP的中断信号(INTx、INTy、INTz),从而实现4个异步FIFO的读写操作。

3.2 GPS数据采集模块

通过各种光学设备拍摄到的雷场图像必须标定上相应的地理坐标信息才能使其具有实际意义。因此,系统的输入数据除了雷场图像数据外还应包含相应的GPS定位数据。

由GPS定位系统根据伪距差分定位原理计算出的GPS定位数据按照整秒输出,输出接口为RS-232型串行接口。TMS320C62xx系列DSP带有3个多通道缓冲串口(McBSP0——McBSP2),考虑到McB-SP串口的电气特性与RS-232串口的电气特性之间存在差异,设计时在DSPI的McBSP接口上外接1个RS-232收发器,以便实现串口通讯,接收GPS定位数据。

3.3 CPLD逻辑控制模块

为了协调系统中每个功能独立的电路高效率工作,使用了2个复杂可编程逻辑器件(CPLD)控制DSP内部多段内存空间的访问,并管理DSP与双口RAM和FIFO之间的访问时序。

此外,由于光学设备的数据输出字宽为8位、TTL电平,而DSP的EMIF接口是32位、LVTTL电平。因此,CPLD还必须通过控制相应的接口电路来解决因光学设备与DSP之间的接口差异而产生的问题,从而保证整个系统有序、高效的运行。

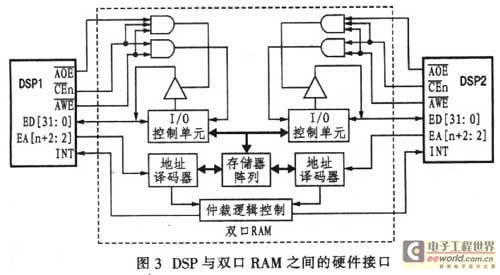

3.4 双口RAM+双DSP图像处理模块

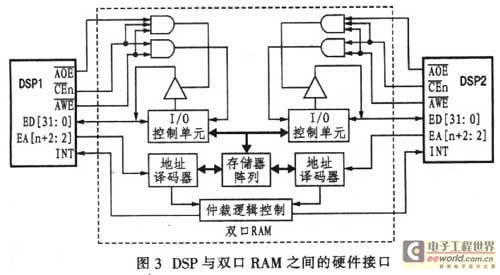

作为图像压缩和存储系统的核心,图像处理模块以双DSP为运算处理核心单元,并辅以双口RAM实现2个DSP之间的高速通信。2个DSP的外部存储器接口EMIF与双口RAM之间的接口设计如图3所示,图中的双口RAM采用的是32位异步RAM。

在图3所示的2个DSP中,DSPl的功能如下:

以直升机(有人机或无人机)为平台,利用可见光成像和红外成像传感器技术,可以昼夜进行远距离、大面积雷场侦察及其他障碍体系的侦察。当机载雷场侦察系统执行任务时,系统对接收的雷场图像进行GPS标定,同时将标定的图像实时压缩、存储和传输。该系统具有极高的实时性要求。因此,考虑在系统中采用双DSP和复杂可编程逻辑器件(CPLD)为核心来构建高速处理体系。一方面,采用双DSP体系结构可以使系统具备极高的运算处理速度,满足实时性要求,另一方面,CPLD的引入使系统的灵活性得到了很大的提高。将二者结合可使该系统充分体现新一代图像压缩系统更快速、更灵活的特点。

2 TMS320C62XX系列DSP的特点

根据图像压缩和存储系统的特点,采用美国德州仪器(TI)公司的TMS320C62xx系列定点DSP作为核心处理器。其主频为200 MHz"300 MHz,数据处理能力为1600 MI/s"2400 MI/s。它的主要特点如下:

(1)DSP内核采用超长指令字(VLIW)体系结构,8个功能单元共用32个32 bit通用寄存器,最多可在一个周期内同时执行8条32位指令,

从而大大提高了程序的执行速度;

(2)电路内部集成了l Mbit~7 Mbit片内SRAM,分为内部程序/Cache存储器和内部数据/Cache存储器,不存在片内存储器与外部存储器的总线竞争和访问速度不匹配问题,因此访问速度快,可以充分利用DSP强大的数据处理能力;

(3)具有32 bit外部存储器接口(EMIF),外部存储器可寻址空间高达52 MByte。可与SDRAM和SBRAM实现无缝连接,用于大容量高速存储。其直接异步存储器接口可与SRAM和EPROM连接,用于小容量数据存储和程序存储。

3 系统硬件设计

按功能划分,图像压缩及存储系统包括图像采集模块、GPS数据采集模块、CPLD逻辑控制模块、双口RAM+双DSP图像处理模块、图像实时存储模块和压缩数据输出模块。

为满足系统实时性要求,整个系统的设计使用3个DSP,其中1个用于压缩数据的实时存储,2个采用级联方式工作的DSP用于雷场图像的实时压缩和传输。系统结构如图l所示。

DSPl接收成像设备产生雷场图像数据和GPS定位系统产生定位数据,并根据GPS定位数据标定雷场图像,然后对标定后的图像进行实时压缩。DSP2对压缩后的雷场图像依次进行量化重排、信源编码和信道编码,并将编码后的图像通过数传机发送到地面。DSP3主要负责控制压缩数据的实时存储。

3.1 图像采集模块

本系统采用图1所示的DSPl的EMIF来实现与可见光成像传感器和红外成像传感器之间的通信,采集雷场的可见光图像和红外图像信息。由于DSPl的EMIF接口是32位,而图像数据的输入字宽为8位,为了充分利用DSP的资源,使系统满足快速传输处理的要求,设计时在传感器和DSPl之间使用4个8位异步FIFO存储器作为图像数据的输入缓冲。FIFO与EMIF之间的硬件接口如图2所示。

图2中的控制逻辑通过图l的CPLDl来实现。CPLD1根据系统所需要的时序,控制产生EMIF的片选信号(CEn)、异步输出允许信号(AOE)、异步写允许信号(AWE)、异步读允许信号(ARE),同时通过接收FIFO的空标志(EF)、满标志(FF)及半满标志(HF)来产生DSP的中断信号(INTx、INTy、INTz),从而实现4个异步FIFO的读写操作。

3.2 GPS数据采集模块

通过各种光学设备拍摄到的雷场图像必须标定上相应的地理坐标信息才能使其具有实际意义。因此,系统的输入数据除了雷场图像数据外还应包含相应的GPS定位数据。

由GPS定位系统根据伪距差分定位原理计算出的GPS定位数据按照整秒输出,输出接口为RS-232型串行接口。TMS320C62xx系列DSP带有3个多通道缓冲串口(McBSP0——McBSP2),考虑到McB-SP串口的电气特性与RS-232串口的电气特性之间存在差异,设计时在DSPI的McBSP接口上外接1个RS-232收发器,以便实现串口通讯,接收GPS定位数据。

3.3 CPLD逻辑控制模块

为了协调系统中每个功能独立的电路高效率工作,使用了2个复杂可编程逻辑器件(CPLD)控制DSP内部多段内存空间的访问,并管理DSP与双口RAM和FIFO之间的访问时序。

此外,由于光学设备的数据输出字宽为8位、TTL电平,而DSP的EMIF接口是32位、LVTTL电平。因此,CPLD还必须通过控制相应的接口电路来解决因光学设备与DSP之间的接口差异而产生的问题,从而保证整个系统有序、高效的运行。

3.4 双口RAM+双DSP图像处理模块

作为图像压缩和存储系统的核心,图像处理模块以双DSP为运算处理核心单元,并辅以双口RAM实现2个DSP之间的高速通信。2个DSP的外部存储器接口EMIF与双口RAM之间的接口设计如图3所示,图中的双口RAM采用的是32位异步RAM。

在图3所示的2个DSP中,DSPl的功能如下:

红外 传感器 GPS DSP CPLD 德州仪器 电路 总线 收发器 IDT 相关文章:

- 基于FPGA的远程图像采集系统设计(11-23)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的二值图像连通域标记快速算法实现(07-24)

- 关于CPLD和接触式图像传感器的图像采集系统(07-26)

- FPGA的光电抗干扰电路设计(08-07)

- StrongARM及其嵌入式应用平台(08-30)