基于FPGA的自然对数变换器的设计与实现

时间:11-09

来源:互联网

点击:

- 后处理单元

由CORD IC得到的z=1/2ln(t),因此将结果左移一位,并截取高16位作为最终的输出。其中最高位为符号位,最大输入值65535的对数值为11.0903,对应的输出为7FFF,其余输出均除以对应的值即得到相应的对数值。

实验结果

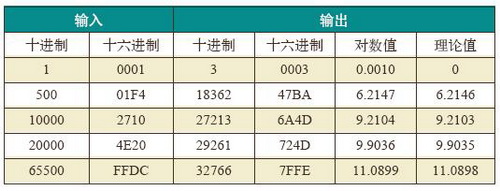

在Quartus II 5.1软件环境下使用Verilog HDL语言完成了上述各算法,并在cyclone系列芯片EP1C6Q240C8上实现。图3 为对数运算时序仿真图。表1为对数运算结果与理论值的比较。

图3对数运算时序仿真图

由表1可看出,该对数运算器的输出误差为10-4数量级。由于采用流水线结构,能够在执行进程的同时输入数据,从而极大的提高了程序的运行效率。该设计需要30个时钟周期获取第一个计算结果,而只需要一个时钟周期来获取随后的计算结果。利用Quartus Ⅱ5.1软件进行时序分析,该运算器的最高频率可达到80MHz。该运算器适用于高速大数据量的数据处理。

表1对数运算结果与理论值的比较

结语

利用对数变换可以将乘除法变换为加减法实现,有利于乘除法在硬件中的实现。由于CORD IC算法完全由移位和相加运算完成,降低了复杂性,易于硬件的实现。笔者利用CORD IC算法在FPGA上设计了一种自然对数变换器。实现过程中采用流水线结构,提高了系统的运行效率。实验结果表明该对数运算器的输出误差为10-4数量级,最高频率可达到80MHz。该运算器适用于高速大数据量的数据处理。

电路 FPGA DSP Altera Quartus Verilog 仿真 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)