基于FPGA的LON网络高速智能节点的设计

时间:11-08

来源:互联网

点击:

3.2 高速智能节点的软件设计

软件设计包括:数据采集和控制。

1) 数据采集软件设计

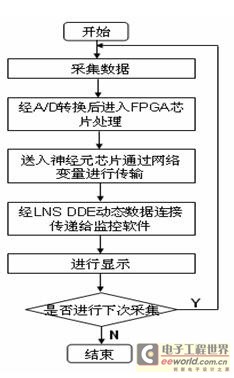

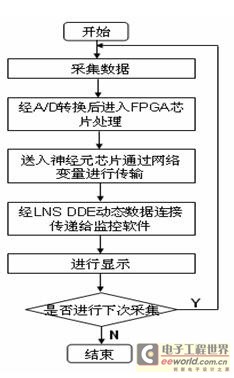

数据采集当上位机发出采集数据指令后,通过网络变量送到相应的节点,然后控制外部传感器执行相应的数据采集指令,并将采集到的数据经 A/D 转换送到神经元芯片,再经过网络变量传递,经 LNS DDE 动态数据连接传递给监控软件,并进行图形化显示给操作者。这一流程可以不断循环进行,直到满足所有条件为止。这一部分的总体流程如图4所示

图4 采集程序的软件流程图

数据采集部分核心软件:本部分的主要功能是将采集到的模拟信号通过电平转换、滤波及多路开关后分成 8 路信号,再进行 A/D 转换变成数字量,经过加工处理后,送至网络数据库,自动改写其中的网络变量的值。

2)控制软件设计

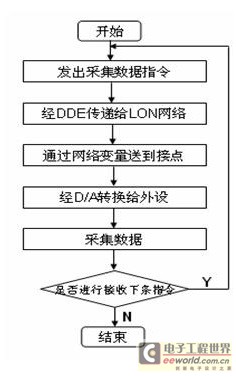

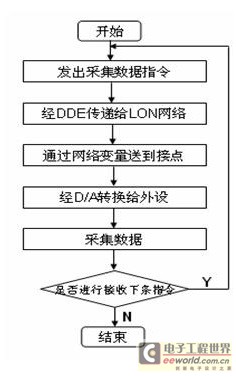

控制软件主要是负责对底层设备的控制。当控制中心在监控软件下发出控制指令,经DDE 传递给 LonWorks 网络,通过网络变量送到对应的节点,在经过 D/A转换,底层设备接收后开始数据采集,然后进行检测是否有下一个控制指令。这一流程也是可不断循环直到满足所有条件为止。这一部分的总体流程如图5所示。

图5 控制程序的软件流程图

3.3 实验结果

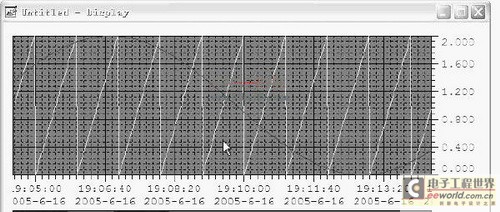

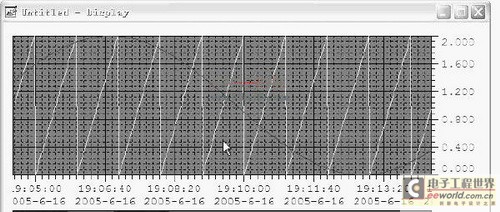

输入一正弦波,周期为1s,得到如图6示结果:

图6 实验结果

4 结束语

本设计成功的实现了利用FPGA芯片作为LON网络智能节点的主处理器,并且采用双口RAM实现了主处理器与NEURON芯片之间的数据传递。本系统适合大多数数据采集场合,能达到通用和高速的目的。

采用FPGA进行设计可缩短开发生产周期,而且现场灵活性好,它不但包括了MCU这一特点,而且可触及硅片电路的物理界限,并兼有串、并行工作方式,高速、高可靠性以及宽口径适用性等诸多方面的特点。因此,利用基于FPGA的LON网络的高速智能节点的设计具有一定的实际意义和价值。

软件设计包括:数据采集和控制。

1) 数据采集软件设计

数据采集当上位机发出采集数据指令后,通过网络变量送到相应的节点,然后控制外部传感器执行相应的数据采集指令,并将采集到的数据经 A/D 转换送到神经元芯片,再经过网络变量传递,经 LNS DDE 动态数据连接传递给监控软件,并进行图形化显示给操作者。这一流程可以不断循环进行,直到满足所有条件为止。这一部分的总体流程如图4所示

图4 采集程序的软件流程图

数据采集部分核心软件:本部分的主要功能是将采集到的模拟信号通过电平转换、滤波及多路开关后分成 8 路信号,再进行 A/D 转换变成数字量,经过加工处理后,送至网络数据库,自动改写其中的网络变量的值。

2)控制软件设计

控制软件主要是负责对底层设备的控制。当控制中心在监控软件下发出控制指令,经DDE 传递给 LonWorks 网络,通过网络变量送到对应的节点,在经过 D/A转换,底层设备接收后开始数据采集,然后进行检测是否有下一个控制指令。这一流程也是可不断循环直到满足所有条件为止。这一部分的总体流程如图5所示。

图5 控制程序的软件流程图

3.3 实验结果

输入一正弦波,周期为1s,得到如图6示结果:

图6 实验结果

4 结束语

本设计成功的实现了利用FPGA芯片作为LON网络智能节点的主处理器,并且采用双口RAM实现了主处理器与NEURON芯片之间的数据传递。本系统适合大多数数据采集场合,能达到通用和高速的目的。

采用FPGA进行设计可缩短开发生产周期,而且现场灵活性好,它不但包括了MCU这一特点,而且可触及硅片电路的物理界限,并兼有串、并行工作方式,高速、高可靠性以及宽口径适用性等诸多方面的特点。因此,利用基于FPGA的LON网络的高速智能节点的设计具有一定的实际意义和价值。

总线 传感器 收发器 单片机 DSP ADC 电路 FPGA MCU 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)