基于FPGA的LON网络高速智能节点的设计

时间:11-08

来源:互联网

点击:

1 概述

LonWorks现场总线(简称LON总线)是美国Echelon公司推出的局部操作网络,为集散式监控系统提供了很强的实现手段,成为当今流行的现场总线技术之一。现在的测控系统中,连接在现场总线网络上的每一个节点,即传感器、变送器、执行器等都不再是单功能的传统仪表,而是具有数据采集、转换、控制、计算、报警、诊断及数字通讯等功能的智能化设备(智能节点)连接在网络上的各种智能现场设备共享总线信道,进行数据和信息交换,相互协调工作组成一个完整的现场总线控制系统。LON总线技术使用开放式的通信协议LonTalk,为设备之间交换控制状态信息建立了一个通用标准并,在硬件芯片的支持下实现了实时性和接口的直观、简洁的现场总线的应用要求。在LON总线技术中所有节点都包括一个用以实现通信管理、输入、输出和控制等功能的神经元芯片(Neuron Chip)-- LON总线技术的核心,它不仅是LON总线的通信处理器,也是数据采集和控制的通用处理器,LON总线技术中所有网络的操作实际上都是通过它来完成的。因此网络中节点的设计是实现LON总线技术的一个关键所在。

2 智能节点开发的一般方法

智能节点是控制网络中分布在现场级的基本智能单元,主要用于接受和处理来自传感器的输入数据,执行通信和控制任务以及控制执行起操作等。智能节点中的核心技术是LONTALK协议和神经元芯片。智能节点的开发分为两类:一类是利用神经元芯片完成所有的工作(包括通信和用户应用程序),节点中不再包含其他处理器。这类智能节点成为基于神经元芯片的节点。另一类是只利用神经元芯片完成通信工作,而用户的应用程序由其他的处理器(如微处理器、微控制器或PC机来完成)这种智能节点成为基于主机的节点。

(1) 以Neuron 芯片为核心的控制节点

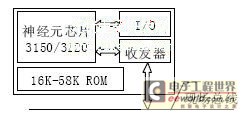

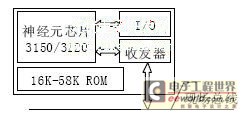

图1为以Neuron芯片为核心的控制节点的结构框图。

神经元芯片是一组复杂的VLSI器件,通过独特的硬件固件相结合技术,使一个Neuron芯片几乎包含一个现场节点的大部分功能若加上收发器就可以构成一个典型的现场控制节点。

此设计方法由于Neuron芯片是8位总线,目前只支持最高主频是10MHz,因此它能完成的功能也十分有限,对于一些复杂的控制如带有PID算法的单回路多回路的控制就显得力不从心。且其片载操作系统基于一种巡检机制,不太适合于实时性很强的控制节点。

图1 以Neuron芯片为核心的控制节点结构

(2) 采用MIP结构的控制节点

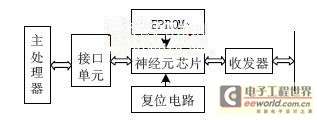

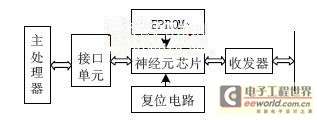

图2为Host Base结构的节点框图。鉴于方法(1)的缺点,采用MIP结构是解决这一问题的好办法,将Neuron芯片作为通信协处理器,用高级主机(上位管理机)的资源来完成复杂的测控功能。

图2 采用MIP结构的控制节点结构

对于这种方法,由于高级主机(上位管理机)和各智能节点间,属于多对一通信,当节点增多时,容易引起网络的阻塞,且一旦发生网络阻塞,网络上的数据传输效率将显著降低。

此外,现有大多LON网络的智能节点应用中,数据采集系统通常采用单片机或DSP(数字信号处理器)作为CPU,控制ADC(模/数转换器)、存储器和其他外围电路的工作。但是单片机的时钟频率较低,难以适应高速数据采集系统的要求,而DSP虽然可以实现较高速的数据采集,但其速度提高的同时也提高了系统的成本。FPGA(现场可编程门阵列)有单片机和DSP无法比拟的优势:时钟频率高,内部时延小;全部控制逻辑由硬件完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

3 高速智能节点的设计

3.1高速智能节点的硬件系统结构设计

该高速智能节点是基于FPGA架构来设计的。FPGA是整个系统的控制中心和数据交换桥梁,而且能够实现对底层的信号快速预处理,在很多信号处理系统中,底层的信号预处理算法要处理的数据量很大,对处理速度要求很高,但算法结构相对比较简单,适于用FPGA进行硬件编程实现。

系统的原理框图如图3所示。

图3 通用高速智能节点总体结构框图

整个高速数据采集处理系统的主要硬件构成为:

1)ACEX1K系列EP1K30TC144-3:主处理器,是整个系统的控制中心和数据处理中心,特点是电路连接I/O口多,速度快;

2)AD9288:实现4路8位采样,最高采样频率为100 MSPS,适合应用与高速信号测量仪器;;

3)Neuron芯片:通信协处理器,负责通信功能

4)双口RAM:主处理器与通信协处理器的接口,实现数据交换;

5)收发器FTT-10A:将数据传递至LON总线。

在控制台发出采集指令或定时器的作用下,模拟输入经AD采样进入FPGA,经过FPGA里的信号处理模块和算法处理后存入RAM,经Neuron芯片读出至LON网络。

LonWorks现场总线(简称LON总线)是美国Echelon公司推出的局部操作网络,为集散式监控系统提供了很强的实现手段,成为当今流行的现场总线技术之一。现在的测控系统中,连接在现场总线网络上的每一个节点,即传感器、变送器、执行器等都不再是单功能的传统仪表,而是具有数据采集、转换、控制、计算、报警、诊断及数字通讯等功能的智能化设备(智能节点)连接在网络上的各种智能现场设备共享总线信道,进行数据和信息交换,相互协调工作组成一个完整的现场总线控制系统。LON总线技术使用开放式的通信协议LonTalk,为设备之间交换控制状态信息建立了一个通用标准并,在硬件芯片的支持下实现了实时性和接口的直观、简洁的现场总线的应用要求。在LON总线技术中所有节点都包括一个用以实现通信管理、输入、输出和控制等功能的神经元芯片(Neuron Chip)-- LON总线技术的核心,它不仅是LON总线的通信处理器,也是数据采集和控制的通用处理器,LON总线技术中所有网络的操作实际上都是通过它来完成的。因此网络中节点的设计是实现LON总线技术的一个关键所在。

2 智能节点开发的一般方法

智能节点是控制网络中分布在现场级的基本智能单元,主要用于接受和处理来自传感器的输入数据,执行通信和控制任务以及控制执行起操作等。智能节点中的核心技术是LONTALK协议和神经元芯片。智能节点的开发分为两类:一类是利用神经元芯片完成所有的工作(包括通信和用户应用程序),节点中不再包含其他处理器。这类智能节点成为基于神经元芯片的节点。另一类是只利用神经元芯片完成通信工作,而用户的应用程序由其他的处理器(如微处理器、微控制器或PC机来完成)这种智能节点成为基于主机的节点。

(1) 以Neuron 芯片为核心的控制节点

图1为以Neuron芯片为核心的控制节点的结构框图。

神经元芯片是一组复杂的VLSI器件,通过独特的硬件固件相结合技术,使一个Neuron芯片几乎包含一个现场节点的大部分功能若加上收发器就可以构成一个典型的现场控制节点。

此设计方法由于Neuron芯片是8位总线,目前只支持最高主频是10MHz,因此它能完成的功能也十分有限,对于一些复杂的控制如带有PID算法的单回路多回路的控制就显得力不从心。且其片载操作系统基于一种巡检机制,不太适合于实时性很强的控制节点。

图1 以Neuron芯片为核心的控制节点结构

(2) 采用MIP结构的控制节点

图2为Host Base结构的节点框图。鉴于方法(1)的缺点,采用MIP结构是解决这一问题的好办法,将Neuron芯片作为通信协处理器,用高级主机(上位管理机)的资源来完成复杂的测控功能。

图2 采用MIP结构的控制节点结构

对于这种方法,由于高级主机(上位管理机)和各智能节点间,属于多对一通信,当节点增多时,容易引起网络的阻塞,且一旦发生网络阻塞,网络上的数据传输效率将显著降低。

此外,现有大多LON网络的智能节点应用中,数据采集系统通常采用单片机或DSP(数字信号处理器)作为CPU,控制ADC(模/数转换器)、存储器和其他外围电路的工作。但是单片机的时钟频率较低,难以适应高速数据采集系统的要求,而DSP虽然可以实现较高速的数据采集,但其速度提高的同时也提高了系统的成本。FPGA(现场可编程门阵列)有单片机和DSP无法比拟的优势:时钟频率高,内部时延小;全部控制逻辑由硬件完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

3 高速智能节点的设计

3.1高速智能节点的硬件系统结构设计

该高速智能节点是基于FPGA架构来设计的。FPGA是整个系统的控制中心和数据交换桥梁,而且能够实现对底层的信号快速预处理,在很多信号处理系统中,底层的信号预处理算法要处理的数据量很大,对处理速度要求很高,但算法结构相对比较简单,适于用FPGA进行硬件编程实现。

系统的原理框图如图3所示。

图3 通用高速智能节点总体结构框图

整个高速数据采集处理系统的主要硬件构成为:

1)ACEX1K系列EP1K30TC144-3:主处理器,是整个系统的控制中心和数据处理中心,特点是电路连接I/O口多,速度快;

2)AD9288:实现4路8位采样,最高采样频率为100 MSPS,适合应用与高速信号测量仪器;;

3)Neuron芯片:通信协处理器,负责通信功能

4)双口RAM:主处理器与通信协处理器的接口,实现数据交换;

5)收发器FTT-10A:将数据传递至LON总线。

在控制台发出采集指令或定时器的作用下,模拟输入经AD采样进入FPGA,经过FPGA里的信号处理模块和算法处理后存入RAM,经Neuron芯片读出至LON网络。

总线 传感器 收发器 单片机 DSP ADC 电路 FPGA MCU 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)