使用Xilinx FPGA适应不断变化的广播视频潮流

时间:10-23

来源:互联网

点击:

电视台的演播室需要在不替换庞大的以同轴电缆构建的基础架构的情况下,将模拟音频和视频转换为数字音频和视频,这样就逐渐形成了传输非压缩标清视频的串行数字接口(SDI)协议。如今,出于重新利用同轴电缆的同样目的,日益增长的屏幕分辨率和相关数据速率衍生出了若干新的串行数据通信格式。

首先出现的是SDI标准,通常称为SMPTE 259M标准,这是由电影与电视工程师协会(SMPTE)制定的,于1989年开始商业应用。在最初推出之际,用于接口的主要芯片是由ASSP芯片制造商提供的。SDI名义上的数据速率是270Mbps,足够满足标清电视(SDTV)的分辨率。

在2002年,Xilinx对业界宣布即将推出Virtex-II Pro FPGA。这一器件的显著的特点是包含多个千兆位级收发器(MGT),这些收发器能够以高达3.125Gbps的比特率运行。与此同时,电视台的演播室开始采用新的高清晰度电视(HDTV)标准,此标准能够满足更高屏幕分辨率和更快数据速率的要求。SMPTE又制定了通常称为SMPTE 292M的标准,支持非压缩的HDTV视频内容的串行传输,其名义速率为1.5Gbps,其通常被称作HD-SDI标准。

Xilinx高级资深应用工程师John Snow意识到,这两种数据速率用单个Virtex-II Pro MGT即可支持,由此而发现了将多个ASSP芯片集成到单个Xilinx FPGA中的良机。该集成将大大降低接口的成本费用,尤其是对于含有多个视频流的视频切换器和主控制器的设计。

Snow为使用FPGA的这两种接口标准制定了第一批应用指南。这些应用指南包括用Verilog和VHDL源代码编写的免费参考设计。使用该代码和技术文档,广播系统工程师可毫不费力地在Virtex-II Pro FPGA中实现功能齐全的SDI和HD-SDI接收器和发射器,以及其他相关的功能,如视频测试模式生成器。第二年,将多个ASSP芯片集中在一起的Virtex-II ProFPGA,开始出现在全球的广播设备中。

消费者越来越认同HDTV。这一令人惊叹的技术使电视观众更接近真实世界,因此HD内容总量会越来越多。如今,高清接收器实现了规模市场价格,消费者对HDTV的兴趣越来越大。多速率SDI和HD-SDI参考设计对广播电台演播室的数字音频和视频内容的分发来说日益重要。

如今,SMPTE组织并未停下脚步。他们不断发布新标准,以满足对更高带宽的视频格式要求。两个最新发布的标准为双连接HD-SDI(SMPTE 372M)和3G-SDI(SMPTE 424M和SMPTE 425M)标准,二者都提供3Gbps的总带宽。

双连接HD-SDI标准使用两个HD-SDI速率链路,二者合力以提供更丰富颜色的传输(更多像素的颜色数据)或者更快的更新率(1080行,帧频60Hz逐行扫描,而不是帧频30Hz)。构成双连接HD-SDI接口的两条同轴电缆,如使用3G-SDI标准,仅用一条同轴电缆就可代替。

需要更高数据速率的一个应用示例是电影业向数字数据的转移。与通常HDTV格式使用的每个视频象素20位数据相比,数字电影标准使用每个视频象素36位数据。每视频象素位的增加,再加上更高的屏幕分辨率,导致了市场对以3Gbps运行的数字接口的需求。

即使是在SMPTE制定的单个标准中,FPGA也有诸多机会适应未来的发展变化。3G-SDI确切地说是通过两个标准来定义的:SMPTE 424M标准和SMPTE 425M标准。SMPTE 424M标准规定了串行接口本身的物理和电特性。而SMPTE 425M规定了如何将各种视频格式映射到接口中。虽然SMPTE 425M标准的发表是近在2006年的事,SMPTE已着手开始修改此标准使其支持其他的视频格式。

SMPTE组织定义了以10Gbps运行的接口,并正在设想运行速度更快的接口。使用Xilinx FPGA设计这些接口消除了由于标准的快速演化,新设计的视频设备未及面世就会过时的风险。

让我们看一下使用HD-SDI视频连接的几个新兴应用。

1 CCD摄像机与VoIP应用

超高速、超高灵敏度广播摄像机能够捕获清晰、平滑、可慢动作回放的视频(即使在低光照的环境下),对录制夜间职业棒球比赛之类的活动极其有用。这种摄像机能把快速移动的现象(如球棒击球瞬间的系列动作)拍摄下来,而普通肉眼则难以企及。以慢动作播放这些事件能大大改善电视观众的体验。

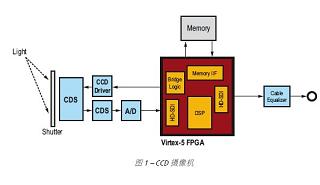

如图1所示的电荷耦合器件(CCD)摄像机使用FPGA实现信号综合处理和颜色处理,并连接到CCD驱动器。CCD驱动器反过来驱使CCD、机械快门控制并触发控制。模数转换器将输入视频信号转换成数字格式,然后将其存储到片外存储器。当整帧数据的传输完成后,FPGA将存储器中的数据综合,并使用HD-SDI标准将其发送到网络中。从触发到HD-SDI输出所需的处理时间为1秒或更少。FPGA还可控制存储器和ADC(模数转换器)。

首先出现的是SDI标准,通常称为SMPTE 259M标准,这是由电影与电视工程师协会(SMPTE)制定的,于1989年开始商业应用。在最初推出之际,用于接口的主要芯片是由ASSP芯片制造商提供的。SDI名义上的数据速率是270Mbps,足够满足标清电视(SDTV)的分辨率。

在2002年,Xilinx对业界宣布即将推出Virtex-II Pro FPGA。这一器件的显著的特点是包含多个千兆位级收发器(MGT),这些收发器能够以高达3.125Gbps的比特率运行。与此同时,电视台的演播室开始采用新的高清晰度电视(HDTV)标准,此标准能够满足更高屏幕分辨率和更快数据速率的要求。SMPTE又制定了通常称为SMPTE 292M的标准,支持非压缩的HDTV视频内容的串行传输,其名义速率为1.5Gbps,其通常被称作HD-SDI标准。

Xilinx高级资深应用工程师John Snow意识到,这两种数据速率用单个Virtex-II Pro MGT即可支持,由此而发现了将多个ASSP芯片集成到单个Xilinx FPGA中的良机。该集成将大大降低接口的成本费用,尤其是对于含有多个视频流的视频切换器和主控制器的设计。

Snow为使用FPGA的这两种接口标准制定了第一批应用指南。这些应用指南包括用Verilog和VHDL源代码编写的免费参考设计。使用该代码和技术文档,广播系统工程师可毫不费力地在Virtex-II Pro FPGA中实现功能齐全的SDI和HD-SDI接收器和发射器,以及其他相关的功能,如视频测试模式生成器。第二年,将多个ASSP芯片集中在一起的Virtex-II ProFPGA,开始出现在全球的广播设备中。

消费者越来越认同HDTV。这一令人惊叹的技术使电视观众更接近真实世界,因此HD内容总量会越来越多。如今,高清接收器实现了规模市场价格,消费者对HDTV的兴趣越来越大。多速率SDI和HD-SDI参考设计对广播电台演播室的数字音频和视频内容的分发来说日益重要。

如今,SMPTE组织并未停下脚步。他们不断发布新标准,以满足对更高带宽的视频格式要求。两个最新发布的标准为双连接HD-SDI(SMPTE 372M)和3G-SDI(SMPTE 424M和SMPTE 425M)标准,二者都提供3Gbps的总带宽。

双连接HD-SDI标准使用两个HD-SDI速率链路,二者合力以提供更丰富颜色的传输(更多像素的颜色数据)或者更快的更新率(1080行,帧频60Hz逐行扫描,而不是帧频30Hz)。构成双连接HD-SDI接口的两条同轴电缆,如使用3G-SDI标准,仅用一条同轴电缆就可代替。

需要更高数据速率的一个应用示例是电影业向数字数据的转移。与通常HDTV格式使用的每个视频象素20位数据相比,数字电影标准使用每个视频象素36位数据。每视频象素位的增加,再加上更高的屏幕分辨率,导致了市场对以3Gbps运行的数字接口的需求。

即使是在SMPTE制定的单个标准中,FPGA也有诸多机会适应未来的发展变化。3G-SDI确切地说是通过两个标准来定义的:SMPTE 424M标准和SMPTE 425M标准。SMPTE 424M标准规定了串行接口本身的物理和电特性。而SMPTE 425M规定了如何将各种视频格式映射到接口中。虽然SMPTE 425M标准的发表是近在2006年的事,SMPTE已着手开始修改此标准使其支持其他的视频格式。

SMPTE组织定义了以10Gbps运行的接口,并正在设想运行速度更快的接口。使用Xilinx FPGA设计这些接口消除了由于标准的快速演化,新设计的视频设备未及面世就会过时的风险。

让我们看一下使用HD-SDI视频连接的几个新兴应用。

1 CCD摄像机与VoIP应用

超高速、超高灵敏度广播摄像机能够捕获清晰、平滑、可慢动作回放的视频(即使在低光照的环境下),对录制夜间职业棒球比赛之类的活动极其有用。这种摄像机能把快速移动的现象(如球棒击球瞬间的系列动作)拍摄下来,而普通肉眼则难以企及。以慢动作播放这些事件能大大改善电视观众的体验。

如图1所示的电荷耦合器件(CCD)摄像机使用FPGA实现信号综合处理和颜色处理,并连接到CCD驱动器。CCD驱动器反过来驱使CCD、机械快门控制并触发控制。模数转换器将输入视频信号转换成数字格式,然后将其存储到片外存储器。当整帧数据的传输完成后,FPGA将存储器中的数据综合,并使用HD-SDI标准将其发送到网络中。从触发到HD-SDI输出所需的处理时间为1秒或更少。FPGA还可控制存储器和ADC(模数转换器)。

图1:电荷耦合器件(CCD)摄像机使用FPGA实现信

Xilinx FPGA 收发器 Verilog VHDL ADC 嵌入式 DSP 解码器 编码器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)