第三代非易失FPGA给予片上系统更多的功能

时间:09-21

来源:互联网

点击:

针对可靠性的双引导方案

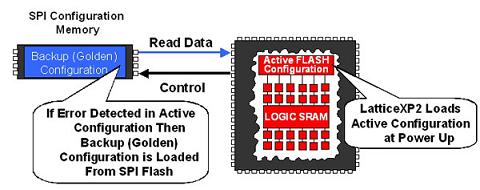

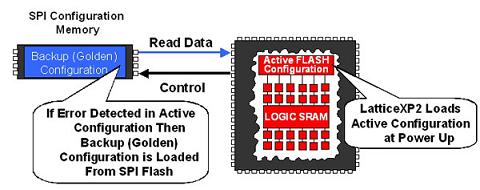

存储的FPGA配置被更新时,存在着电源或者通信失败的风险,会导致不可靠的配置和系统停止工作。如果发生了这种情况,拜访技术员和纠正差错都是不小的开支。为了防止发生此类问题,LatticeXP2器件可以使用外部的SPI存储器来实现双引导方案。

如图9所示,上电时LatticeXP2试图从片上Flash载入SRAM配置位。如果在这个过程中检测到错误,于是FPGA从外部的SPI存储器读取备份或者重要的配置。用这种方法运行系统,能够可靠地进行更新而不管电源或者通信故障。

图9 高可靠现场更新的双引导方法

用于设计安全的128位加密

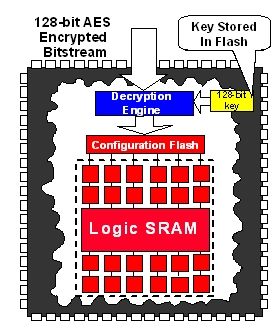

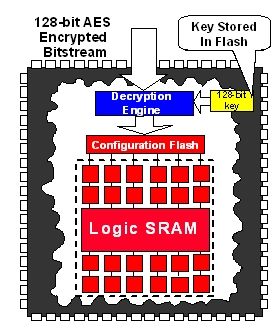

LatticeXP2器件能用可选的128位AES编程数据加密。器件收到加密数据时,用片上的解密引擎进行解密,解密引擎

是用户定义的用Flash存储器存储在片上的密钥。基本的操作如图10所示。这种运作模式使得在现场更新期间敏感的设计数据得到了保护。

图10 基本的操作

本文小结

设计者选择非易失器件的主要原因仍然未变,这些原因是小的尺寸、瞬时以及高可靠性。然而对非易失数据存储和全面的现场更新解决方案的新要求正在兴起。所有这些新要求都必须满足,而且,相对于传统的SRAM解决方案,非易失解决方案的额外费用是最小的。

如今有两种方法提供非易失FPGA:混合的和单片的。混合方法主要是解决小尺寸的要求。而真正的单片非易失方法满足了小尺寸、瞬时和高安全性的要求。

采用90纳米嵌入式Flash工艺,LatticeXP2 FPGA满足了选择非易失器件的主要和新兴的原因,同时还降低了成本。

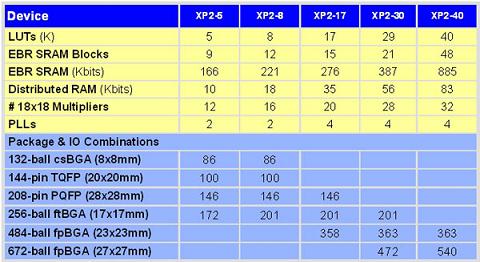

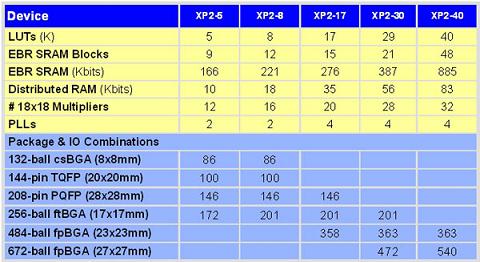

表1 LatticeXP2 FPGA 系列

存储的FPGA配置被更新时,存在着电源或者通信失败的风险,会导致不可靠的配置和系统停止工作。如果发生了这种情况,拜访技术员和纠正差错都是不小的开支。为了防止发生此类问题,LatticeXP2器件可以使用外部的SPI存储器来实现双引导方案。

如图9所示,上电时LatticeXP2试图从片上Flash载入SRAM配置位。如果在这个过程中检测到错误,于是FPGA从外部的SPI存储器读取备份或者重要的配置。用这种方法运行系统,能够可靠地进行更新而不管电源或者通信故障。

图9 高可靠现场更新的双引导方法

用于设计安全的128位加密

LatticeXP2器件能用可选的128位AES编程数据加密。器件收到加密数据时,用片上的解密引擎进行解密,解密引擎

是用户定义的用Flash存储器存储在片上的密钥。基本的操作如图10所示。这种运作模式使得在现场更新期间敏感的设计数据得到了保护。

图10 基本的操作

本文小结

设计者选择非易失器件的主要原因仍然未变,这些原因是小的尺寸、瞬时以及高可靠性。然而对非易失数据存储和全面的现场更新解决方案的新要求正在兴起。所有这些新要求都必须满足,而且,相对于传统的SRAM解决方案,非易失解决方案的额外费用是最小的。

如今有两种方法提供非易失FPGA:混合的和单片的。混合方法主要是解决小尺寸的要求。而真正的单片非易失方法满足了小尺寸、瞬时和高安全性的要求。

采用90纳米嵌入式Flash工艺,LatticeXP2 FPGA满足了选择非易失器件的主要和新兴的原因,同时还降低了成本。

表1 LatticeXP2 FPGA 系列

FPGA 电路 半导体 传感器 电子 总线 嵌入式 DSP 滤波器 CMOS 电阻 振荡器 电压 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)