Virtex-5 FXT平台背景资料

时间:09-25

来源:互联网

点击:

Virtex-5 FXT FPGA – 终极系统集成平台

由于众多不断增加和演化的标准、苛刻的处理要求以及不断降低的成本和时间预算,数字融合时代加速了对FPGA基本价值主张的依赖性。这些基本价值主张是:灵活性、现场可升级能力、优异的信号处理能力、更快的产品上市时间、降低风险、适应不断演化的标准以及降低系统成本。 Virtex?-5平台建立在这些丰富价值的基础上,再加上高速串行连接功能和嵌入式处理能力,从而构成了终极系统集成平台。

Virtex-5 FXT平台是唯一结合了业界标准的550MHz PowerPC? 440嵌入式处理器内核、DSP和高速串行I/O功能的FPGA,其无与伦比的系统集成度可更好地支持通信、音频视频广播、军事和航空、工业、科学以及医疗市场中的高性能应用。利用Virtex-5 FXT平台,此类应用的设计人员可以提高整体系统性能、最小化电路板复杂度并降低系统成本。

Virtex-5系列

无论在产品可用性还是为客户提供的多种选择方面, Virtex-5系列FPGA平台都是业界领先的高密度65nm FPGA产品。Virtex-5系列是Virtex系列FPGA的第5代产品。基于其独特的ASMBL架构,Virtex-5系列提供了四个领域优化的平台共24款器件供客户选择:

该系列器件提供了一系列创新的特性,包括:

Virtex-5 FXT平台增加的系统集成主要特性包括:

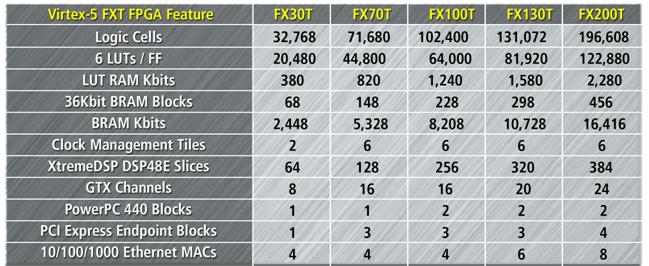

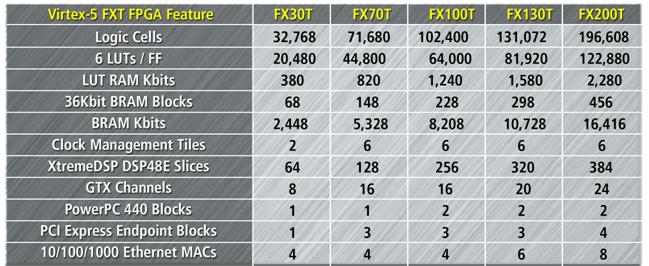

表1:Virtex-5 FXT产品一览

PowerPC 440处理器模块

PowerPC 440处理器已经广泛应用于赛灵思公司高密度FPGA所面向的细分市场中的众多系统应用中,并且经受了测试和验证。Virtex-5 FXT FPGA率先提供了同时符合两个业界标准的PowerPC 440处理器,其增强的系统性能可支持设计人员快速容易地实现先进的可升级嵌入式处理应用。每个处理器集成32KB指令和32KB数据缓存,在550MHz时钟下可以提供高达1,100 DMIPS的性能。

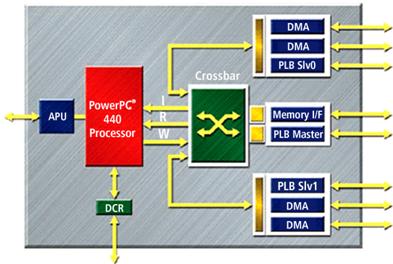

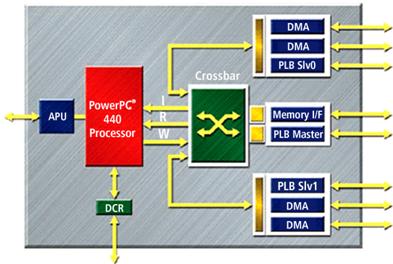

大幅提高系统处理性能的关键是通过多通道、高效、并发高速数据访问来提高总体数据吞吐能力。为达到这一目的,新集成的5x2 纵横交换式处理器互连架构与PowerPC 440处理器紧密耦合,提供并发I/O和存储器访问能力(图1)。这一高度集成的架构支持5个主PLB(处理器局部总线)接口和两个从接口、四个独立收发全双工信道DMA端口和一个专用存储器总线接口,因此存储器带宽最高可达此前解决方案的5倍。在新的硬核化纵横交换式架构管理下,系统支持并发访问多个128位总线(原来为64位)的数据,从而进一步扩大系统吞吐能力。先进的PLB架构支持高吞吐量128位接口,可缩小系统瓶颈,从而最大化处理器、纵横开关式交换构造以及软IP逻辑之间的数据传输能力。

图 1.PowerPC 440模块包括PowerPC 440内核和新的互连架构

与这一新架构形成互补的是,这一平台集成的增强高性能辅助处理器控制单元(APU)接口允许用户可以构造辅助处理器来执行非PowerPC 440指令集的指令。这样就为视频处理、3D数据处理和浮点算术等应用中的专用协处理引擎或用户专用定制指南提供了支持。

高速串行连接能力

Virtex-5 FXT平台支持最热门的数字I/O和数千兆位(multi-gigabit)串行I/O技术,提供多达24个全功能RocketIO? 千兆级收发器(GTX)。这些增强的收发器现在可以支持从500Mbps到6.5Gbps的数据速率。Virtex-5 FXT GTX收发器是目前Virtex-5系列中速度最快的,不仅扩展了Virtex-5 LXT和SXT FPGA中得到验证的收发器架构,同时也方便了在Virtex-5 LXT、SXT & FXT平台间的设计移植。

在附加高数据速率性能的同时6.5Gbps速率时每通道消耗的典型功耗只有200mW。当运行在较低的3.75 Gbps速率时,每通道功耗仅100mW。

除了更高的串行I/O性能以外,还增强了一些其它关键特性。为提高这些高速信号的信号完整性,集成了4抽头决策反馈均衡器(DFE)、线性均衡器和发送预加重补偿。决策反馈均衡器(DFE)是一种非线性均衡器,利用前检测决策来消除当前解调脉冲的符号间干扰(ISI)。DFE的优点是其工作在无噪声的量化电平上,因此其输出与信道噪声无关。

GTX收发器提供了一种新的灵活速率变换器,或变速箱,支持主要领先协议的8B/10B, 64B/66B 和 64B/67B编码和同步。独立的发送和接收数据流支持全双工操作。

用于PCI Express?、Gigabit Ethernet 和 XAUI的完整协议包为设计成功提供了一个低风险的路径。该协议包还可为SONET OC-48/SDH STM-16 和 CPRI (Common Public Radio Interface)提供专用协议参数报告,从而能够在采用新的串行协议时更有信心。每一标准协议包都包括针对特定协议物理层的特性描述报告、互操作性和兼容性报告、知识产权(IP)内核以及技术文档,支持用户高效且低风险地在Virtex?-5 FPGA中实现标准的高速串行协议。

由于众多不断增加和演化的标准、苛刻的处理要求以及不断降低的成本和时间预算,数字融合时代加速了对FPGA基本价值主张的依赖性。这些基本价值主张是:灵活性、现场可升级能力、优异的信号处理能力、更快的产品上市时间、降低风险、适应不断演化的标准以及降低系统成本。 Virtex?-5平台建立在这些丰富价值的基础上,再加上高速串行连接功能和嵌入式处理能力,从而构成了终极系统集成平台。

Virtex-5 FXT平台是唯一结合了业界标准的550MHz PowerPC? 440嵌入式处理器内核、DSP和高速串行I/O功能的FPGA,其无与伦比的系统集成度可更好地支持通信、音频视频广播、军事和航空、工业、科学以及医疗市场中的高性能应用。利用Virtex-5 FXT平台,此类应用的设计人员可以提高整体系统性能、最小化电路板复杂度并降低系统成本。

Virtex-5系列

无论在产品可用性还是为客户提供的多种选择方面, Virtex-5系列FPGA平台都是业界领先的高密度65nm FPGA产品。Virtex-5系列是Virtex系列FPGA的第5代产品。基于其独特的ASMBL架构,Virtex-5系列提供了四个领域优化的平台共24款器件供客户选择:

- LX – 针对逻辑应用领域而优化

- LXT – 针对支持低功耗串行连接逻辑应用领域而优化

- SXT – 针对支持串行连接的DSP应用领域而优化

- FXT – 针对支持高速串行连接的嵌入式处理应用领域而优化

该系列器件提供了一系列创新的特性,包括:

- 新的CLB和增强的布线技术支持超快ExpressFabric? 技术

- LXT、SXT和FXT平台提供完全集成的PCI Express? 端点模块

- LXT、SXT、FXT平台提供完全集成的三模式(0/100/1000 Mbps)以太网MAC模块

- 提供ECC选择的36Kbit 双端口BRAM/FIFO模块

- 带PLL 的550Mhz时钟管理管道(CMT)

- 支持ChipSync技术的SelectIO

- 第二代稀疏锯齿形(Sparse Chevron) 封装技术支持增强引脚输出功能

- 多位流管理和多种细粒度帧尺寸方便进行部分重配置

Virtex-5 FXT平台增加的系统集成主要特性包括:

- 完全集成的PowerPC 440处理器模块和128位互连

- 高性能GTX 6.5 Gbps 串行 I/O

- XtremeDSP? 逻辑片 (DSP48E逻辑片)优化组合

表1:Virtex-5 FXT产品一览

PowerPC 440处理器模块

PowerPC 440处理器已经广泛应用于赛灵思公司高密度FPGA所面向的细分市场中的众多系统应用中,并且经受了测试和验证。Virtex-5 FXT FPGA率先提供了同时符合两个业界标准的PowerPC 440处理器,其增强的系统性能可支持设计人员快速容易地实现先进的可升级嵌入式处理应用。每个处理器集成32KB指令和32KB数据缓存,在550MHz时钟下可以提供高达1,100 DMIPS的性能。

大幅提高系统处理性能的关键是通过多通道、高效、并发高速数据访问来提高总体数据吞吐能力。为达到这一目的,新集成的5x2 纵横交换式处理器互连架构与PowerPC 440处理器紧密耦合,提供并发I/O和存储器访问能力(图1)。这一高度集成的架构支持5个主PLB(处理器局部总线)接口和两个从接口、四个独立收发全双工信道DMA端口和一个专用存储器总线接口,因此存储器带宽最高可达此前解决方案的5倍。在新的硬核化纵横交换式架构管理下,系统支持并发访问多个128位总线(原来为64位)的数据,从而进一步扩大系统吞吐能力。先进的PLB架构支持高吞吐量128位接口,可缩小系统瓶颈,从而最大化处理器、纵横开关式交换构造以及软IP逻辑之间的数据传输能力。

图 1.PowerPC 440模块包括PowerPC 440内核和新的互连架构

与这一新架构形成互补的是,这一平台集成的增强高性能辅助处理器控制单元(APU)接口允许用户可以构造辅助处理器来执行非PowerPC 440指令集的指令。这样就为视频处理、3D数据处理和浮点算术等应用中的专用协处理引擎或用户专用定制指南提供了支持。

高速串行连接能力

Virtex-5 FXT平台支持最热门的数字I/O和数千兆位(multi-gigabit)串行I/O技术,提供多达24个全功能RocketIO? 千兆级收发器(GTX)。这些增强的收发器现在可以支持从500Mbps到6.5Gbps的数据速率。Virtex-5 FXT GTX收发器是目前Virtex-5系列中速度最快的,不仅扩展了Virtex-5 LXT和SXT FPGA中得到验证的收发器架构,同时也方便了在Virtex-5 LXT、SXT & FXT平台间的设计移植。

在附加高数据速率性能的同时6.5Gbps速率时每通道消耗的典型功耗只有200mW。当运行在较低的3.75 Gbps速率时,每通道功耗仅100mW。

除了更高的串行I/O性能以外,还增强了一些其它关键特性。为提高这些高速信号的信号完整性,集成了4抽头决策反馈均衡器(DFE)、线性均衡器和发送预加重补偿。决策反馈均衡器(DFE)是一种非线性均衡器,利用前检测决策来消除当前解调脉冲的符号间干扰(ISI)。DFE的优点是其工作在无噪声的量化电平上,因此其输出与信道噪声无关。

GTX收发器提供了一种新的灵活速率变换器,或变速箱,支持主要领先协议的8B/10B, 64B/66B 和 64B/67B编码和同步。独立的发送和接收数据流支持全双工操作。

用于PCI Express?、Gigabit Ethernet 和 XAUI的完整协议包为设计成功提供了一个低风险的路径。该协议包还可为SONET OC-48/SDH STM-16 和 CPRI (Common Public Radio Interface)提供专用协议参数报告,从而能够在采用新的串行协议时更有信心。每一标准协议包都包括针对特定协议物理层的特性描述报告、互操作性和兼容性报告、知识产权(IP)内核以及技术文档,支持用户高效且低风险地在Virtex?-5 FPGA中实现标准的高速串行协议。

FPGA 嵌入式 DSP 电路 赛灵思 MIPS 总线 收发器 滤波器 LTE Xilinx 电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)