Virtex-5 FXT平台背景资料

时间:09-25

来源:互联网

点击:

- 系统级数字信号处理

Virtex-5 FXT平台的DSP性能对于其作为终极系统集成平台的价值做出了重要贡献。基本上,与传统DSP处理器的固定架构相比,FPGA提供的DSP性能高出几个数量级。目前越来越多的通信和多媒体系统都需要高于4MSPS的DSP性能,因此已经远远超出了大多数独立DSP处理器的极限。

利用FPGA可以方便地构造出高度并行的处理架构,能够在单个时钟周期里完成复杂的算法,从而单片器件就可以提供数以百计的MSPS性能。在如此高的DSP性能水平,设计人员可以选择降低FPGA的时钟速率来节省功耗,也可以选择实现更多通道来降低系统成本并降低材料清单成本(BOM)。

Virtex-5 FPGA 系列高性能DSP功能的关键是其DSP48E 逻辑片。这些逻辑片能够高效执行大多数数字滤波器底层运算的乘法累加操作。含内建乘法器模块的FPGA支持以专用硬件实现更宽输入的滤波器,从而使DSP设计人员可以获得更高的性能。Virtex-5 FXT FPGA提供高比率的DSP逻辑片(含高达384个内建18x25 DSP逻辑片),可以在500MHz时钟频率下提供高达192 GMACs/秒的性能。与Virtex-4中的18 x 18乘法器相比,Virtex-5 DSP48E逻辑片中的乘法器达到25 x 18。与更宽的数据路径和96位累加输出相配合可以支持更高精度的单精度浮点运算。同时,DSP48E逻辑片在高精度滤波器工作时消费的资源也更少。

除了快速的逻辑执行速度以外,高性能系统还需要处理单元具备快速吞吐大量数据的能力。Virtex FPGA提供了两种互补的方法来构建高效的存储器结构:

- 查找表(LUT)逻辑结构中的存储器单元构成的分布式RAM可以支持实现64位移位寄存器。

- 36Kb模块的嵌入式BlockRAM 结构可提供多达16.5 Mb的存储器。

由于嵌入式BlockRAM结构在芯片上是与DSP48E逻辑片邻近的,因此它们为向滤波器架构供应数据提供了超高带宽方法。FXT平台可提供高达16.5Mb的内部存储器和163 GBytes/s聚集IO性能的总IO带宽,可以满足系统级要求。

高系统集成度进一步提高性能

Virtex-5 FXT FPGA系统集成度的增强进一步提高了性能,这主要是由于整个平台处理子系统改善的复合效应。采用纵横交换式互连架构来代替单共享总线互连方式,利用多个独立总线组成的网络来并行完成数据传输,从而改善了总体系统性能。多个运算操作可同时进行,减少了堵塞和等待时间。利用128数据传输则进一步提高了系统数据吞吐能力。

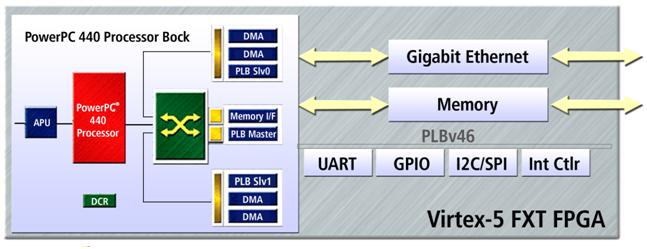

图 2.在Virtex-5 FXT平台上,新的PowerPC 440处理器模块接口通过硬交换式互连构造与硬核三模以太网MAC连接。

例如,图2中所示的千兆以太网设计显示出纵横交换式结构中存储器控制器(构造中生成的软控制器)与存储器控制器接口(MCI)的典型连接。由于这是一个独立于其它访问操作(如外设处理)的专用端口,因此总延迟和带宽也获得改善。外设(软)附加到PLB46总线,并连接到纵横交换构造上独立的主PLB(MPLB)端口。

千兆以太网通过新集成的硬件DMA控制器之一连接到系统。DMA引擎也接口到纵横交换构造。在需要时,这一交换构造成为DMA引擎与主存储器的连接路径。千兆以太网设计还利用了Virtex-5 FXT平台中的硬核千兆以太网MAC,因此可以利用更少的资源并降低功耗。

将上述基于Virtex-5 FXT平台的千兆位以太网系统与基于Virtex-4 FX平台的同样系统相比,性能提高了2.7倍。这一性能提升是指总体系统吞吐能力的提升,而非仅仅是处理器、外设或I/O。

应用

众多复杂应用如有线和无线通信、音频/视频广播、航空和国防以及工业科学和医疗等四大关键行业所提出的高度多元化的苛刻要求, 使得Virtex-5 FXT平台复合系统集成应运而生。这些市场中的客户对于赛灵思FXT产品线的发展做出了重要贡献,他们的共同推动, 使得器件配置能够满足FPGA逻辑、嵌入式处理、DSP、存储器和串行IO等所有方面的要求。

通信

无线通信市场是一个变化快速且具有挑战性的环境。系统设计人员始终面临提供新解决方案的挑战,或者是为了降低现有产品成本,或者是提供无风险的基础设施迁移方法,为现有以及下一代技术(如3GPP-LTE 和 WiMAX)提供高效的支持。

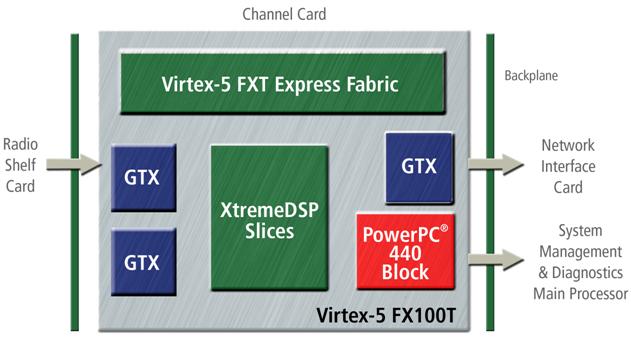

图 3.采用Virtex-5 FX100T器件的下一代无线基站(LTE)。

在这一应用中采用赛灵思Virtex-5 FXT FPGA可保证处理器子系统、DSP赋能的FPGA构造以及高速通信之间的紧密耦合和集成。这一LTE基带参考系统的硬件和软件单元的集成都利用标准硬件电路板在单片Virtex-5 FX100T器件上实现。

音频/视频广播

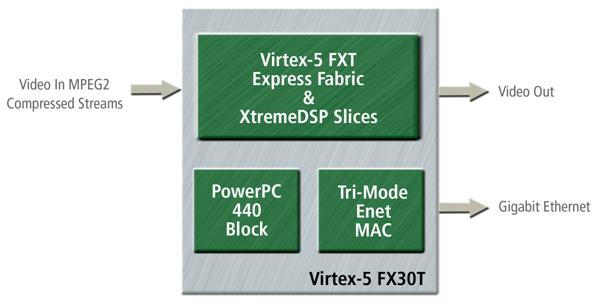

IP视频(Video-Over-IP)系统利用MPEG-2等压缩标准对视频流进行编码。然后,该系统利用因特网协议(IP)实现网络上不同点之间编码位流的传输。与网络上非时间关键的其它业务流量不同,视频数据必须遵守严格的服务质量(QoS)要求才能够满足视频要求。

目前利用视频处理器、用于加速或完成实时算法的可编程逻辑、以及用于网络通信的以太网解决方案构成的分块式解决方案也可以满足这些要求。但Virtex-5 FXT FPGA是业界首个在单个可编程SOC芯片上实现了所有这些功能。

图 4.IP视频(Video-Over-IP)系统集成图显示高级要求

- 系统级数字信号处理

FPGA 嵌入式 DSP 电路 赛灵思 MIPS 总线 收发器 滤波器 LTE Xilinx 电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)