第三代非易失FPGA给予片上系统更多的功能

时间:09-21

来源:互联网

点击:

LatticeXP2器件

Lattice与富士通(Fujitsu)合作开发了90nm嵌入式闪存工艺的 LatticeXP2系列,这种工艺使LatticeXP2器件的成本减少了50%。该器件把成功用于LatticeECP2 SRAM的功能块和Flash单元组合在一起,称之为flexiFLASH。

1 LatticeXP2结构-功能块

LatticeXP2器件的核心含有能够实现逻辑的可编程功能单元(PFU),以及占25%逻辑块的分布式存储器。用4输入的查找表和寄存器对来实现逻辑,对于FPGA工业、能够被系统设计者充分理解以及逻辑综合工具提供者来说,这是一个事实上的标准。分布式存储器为设计者提供了有效的方法实现便笺式存储器。这个系列提供5K到40K LUT。

嵌入式RAM(EBR)的sysMEM行提供166K -885Kb的18kb块的双口存储器。器件还有乘、加、减和累加功能的sysDSP块,用来实现通用的DSP功能,例如FIR滤波器、FFT和复杂算法。sysDSP块提供12-32的18x18乘法器。

器件的I/O引脚数从86到540,能与各种I/O标准互连,包括LVCMOS、PCI、LVTTL、LVDS和SSTL, HSTL。此外与附加的外部电阻相配合可以模仿LVPECL、BLVDS 和RSDS接口标准。校准DQS延时块的DLL、DDR寄存器和时钟传送电路能实现达400Mbps的DDR和DDR2存储器接口。还可以与器件一起实现750Mbps的普通DDR接口。

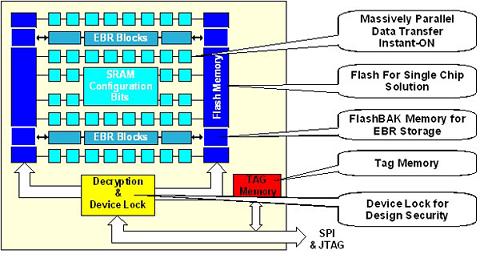

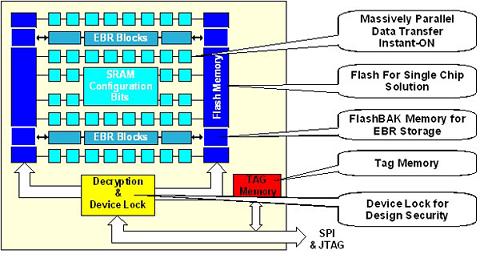

器件还提供多达4个PLL,用于时钟综合与对齐。片上振荡器提供低精度的时钟源,适用于许多辅助功能,例如监视时钟和键盘扫描逻辑。时钟的分布为8个全局时钟、8个区域时钟,或者2个高速边沿时钟。图的左边和右边为Flash存储器块,用于器件的配置。

器件工作于1.2伏的内部电压并有各种可供选择的封装。图4为器件的整个结构,图5为系列中的各个成员的详情。下面将详述非易失特性的运作。

图4 LatticeXP2结构

图5 flexiFLASH结构

FlexiFLASH详情

LatticeXP2器件在结构中组合了Flash 和SRAM,称为flexiFLASH。器件逻辑配置和嵌入式RAM块数据存储在SRAM单元。上电时或者根据用户命令,源于片上Flash存储器的块以并行形式载入SRAM。这种迅速的传送方式使器件具有瞬时的特性,片上的Flash存储器导致了单片解决方案。通过JTAG 或者SPI端口可以对Flash存储器进行写操作,如图5所示。

FlashBAK存储器

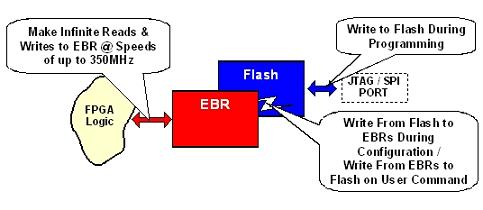

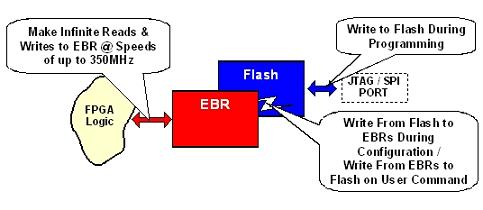

为了满足存储大块的数据,LatticeXP2器件提供称为FlashBAK存储器的创新功能。如前所述,上电时从片上Flash存储器装载至EBR。EBR能以350MHz的速度进行读或写。可以根据要求在FPGA内切换信号,根据当前EBR的内容,重写Flash是可能的。这个过程大约为1秒的时间。用这个方法,用户可获得高性能和无限次的读和写,这是非易失Flash存储器与SRAM相结合的结果。这个器件提供166K 和 885Kbit的 FlashBAK存储器。

图6 非易失FlashBAK存储

串行TAG存储器

为了提供小量可串行访问的存储器,每个器件都有0.6K至3.4Kbit的串行TAG存储器。如图7所示,可以通过器件的JTAG接口或者FPGA逻辑访问这个存储器。这个存储器位于器件安全结构的外面,可以独立地访问器件安全设置。

图7 串行TAG存储器

器件锁提供设计安全

如前所述,许多设计者都要确保设计安全地锁定在FPGA之内。用物理的方法来检查FPGA 的SRAM单元几乎是不可能的,因为SRAM单元掩埋在多层金属下。防止通过JTAG 或者SPI端口查询器件配置的保密位进一步完善了安全性。

为了防止未授权的篡改,器件有64位的码,一旦设置后,在擦除或者重写Flash时需要验证。对于客户要求更加安全的解决方案,还有一次性编程(OTP)的模式。一旦器件处于这种模式,就不能擦除或者对器件再编程。

全面的现场更新

如前所述,实现现场更新的设计者要求最大的设备正常运行时间、很好的可靠性和高的安全性。为了满足这些要求,LatticeXP2器件提供TransFR I/O、双引导和128位AES解密。

针对最大正常工作时间的TransFR I/O

在系统配置期间,大多数FPGA的I/O均为三态。这种缺少控制的状态通常迫使循环上电以便更新FPGA的配置。如同其他的Lattice FPGA,LatticeXP2器件具有TransFR I/O,在器件配置期间能冻结I/O的状态。这样现场更新的器件就有最小的中断和停机时间,系统设计者能够满足高系统正常运行时间和现场更新逻辑的双重要求。图8展示了TransFR I/O更新的4个步骤。因为新的配置可以在后台载入LatticeXP2的片上Flash,新的配置载入SRAM是很快的。锁定I/O,施加新的配置,再释放I/O的时间小于2毫秒。

图8 TransFR I/O更新的4个步骤

Lattice与富士通(Fujitsu)合作开发了90nm嵌入式闪存工艺的 LatticeXP2系列,这种工艺使LatticeXP2器件的成本减少了50%。该器件把成功用于LatticeECP2 SRAM的功能块和Flash单元组合在一起,称之为flexiFLASH。

1 LatticeXP2结构-功能块

LatticeXP2器件的核心含有能够实现逻辑的可编程功能单元(PFU),以及占25%逻辑块的分布式存储器。用4输入的查找表和寄存器对来实现逻辑,对于FPGA工业、能够被系统设计者充分理解以及逻辑综合工具提供者来说,这是一个事实上的标准。分布式存储器为设计者提供了有效的方法实现便笺式存储器。这个系列提供5K到40K LUT。

嵌入式RAM(EBR)的sysMEM行提供166K -885Kb的18kb块的双口存储器。器件还有乘、加、减和累加功能的sysDSP块,用来实现通用的DSP功能,例如FIR滤波器、FFT和复杂算法。sysDSP块提供12-32的18x18乘法器。

器件的I/O引脚数从86到540,能与各种I/O标准互连,包括LVCMOS、PCI、LVTTL、LVDS和SSTL, HSTL。此外与附加的外部电阻相配合可以模仿LVPECL、BLVDS 和RSDS接口标准。校准DQS延时块的DLL、DDR寄存器和时钟传送电路能实现达400Mbps的DDR和DDR2存储器接口。还可以与器件一起实现750Mbps的普通DDR接口。

器件还提供多达4个PLL,用于时钟综合与对齐。片上振荡器提供低精度的时钟源,适用于许多辅助功能,例如监视时钟和键盘扫描逻辑。时钟的分布为8个全局时钟、8个区域时钟,或者2个高速边沿时钟。图的左边和右边为Flash存储器块,用于器件的配置。

器件工作于1.2伏的内部电压并有各种可供选择的封装。图4为器件的整个结构,图5为系列中的各个成员的详情。下面将详述非易失特性的运作。

图4 LatticeXP2结构

图5 flexiFLASH结构

FlexiFLASH详情

LatticeXP2器件在结构中组合了Flash 和SRAM,称为flexiFLASH。器件逻辑配置和嵌入式RAM块数据存储在SRAM单元。上电时或者根据用户命令,源于片上Flash存储器的块以并行形式载入SRAM。这种迅速的传送方式使器件具有瞬时的特性,片上的Flash存储器导致了单片解决方案。通过JTAG 或者SPI端口可以对Flash存储器进行写操作,如图5所示。

FlashBAK存储器

为了满足存储大块的数据,LatticeXP2器件提供称为FlashBAK存储器的创新功能。如前所述,上电时从片上Flash存储器装载至EBR。EBR能以350MHz的速度进行读或写。可以根据要求在FPGA内切换信号,根据当前EBR的内容,重写Flash是可能的。这个过程大约为1秒的时间。用这个方法,用户可获得高性能和无限次的读和写,这是非易失Flash存储器与SRAM相结合的结果。这个器件提供166K 和 885Kbit的 FlashBAK存储器。

图6 非易失FlashBAK存储

串行TAG存储器

为了提供小量可串行访问的存储器,每个器件都有0.6K至3.4Kbit的串行TAG存储器。如图7所示,可以通过器件的JTAG接口或者FPGA逻辑访问这个存储器。这个存储器位于器件安全结构的外面,可以独立地访问器件安全设置。

图7 串行TAG存储器

器件锁提供设计安全

如前所述,许多设计者都要确保设计安全地锁定在FPGA之内。用物理的方法来检查FPGA 的SRAM单元几乎是不可能的,因为SRAM单元掩埋在多层金属下。防止通过JTAG 或者SPI端口查询器件配置的保密位进一步完善了安全性。

为了防止未授权的篡改,器件有64位的码,一旦设置后,在擦除或者重写Flash时需要验证。对于客户要求更加安全的解决方案,还有一次性编程(OTP)的模式。一旦器件处于这种模式,就不能擦除或者对器件再编程。

全面的现场更新

如前所述,实现现场更新的设计者要求最大的设备正常运行时间、很好的可靠性和高的安全性。为了满足这些要求,LatticeXP2器件提供TransFR I/O、双引导和128位AES解密。

针对最大正常工作时间的TransFR I/O

在系统配置期间,大多数FPGA的I/O均为三态。这种缺少控制的状态通常迫使循环上电以便更新FPGA的配置。如同其他的Lattice FPGA,LatticeXP2器件具有TransFR I/O,在器件配置期间能冻结I/O的状态。这样现场更新的器件就有最小的中断和停机时间,系统设计者能够满足高系统正常运行时间和现场更新逻辑的双重要求。图8展示了TransFR I/O更新的4个步骤。因为新的配置可以在后台载入LatticeXP2的片上Flash,新的配置载入SRAM是很快的。锁定I/O,施加新的配置,再释放I/O的时间小于2毫秒。

图8 TransFR I/O更新的4个步骤

FPGA 电路 半导体 传感器 电子 总线 嵌入式 DSP 滤波器 CMOS 电阻 振荡器 电压 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)