用FPGA/CPLD设计UART

时间:09-01

来源:互联网

点击:

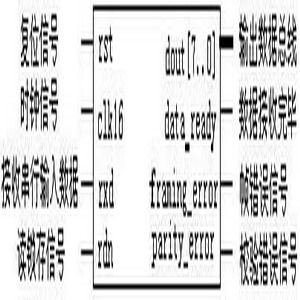

图 5

---实现的部分VHDL 程序如下。

--- elsif clk1x'event and clk1x = '1' then

---if std_logic_vector(length_no) >= “0001” and std_logic_vector(length_no) <= “1001” then

---数据帧数据由接收串行数据端移位入接收移位寄存器

---rsr(0) <= rxda ;

--- rsr(7 downto 1) <= rsr(6 downto 0) ;

--- parity <= parity xor rsr(7) ;

--- elsif std_logic_vector(length_no) = “1010” then --- rbr <= rsr ;

--- 接收移位寄存器数据进入接收缓冲器

---

--- end if ;

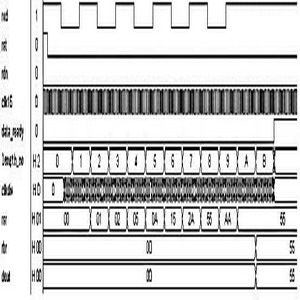

---接收器仿真波形如图6 所示。

图 6

3、 波特率发生器

--- UART 的接收和发送是按照相同的波特率进行收发的。波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提出异步的串行数据。

---根据给定的晶振时钟和要求的波特率算出波特率分频数。

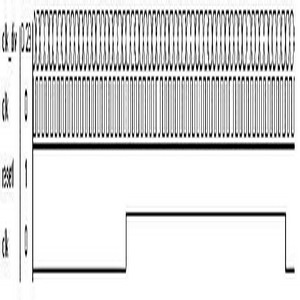

---波特率发生器仿真波形如图7 所示。

三、小 结

通过波特率发生器、发送器和接收器模块的设计与仿真,能较容易地实现通用异步收发器总模块,对于收发的数据帧和发生的波特率时钟频率能较灵活地改变,而且硬件实现不需要很多资源,尤其能较灵活地嵌入到FPGA/CPLD的开发中。在EDA技术平台上进行设计、仿真与实现具有较好的优越性。

收发器 集成电路 FPGA CPLD VHDL EDA 总线 仿真 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 选择合适的FPGA千兆位收发器至关重要(10-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- FPGA高速收发器设计原则(03-11)

- 基于CPLD的USB总线的隔离接口实现(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)