用FPGA实现数字电视条件接收系统

时间:09-01

来源:互联网

点击:

2.1加扰器的实现

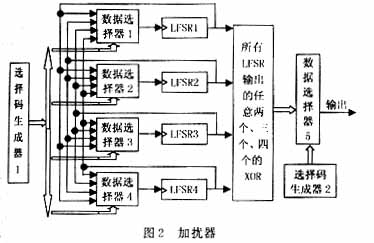

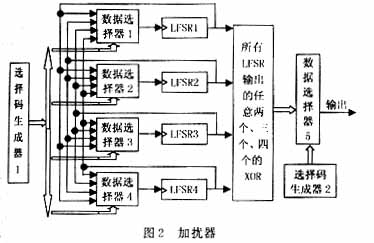

加扰器在条件接收中是一个关键部分,他关系到整个系统的保密程度,所以需要一个安全性较高的加扰器。图2所示加扰器是在FPGA内部实现:他是以可预置线性反馈寄存器(LFSR)为基础,与数据选择器共同形成。4个LFSR的阶数要求互质,每个LFSR的反馈多项式要求是本原的,这样产生的伪随机序列具有最大周期。总线是控制码发生器(一个伪随机序列发生器)产生的选择器控制码,有8个抽头并行输出,每2位对应一个选择器的选择端。每个选择器的输出是选出的4个LFSR反馈之一,作为与之相连的LFSR时钟。这是Gollmann级连的改进型,通过数据选择消除了Gollmann级连易受锁定攻击的缺点。4个LSFR输出的XOR(这是FPGA中的一个器件,当输入有奇数个1时输出为1),除去LFSR的线性影响,通过数字选择器选取这些XOR的输出之一作为加扰序列的输出。数字选择器滤除了加扰器的代数特性避免相关(线性代数)攻击。

选择码生成器可由CW产生器代替,CW一部分作为选择器的选择码,一部分写入4个可预置的LFSR。这样,加扰器寄存器不是很多,周期又较长,达到节约硬件且保密程度较高的目的。

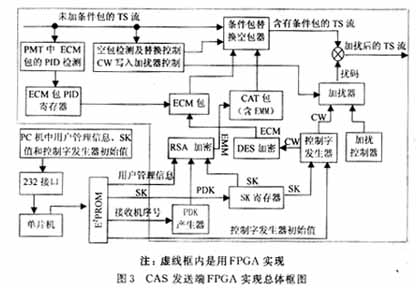

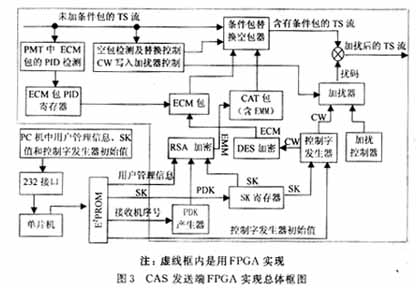

2.2 条件接收发送端FPGA实现

用户管理信息需要PC机处理和保存,既然他是必须的,就可以在PC机中做些其他的事情,以便降低硬件的复杂度,增强信息的保密性。服务密约SK和控制字CW发生器初始值可以在PC机中通过伪随机序列生成程序生成。在PC机中生成SK和CW初值的优点就是程序容易改动,伪随机序列周期可以足够长,保密性高。

在一些文献中,ECM在PES层已经加入,对于PES层加扰当然很适合;但是对于TS层加扰,完成ECM包中含有的CW和写入加扰器的CW一致性(实际就是加扰和解扰的同步)比较困难。采用ECM也在TS层加入,实现加解扰同步就容易得多。

TS流是连续不断的实时信号,条件信号并不可以任意加入其中。不过,TS流中存在大量的空包,可以通过空包替换的方法实现条件包的加入。空包替换器实际就是一个数据选择器,在需要条件包的地方,让条件包代替空包。

ECM包PID寄存器存放从PMT中读取的ECM包的PID,以便形成ECM包时利用。ECM包和EMM包的形成是给EMM和ECM加上包头、PID和Table_id等。ECM包的Table_id有两个,0x80和0x81,是为了方便接收端解扰,只有ECM包含新的CW时,他才发生变化。如果Table_id 没发生变化,接受端就可以不处理这个ECM包,还用以前的CW。EMM只有一个时,可以把他放入CAT包;如果有多个时,可单独形成EMM包,通过CAT 包中的描述子确定他的PID。其实,为了节约硬件,在加入TS流前条件包并不一定是一个完整的TS包,他包含必要的信息就行了。在代替空包时,有用信息代替空包中的前一部分,和余下的空包中内容共同构成TS包。SK信息变化很慢,EMM包和CAT包只需满足刚开机用户能迅速找到SK就行。ECM包替代空包比CAT包或EMM包严格的多,因为CW变化快,并且要使ECM包内的CW和写入加扰器的CW同步,以便保证正确解扰。

CW的加密采用DES(Data Encryption Standard)算法,DES速度快,加密强度较高,硬件容易实现,适合CW变化较快的要求。SK的加密采用RSA算法,RSA 算法速度比DES慢的多,硬件实现只是DES速度的千分之一,但是加密强度大。SK的变化频率低,使用时间长,安全性要求高,RSA正好满足这些要求。 TS流的加扰,采用上述的加扰器,通过加扰控制,使之不对条件包、私有数据包、空包、TS包头、PID等不可加扰的数据进行加扰。

3 结语

本文介绍了条件接收系统的基本原理,并提出一种复接和条件接收相分离的实现方法。这种方法使条件接收系统不受复接的约束,实现起来比较灵活,便于调试。并且这种结构不仅可以对单节目TS流加扰,也可以对多节目TS流进行加扰。采用空包替换,在TS层加入ECM条件包,容易实现加解扰的同步。在实现条件接收的过程中,设计出安全性较高的加扰器成功应用于系统,实现了信息的加、解扰。

加扰器在条件接收中是一个关键部分,他关系到整个系统的保密程度,所以需要一个安全性较高的加扰器。图2所示加扰器是在FPGA内部实现:他是以可预置线性反馈寄存器(LFSR)为基础,与数据选择器共同形成。4个LFSR的阶数要求互质,每个LFSR的反馈多项式要求是本原的,这样产生的伪随机序列具有最大周期。总线是控制码发生器(一个伪随机序列发生器)产生的选择器控制码,有8个抽头并行输出,每2位对应一个选择器的选择端。每个选择器的输出是选出的4个LFSR反馈之一,作为与之相连的LFSR时钟。这是Gollmann级连的改进型,通过数据选择消除了Gollmann级连易受锁定攻击的缺点。4个LSFR输出的XOR(这是FPGA中的一个器件,当输入有奇数个1时输出为1),除去LFSR的线性影响,通过数字选择器选取这些XOR的输出之一作为加扰序列的输出。数字选择器滤除了加扰器的代数特性避免相关(线性代数)攻击。

选择码生成器可由CW产生器代替,CW一部分作为选择器的选择码,一部分写入4个可预置的LFSR。这样,加扰器寄存器不是很多,周期又较长,达到节约硬件且保密程度较高的目的。

2.2 条件接收发送端FPGA实现

用户管理信息需要PC机处理和保存,既然他是必须的,就可以在PC机中做些其他的事情,以便降低硬件的复杂度,增强信息的保密性。服务密约SK和控制字CW发生器初始值可以在PC机中通过伪随机序列生成程序生成。在PC机中生成SK和CW初值的优点就是程序容易改动,伪随机序列周期可以足够长,保密性高。

在一些文献中,ECM在PES层已经加入,对于PES层加扰当然很适合;但是对于TS层加扰,完成ECM包中含有的CW和写入加扰器的CW一致性(实际就是加扰和解扰的同步)比较困难。采用ECM也在TS层加入,实现加解扰同步就容易得多。

TS流是连续不断的实时信号,条件信号并不可以任意加入其中。不过,TS流中存在大量的空包,可以通过空包替换的方法实现条件包的加入。空包替换器实际就是一个数据选择器,在需要条件包的地方,让条件包代替空包。

ECM包PID寄存器存放从PMT中读取的ECM包的PID,以便形成ECM包时利用。ECM包和EMM包的形成是给EMM和ECM加上包头、PID和Table_id等。ECM包的Table_id有两个,0x80和0x81,是为了方便接收端解扰,只有ECM包含新的CW时,他才发生变化。如果Table_id 没发生变化,接受端就可以不处理这个ECM包,还用以前的CW。EMM只有一个时,可以把他放入CAT包;如果有多个时,可单独形成EMM包,通过CAT 包中的描述子确定他的PID。其实,为了节约硬件,在加入TS流前条件包并不一定是一个完整的TS包,他包含必要的信息就行了。在代替空包时,有用信息代替空包中的前一部分,和余下的空包中内容共同构成TS包。SK信息变化很慢,EMM包和CAT包只需满足刚开机用户能迅速找到SK就行。ECM包替代空包比CAT包或EMM包严格的多,因为CW变化快,并且要使ECM包内的CW和写入加扰器的CW同步,以便保证正确解扰。

CW的加密采用DES(Data Encryption Standard)算法,DES速度快,加密强度较高,硬件容易实现,适合CW变化较快的要求。SK的加密采用RSA算法,RSA 算法速度比DES慢的多,硬件实现只是DES速度的千分之一,但是加密强度大。SK的变化频率低,使用时间长,安全性要求高,RSA正好满足这些要求。 TS流的加扰,采用上述的加扰器,通过加扰控制,使之不对条件包、私有数据包、空包、TS包头、PID等不可加扰的数据进行加扰。

3 结语

本文介绍了条件接收系统的基本原理,并提出一种复接和条件接收相分离的实现方法。这种方法使条件接收系统不受复接的约束,实现起来比较灵活,便于调试。并且这种结构不仅可以对单节目TS流加扰,也可以对多节目TS流进行加扰。采用空包替换,在TS层加入ECM条件包,容易实现加解扰的同步。在实现条件接收的过程中,设计出安全性较高的加扰器成功应用于系统,实现了信息的加、解扰。

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 基于FPGA的MPEG-2复用器中FIFO的一种设计方案(07-22)

- 基于FPGA的数字电视CAS系统设计(07-24)

- 用CPLD和外部SRAM构成大容量FIFO的设计(07-29)

- 地面数字电视符号与载波同步的FPGA实现(08-01)

- 采用基于FPGA的SoC进行数字显示系统设计(08-05)