使用SignalTap II逻辑分析仪调试FPGA

时间:08-31

来源:互联网

点击:

1 概述

随着FPGA容量的增大,FPGA的设计日益复杂,设计调试成为一个很繁重的任务。为了使得设计尽快投入市场,设计人员需要一种简易有效的测试工具,以尽可能的缩短测试时间。传统的逻辑分析仪在测试复杂的FPGA设计时,将会面临以下几点问题:1)缺少空余I/O引脚。设计中器件的选择依据设计规模而定,通常所选器件的I/O引脚数目和设计的需求是恰好匹配的。2)I/O引脚难以引出。设计者为减小电路板的面积,大都采用细间距工艺技术,在不改变PCB板布线的情况下引出I/O引脚非常困难。3)外接逻辑分析仪有改变FPGA设计中信号原来状态的可能,因此难以保证信号的正确性。4)传统的逻辑分析仪价格昂贵,将会加重设计方的经济负担。

伴随着EDA工具的快速发展,一种新的调试工具Quartus II 中的SignalTap II 满足了FPGA开发中硬件调试的要求,它具有无干扰、便于升级、使用简单、价格低廉等特点。本文将介绍SignalTap II逻辑分析仪的主要特点和使用流程,并以一个实例介绍该分析仪具体的操作方法和步骤。

2 SignalTap II的特点及使用

SignalTap II嵌入逻辑分析仪集成到Quartus II设计软件中,能够捕获和显示可编程单芯片系统(SOPC)设计中实时信号的状态,这样开发者就可以在整个设计过程中以系统级的速度观察硬件和软件的交互作用。它支持多达1024个通道,采样深度高达128Kb,每个分析仪均有10级触发输入/输出,从而增加了采样的精度。SignalTap II为设计者提供了业界领先的SOPC设计的实时可视性,能够大大减少验证过程中所花费的时间。目前SignalTap II逻辑分析仪支持的器件系列包括:APEXT II, APEX20KE, APEX20KC, APEX20K, Cyclone, Excalibur, Mercury, Stratix GX, Stratix。

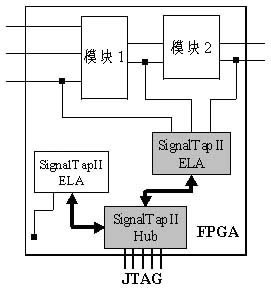

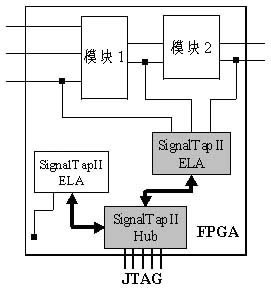

SignalTap II将逻辑分析模块嵌入到FPGA中,如图1所示。逻辑分析模块对待测节点的数据进行捕获,数据通过JTAG接口从FPGA传送到Quartus II软件中显示。使用SignalTap II无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件。SignalTap II对FPGA的引脚和内部的连线信号进行捕获后,将数据存储在一定的RAM块中。因此,需要用于捕获的采样时钟信号和保存被测信号的一定点数的RAM块。

使用SignalTap II的一般流程是:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形、在测试完毕后将该逻辑分析仪从项目中删除。以下描述设置 SignalTap II 文件的基本流程:

1.设置采样时钟。采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。SignalTap II在时钟上升沿将被测信号存储到缓存。

2.设置被测信号。可以使用Node Finder 中的 SignalTap II 滤波器查找所有预综合和布局布线后的SignalTap II 节点,添加要观察的信号。逻辑分析器不可测试的信号包括:逻辑单元的进位信号、PLL的时钟输出、JTAG引脚信号、LVDS(低压差分)信号。

3.配置采样深度、确定RAM的大小。SignalTap II所能显示的被测信号波形的时间长度为Tx,计算公式如下: --- Tx="N"×Ts --- N为缓存中存储的采样点数,Ts为采样时钟的周期。

4.设置buffer acquisition mode。buffer acquisition mode包括循环采样存储、连续存储两种模式。循环采样存储也就是分段存储,将整个缓存分成多个片段(segment),每当触发条件满足时就捕获一段数据。该功能可以去掉无关的数据,使采样缓存的使用更加灵活。

5.触发级别。SignalTap II支持多触发级的触发方式,最多可支持10级触发。

6.触发条件。可以设定复杂的触发条件用来捕获相应的数据,以协助调试设计。当触发条件满足时,在signalTap时钟的上升沿采样被测信号。

完成STP设置后,将STP文件同原有的设计下载到FPGA中,在Quartus II中SignalTap II窗口下查看逻辑分析仪捕获结果。SignalTap II可将数据通过多余的I/O引脚输出,以供外设的逻辑分析器使用;或输出为csv、tbl、vcd、vwf文件格式以供第三方仿真工具使用。

3 实例分析

本文以一个ADC0809器件的采样控制器作为实例,具体说明如何用SignalTap II 来进行FPGA设计的验证。使用Altera公司的器件Cyclone系列FPGA- EP1C12Q240C8,该器件支持SignalTap II 嵌入式逻辑分析仪的使用。

FPGA的设计结构如图2所示。数字倍频器的倍频输出提供ADC控制器的采样触发脉冲。A/D转换器ADC0809的操作时序见数据手册,根据其操作时序,ADC控制器来实现ADC0809的数据采集操作,采样的时机由倍频器来控制。控制器每控制完成一次采样操作,则停止等待下一个触发脉冲的到来。倍频器每输出一个低电平脉冲,ADC采样控制器的状态机进行一次采样操作。在倍频器的触发控制下,完成被测信号一个基波周期N个点的等间隔采样,同时数字倍频器跟踪输入信号的频率的变化,尽可能地保持N个点的采样宽度正好为被测信号一个周波的宽度。

测试项目是基于FPGA的AD采样控制器,它是用状态机控制的周期性的重复事件,一次采样操作完成后等待采样脉冲、开始下一次的采样。针对待测项目的周期性,

在STP文件中将buffer acquisition mode分别设为连续存储和循环采样存储两种模式进行验证。连续存储方式记录采样操作的连续过程,而在循环采样存储方式下SignalTap II记录多次采样时刻数据。

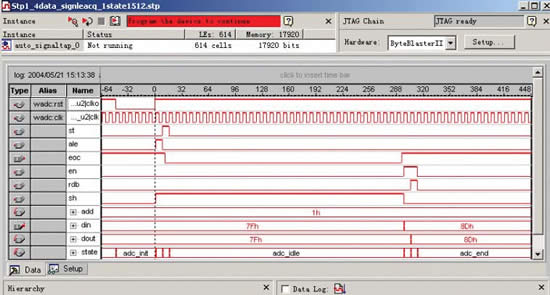

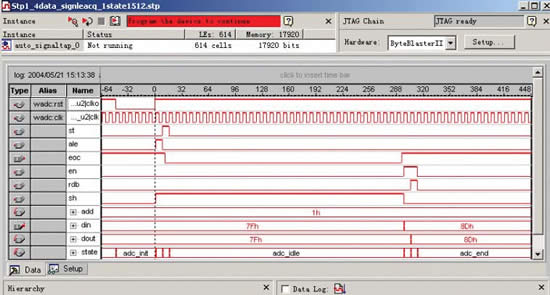

按照上述SignalTap II的使用步骤,在编译后的工程中添加STP文件,并对文件进行设置,如图3所示。如1处设置采样时钟ct,系统时钟的16分频。2处添加测试信号,包括待测模块输出的AD采样控制信号和状态机的状态等。3处是采样深度的设置,设为512。在4处的设置确定了在clko时钟的上升沿触发逻辑分析仪。在连续存储模式下设置buffer acquisition mode为Circular前触发位置。在分段存储模式下设置为Sigmented 512 1 bit segments,表示将存储区划分成512个段,每段1个位的存储深度。存储模式的设置如图中6所示。另外,使用Mnemonic Table将状态机的7个状态标示为直观名称。

首先将STP文件设置成连续存储模式,并将该文件连同工程一起下载到FPGA中。在连续存储模式下,SignalTap II在clko时钟的上升沿连续采样直到采样点数达到512个。这样,SignalTap II记录了一次采样过程的所有数据,捕获结果如图4所示,从中可以看到FPGA控制ADC0809转换的时序波形。

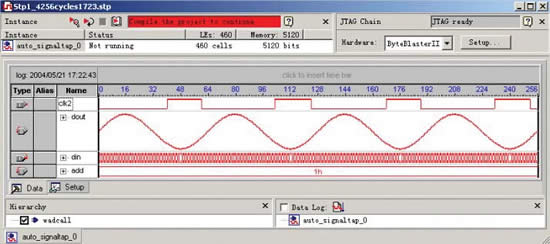

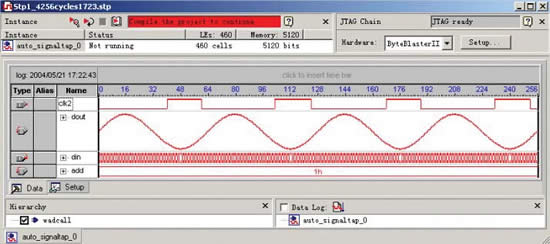

将图3所示步骤6中的Buffer acquisition node改为Segmented方式,设其值为256 1 bit segments,并将修改后的STP文件连同工程重新下载到FPGA中。和单次触发相同的是逻辑分析仪在ADC0809采样时钟上升沿时触发逻辑分析仪,不同的是因为每一段只有1bit的存储深度,因此捕获1位数据后逻辑分析仪停止,等待下一次满足触发信号再次启动,一共启动256次。在波形显示窗口,设显示格式为Line Chart,这样结果就直观的显示为连续的波形。分片采样,可观察同步采样的结果,图5是连续采样256个点的结果波形。

随着FPGA容量的增大,FPGA的设计日益复杂,设计调试成为一个很繁重的任务。为了使得设计尽快投入市场,设计人员需要一种简易有效的测试工具,以尽可能的缩短测试时间。传统的逻辑分析仪在测试复杂的FPGA设计时,将会面临以下几点问题:1)缺少空余I/O引脚。设计中器件的选择依据设计规模而定,通常所选器件的I/O引脚数目和设计的需求是恰好匹配的。2)I/O引脚难以引出。设计者为减小电路板的面积,大都采用细间距工艺技术,在不改变PCB板布线的情况下引出I/O引脚非常困难。3)外接逻辑分析仪有改变FPGA设计中信号原来状态的可能,因此难以保证信号的正确性。4)传统的逻辑分析仪价格昂贵,将会加重设计方的经济负担。

伴随着EDA工具的快速发展,一种新的调试工具Quartus II 中的SignalTap II 满足了FPGA开发中硬件调试的要求,它具有无干扰、便于升级、使用简单、价格低廉等特点。本文将介绍SignalTap II逻辑分析仪的主要特点和使用流程,并以一个实例介绍该分析仪具体的操作方法和步骤。

2 SignalTap II的特点及使用

SignalTap II嵌入逻辑分析仪集成到Quartus II设计软件中,能够捕获和显示可编程单芯片系统(SOPC)设计中实时信号的状态,这样开发者就可以在整个设计过程中以系统级的速度观察硬件和软件的交互作用。它支持多达1024个通道,采样深度高达128Kb,每个分析仪均有10级触发输入/输出,从而增加了采样的精度。SignalTap II为设计者提供了业界领先的SOPC设计的实时可视性,能够大大减少验证过程中所花费的时间。目前SignalTap II逻辑分析仪支持的器件系列包括:APEXT II, APEX20KE, APEX20KC, APEX20K, Cyclone, Excalibur, Mercury, Stratix GX, Stratix。

SignalTap II将逻辑分析模块嵌入到FPGA中,如图1所示。逻辑分析模块对待测节点的数据进行捕获,数据通过JTAG接口从FPGA传送到Quartus II软件中显示。使用SignalTap II无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件。SignalTap II对FPGA的引脚和内部的连线信号进行捕获后,将数据存储在一定的RAM块中。因此,需要用于捕获的采样时钟信号和保存被测信号的一定点数的RAM块。

使用SignalTap II的一般流程是:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形、在测试完毕后将该逻辑分析仪从项目中删除。以下描述设置 SignalTap II 文件的基本流程:

1.设置采样时钟。采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。SignalTap II在时钟上升沿将被测信号存储到缓存。

2.设置被测信号。可以使用Node Finder 中的 SignalTap II 滤波器查找所有预综合和布局布线后的SignalTap II 节点,添加要观察的信号。逻辑分析器不可测试的信号包括:逻辑单元的进位信号、PLL的时钟输出、JTAG引脚信号、LVDS(低压差分)信号。

3.配置采样深度、确定RAM的大小。SignalTap II所能显示的被测信号波形的时间长度为Tx,计算公式如下: --- Tx="N"×Ts --- N为缓存中存储的采样点数,Ts为采样时钟的周期。

4.设置buffer acquisition mode。buffer acquisition mode包括循环采样存储、连续存储两种模式。循环采样存储也就是分段存储,将整个缓存分成多个片段(segment),每当触发条件满足时就捕获一段数据。该功能可以去掉无关的数据,使采样缓存的使用更加灵活。

5.触发级别。SignalTap II支持多触发级的触发方式,最多可支持10级触发。

6.触发条件。可以设定复杂的触发条件用来捕获相应的数据,以协助调试设计。当触发条件满足时,在signalTap时钟的上升沿采样被测信号。

完成STP设置后,将STP文件同原有的设计下载到FPGA中,在Quartus II中SignalTap II窗口下查看逻辑分析仪捕获结果。SignalTap II可将数据通过多余的I/O引脚输出,以供外设的逻辑分析器使用;或输出为csv、tbl、vcd、vwf文件格式以供第三方仿真工具使用。

3 实例分析

本文以一个ADC0809器件的采样控制器作为实例,具体说明如何用SignalTap II 来进行FPGA设计的验证。使用Altera公司的器件Cyclone系列FPGA- EP1C12Q240C8,该器件支持SignalTap II 嵌入式逻辑分析仪的使用。

FPGA的设计结构如图2所示。数字倍频器的倍频输出提供ADC控制器的采样触发脉冲。A/D转换器ADC0809的操作时序见数据手册,根据其操作时序,ADC控制器来实现ADC0809的数据采集操作,采样的时机由倍频器来控制。控制器每控制完成一次采样操作,则停止等待下一个触发脉冲的到来。倍频器每输出一个低电平脉冲,ADC采样控制器的状态机进行一次采样操作。在倍频器的触发控制下,完成被测信号一个基波周期N个点的等间隔采样,同时数字倍频器跟踪输入信号的频率的变化,尽可能地保持N个点的采样宽度正好为被测信号一个周波的宽度。

测试项目是基于FPGA的AD采样控制器,它是用状态机控制的周期性的重复事件,一次采样操作完成后等待采样脉冲、开始下一次的采样。针对待测项目的周期性,

在STP文件中将buffer acquisition mode分别设为连续存储和循环采样存储两种模式进行验证。连续存储方式记录采样操作的连续过程,而在循环采样存储方式下SignalTap II记录多次采样时刻数据。

按照上述SignalTap II的使用步骤,在编译后的工程中添加STP文件,并对文件进行设置,如图3所示。如1处设置采样时钟ct,系统时钟的16分频。2处添加测试信号,包括待测模块输出的AD采样控制信号和状态机的状态等。3处是采样深度的设置,设为512。在4处的设置确定了在clko时钟的上升沿触发逻辑分析仪。在连续存储模式下设置buffer acquisition mode为Circular前触发位置。在分段存储模式下设置为Sigmented 512 1 bit segments,表示将存储区划分成512个段,每段1个位的存储深度。存储模式的设置如图中6所示。另外,使用Mnemonic Table将状态机的7个状态标示为直观名称。

首先将STP文件设置成连续存储模式,并将该文件连同工程一起下载到FPGA中。在连续存储模式下,SignalTap II在clko时钟的上升沿连续采样直到采样点数达到512个。这样,SignalTap II记录了一次采样过程的所有数据,捕获结果如图4所示,从中可以看到FPGA控制ADC0809转换的时序波形。

将图3所示步骤6中的Buffer acquisition node改为Segmented方式,设其值为256 1 bit segments,并将修改后的STP文件连同工程重新下载到FPGA中。和单次触发相同的是逻辑分析仪在ADC0809采样时钟上升沿时触发逻辑分析仪,不同的是因为每一段只有1bit的存储深度,因此捕获1位数据后逻辑分析仪停止,等待下一次满足触发信号再次启动,一共启动256次。在波形显示窗口,设显示格式为Line Chart,这样结果就直观的显示为连续的波形。分片采样,可观察同步采样的结果,图5是连续采样256个点的结果波形。

FPGA 电路 PCB EDA Quartus 滤波器 仿真 ADC Altera 嵌入式 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)