用FPGA实现数字电视条件接收系统

时间:09-01

来源:互联网

点击:

数字电视是近十几年发展起来的高新技术,其声像质量,抗干扰性及传送节目的数目等方面有模拟电视无法比拟的优点。数字电视的开播,使观众可以欣赏更多的优质节目;同时,服务商则希望实现按观看内容进行收费的良性运营。条件接收系统CAS主要的功能就是确保只有付费用户才能收看所选节目,彻底解决运营商的收费问题。可以说,CAS是运营商发展新服务的关键。但是,我国目前开通的数字电视用的CAS大多是国外的软硬件方案,随着数字电视的普及,CAS的国产化就成为非常紧迫的要求。

1 数字电视条件接收系统(CAS)的工作原理

1.1 CAS的加扰和解扰

在采用MPEG-2的数字电视中,加扰过程就是用一个由控制字CW控制的伪随机序列对PES流或TS流进行扰动,使没有被授权的用户不能观看节目。对于授权用户,他们的接收机也有一个同样的伪随机序列产生器,如果接收到正确的CW,就可以生成解扰序列,解除信号的扰动,恢复出接收机可以播放的信号。

1.2 CAS的加密和解密

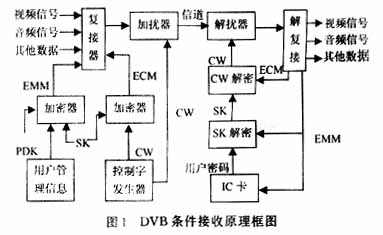

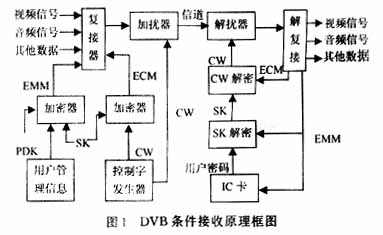

用户解扰的关键就是得到正确的CW,而CW是随着有用信号通过公用的信道传输。所以说,CAS的加密实际就是对CW的加密,以防止非授权用户的侵入。结合图1介绍CW的加解密机制。

CW一方面控制加扰器对数据流加扰;另一方面通过业务密钥SK(Server Key)加密形成授权控制信息ECM送到接收端。为了信号的保密性,CW一般几秒就要改变一次,并且SK也必须进行加密保护。一般来说,对SK加密完全按照各个用户的特征来进行。由于每台接收机可以编惟一的接收机号,所以可通过此序号生成个人分配密钥PDK(Personal DistributionKey)对SK加密,形成授权管理信息EMM。PDK由CA系统设备产生并严格控制,在接收端不能被用户读出。本文采用的方法是在接收端把PDK装入FPGA芯片中,增加保密性。为了能提供不同级别、不同类型的服务,一套CA系统往往为每个用户分配好几个PDK,来满足丰富的业务需求。EMM是用户管理信息和SK等通过PDK加密形成。用户管理信息由服务商的用户管理系统形成,包括用户名称、地址、智能卡号等。EMM平均每 8~10 s插入传送流一次,以便新开机用户解扰。解扰是加扰的逆过程,首先是用户插入IC卡,输入用户密码,如果密码正确PDK就会对SK进行解密;然后,由SK 对ECM解密出控制字CW。

2 条件接收系统的FPGA实现

FPGA(Field Programmable Gate Array)有丰富的触发器和I/O口可以满足完成CAS功能,开发周期短,可以反复修改,特别适合需不断完善电路的开发阶段。

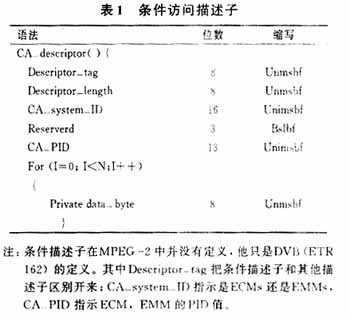

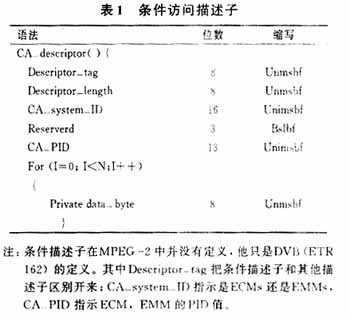

要实现CAS硬件设计,首先要理解程序特殊信息PSI。PSI能从多节目的TS流中找出所需要的节目码流和条件接收信息等。PSI必须以一定的频率不断发送,至少20次/s,以便新开的接收机能及时解释传送流的性质。PSI由4个表组成,包括:程序关联表(PAT)、程序映射表(PMT)、网络信息表(NIT)以及条件访问表(CAT)。其中CAT和PMT与条件接收有关。条件接收信息EMM和ECM的位置是通过CAT和PMT中的条件访问描述子确定。表1介绍了条件描述子。

EMM信息包的位置是通过CAT表中的描述子确定。ECM信息包的位置确定稍微复杂一些。当在PES流层加扰,出现在PES流中ECM信息被反映到TS 流的PMT中,ECM的条件描述子就出现在PMT中。当在TS层加扰,ECM不出现在PES流中,如果条件信息通过复接加入TS流,ECM的条件描述子就出现在PMT中;如果条件信息没有通过复接加入TS流,确定ECM的位置可以有2种方法:一种方法是复接时在PMT中预先加入ECM条件描述子,用他确定 TS流中ECM的位置,本文就是采用这种方法;另一种方法是也用CAT中的条件描述子确定ECM信息包的位置,通过CA_system_ID辨别ECM和EMM。

实现CAS时还要注意以下一些限制:

(1)仅在PES层或TS层加扰,不要两层同时加扰。

(2)加扰的PES包头不允许超过184 B。

(3)携带PES包的TS包,除了含有PES包尾的可以有自适应域外,其他的不可以含有自适应域。

(4)PID等于MPEG-2规范的条件描述子CA_PID值的TS包,应仅含有条件系统信息,不能携带其他信息。另一方面,条件信息不应该出现在其他地方,例如自适应域等。

(5)在同一个TS中,两个CA提供商不应该使用相同的CA_PID。

为了避免客户端解扰设备太复杂,DVB(DigitalVideo Broadcasting)对在PES层加扰做了前3条限制;广播数据跨越媒体边界(例如从有线广播到卫星广播)时需要新的CA信息替换原有的CA信息,为了灵活高效地进行CA信息替换,DVB做了后2条限制。

解扰只是加扰的逆过程,并且相对简单,所以下面只对条件接收系统加扰过程的FPGA实现进行讨论。

1 数字电视条件接收系统(CAS)的工作原理

1.1 CAS的加扰和解扰

在采用MPEG-2的数字电视中,加扰过程就是用一个由控制字CW控制的伪随机序列对PES流或TS流进行扰动,使没有被授权的用户不能观看节目。对于授权用户,他们的接收机也有一个同样的伪随机序列产生器,如果接收到正确的CW,就可以生成解扰序列,解除信号的扰动,恢复出接收机可以播放的信号。

1.2 CAS的加密和解密

用户解扰的关键就是得到正确的CW,而CW是随着有用信号通过公用的信道传输。所以说,CAS的加密实际就是对CW的加密,以防止非授权用户的侵入。结合图1介绍CW的加解密机制。

CW一方面控制加扰器对数据流加扰;另一方面通过业务密钥SK(Server Key)加密形成授权控制信息ECM送到接收端。为了信号的保密性,CW一般几秒就要改变一次,并且SK也必须进行加密保护。一般来说,对SK加密完全按照各个用户的特征来进行。由于每台接收机可以编惟一的接收机号,所以可通过此序号生成个人分配密钥PDK(Personal DistributionKey)对SK加密,形成授权管理信息EMM。PDK由CA系统设备产生并严格控制,在接收端不能被用户读出。本文采用的方法是在接收端把PDK装入FPGA芯片中,增加保密性。为了能提供不同级别、不同类型的服务,一套CA系统往往为每个用户分配好几个PDK,来满足丰富的业务需求。EMM是用户管理信息和SK等通过PDK加密形成。用户管理信息由服务商的用户管理系统形成,包括用户名称、地址、智能卡号等。EMM平均每 8~10 s插入传送流一次,以便新开机用户解扰。解扰是加扰的逆过程,首先是用户插入IC卡,输入用户密码,如果密码正确PDK就会对SK进行解密;然后,由SK 对ECM解密出控制字CW。

2 条件接收系统的FPGA实现

FPGA(Field Programmable Gate Array)有丰富的触发器和I/O口可以满足完成CAS功能,开发周期短,可以反复修改,特别适合需不断完善电路的开发阶段。

要实现CAS硬件设计,首先要理解程序特殊信息PSI。PSI能从多节目的TS流中找出所需要的节目码流和条件接收信息等。PSI必须以一定的频率不断发送,至少20次/s,以便新开的接收机能及时解释传送流的性质。PSI由4个表组成,包括:程序关联表(PAT)、程序映射表(PMT)、网络信息表(NIT)以及条件访问表(CAT)。其中CAT和PMT与条件接收有关。条件接收信息EMM和ECM的位置是通过CAT和PMT中的条件访问描述子确定。表1介绍了条件描述子。

EMM信息包的位置是通过CAT表中的描述子确定。ECM信息包的位置确定稍微复杂一些。当在PES流层加扰,出现在PES流中ECM信息被反映到TS 流的PMT中,ECM的条件描述子就出现在PMT中。当在TS层加扰,ECM不出现在PES流中,如果条件信息通过复接加入TS流,ECM的条件描述子就出现在PMT中;如果条件信息没有通过复接加入TS流,确定ECM的位置可以有2种方法:一种方法是复接时在PMT中预先加入ECM条件描述子,用他确定 TS流中ECM的位置,本文就是采用这种方法;另一种方法是也用CAT中的条件描述子确定ECM信息包的位置,通过CA_system_ID辨别ECM和EMM。

实现CAS时还要注意以下一些限制:

(1)仅在PES层或TS层加扰,不要两层同时加扰。

(2)加扰的PES包头不允许超过184 B。

(3)携带PES包的TS包,除了含有PES包尾的可以有自适应域外,其他的不可以含有自适应域。

(4)PID等于MPEG-2规范的条件描述子CA_PID值的TS包,应仅含有条件系统信息,不能携带其他信息。另一方面,条件信息不应该出现在其他地方,例如自适应域等。

(5)在同一个TS中,两个CA提供商不应该使用相同的CA_PID。

为了避免客户端解扰设备太复杂,DVB(DigitalVideo Broadcasting)对在PES层加扰做了前3条限制;广播数据跨越媒体边界(例如从有线广播到卫星广播)时需要新的CA信息替换原有的CA信息,为了灵活高效地进行CA信息替换,DVB做了后2条限制。

解扰只是加扰的逆过程,并且相对简单,所以下面只对条件接收系统加扰过程的FPGA实现进行讨论。

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 基于FPGA的MPEG-2复用器中FIFO的一种设计方案(07-22)

- 基于FPGA的数字电视CAS系统设计(07-24)

- 用CPLD和外部SRAM构成大容量FIFO的设计(07-29)

- 地面数字电视符号与载波同步的FPGA实现(08-01)

- 采用基于FPGA的SoC进行数字显示系统设计(08-05)