基于FPGA的判决反馈均衡器的设计与实现

时间:08-02

来源:互联网

点击:

4.3误差控制函数运算模块

误差控制函数运算模块主要完成判决输出以及误差控制函数的运算。不同的抽头更新算法在于误差控制函数的不同。判决器的功能是进行误差判决,判决器判决部分比较简单,由于二进制数采用补码表示,判决和误差的计算都可以用组合电路来实现。

4.4抽头系数调整模块

本模块完成抽头系数的自适应调整,模块主要由系数移位寄存器和系数调整运算模块组成。

(1)系数移位寄存器

对于前馈寄存器,相应的输入移位寄存器有32节,则系数移位寄存器也有32节。设置一个初始系数装入输出端,32个系数输入端,32个系数输出端,复位信号有效时,所有寄存器清零,初始系数串行装入,装入7个初始系数需要7个时钟周期,在装入使能有效时,每来一个时钟上升沿,装入一个系数,先装入 的系数右移动一个寄存器,如果系数调整使能有效,则每来一个时钟上升沿就把来自系数调整运算模块调整后的系数并行装入到系数移位寄存器中。

对于反馈系数,移位寄存器有64节,移位原理同前馈滤波器。

(2)系数运算调整

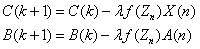

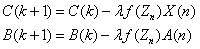

抽头系数的调整可按上式来计算,其中 为 时刻前抽头系数向量, 为 时刻反馈抽头系数向量, 为输入数据向量, 为判决器输出向量, 为误差控制函数计算模块的输出。

对于前馈抽头系数,输入的前一个时刻的系数来自前馈系数移位寄存器输出的系数,每来一个时钟,系数调整一次。 为宽度12位,精度为10位的数据, 为宽度为九位,精度为0位的数据,两者输入到一个12×9乘法器相乘后,得到宽度为11+8+1=20位,精度为10位的数据。由于在误差控制模块中计算 时,只取了低9位,小数点右移了15位,现在把小数点左移15位得到宽度为26,精度为25的数据。截取高16位,得到宽度为16、精度为15的系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,这里系数极小,所以不必考虑进位,得到一个宽度为16位、精度为15位的差,即调整后的系数,输出到前馈系数移位寄存器。

对于反馈抽头系数,输入的前一个时刻的系数来自反馈系数移位寄存器输出的系数。每来一个时钟,系数调整一次。 为宽度为2、精度为0的数据, 为宽度9位、精度0位的数据,两者输入到一个2×9乘法器相乘后,得到宽度为1+8+1=10位、精度为0位的乘积。同样把小数点左移15位,得到系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,得到一个调整后的系数,宽度16位、精度15位。

4.5 FPGA实现

整个设计全部用verilog HDL语言实现,FPGA芯片采用XC2VP70,采用Synplify Pro 7.7进行综合,ncverilog 5.0进行功能仿真,ISE6.3生成布线文件。根据综合结果对设计进行了优化,最后系统显示最高频率可到80M,上板测试功能正常,系统延迟控制在35us范围以内,可以满足绝大多数高速无线数据通讯系统对均衡器的要求。

5 总结

本文作者创新点:针对高速无线数据通讯的实时性要求,提出采用FPGA来实现可配置均衡器的设计,在设计过程中采用自顶而下划分的设计方式,即方便了设计的需要,同时又满足了性能的要求,在实际项目中收到很好的效果。

误差控制函数运算模块主要完成判决输出以及误差控制函数的运算。不同的抽头更新算法在于误差控制函数的不同。判决器的功能是进行误差判决,判决器判决部分比较简单,由于二进制数采用补码表示,判决和误差的计算都可以用组合电路来实现。

4.4抽头系数调整模块

本模块完成抽头系数的自适应调整,模块主要由系数移位寄存器和系数调整运算模块组成。

(1)系数移位寄存器

对于前馈寄存器,相应的输入移位寄存器有32节,则系数移位寄存器也有32节。设置一个初始系数装入输出端,32个系数输入端,32个系数输出端,复位信号有效时,所有寄存器清零,初始系数串行装入,装入7个初始系数需要7个时钟周期,在装入使能有效时,每来一个时钟上升沿,装入一个系数,先装入 的系数右移动一个寄存器,如果系数调整使能有效,则每来一个时钟上升沿就把来自系数调整运算模块调整后的系数并行装入到系数移位寄存器中。

对于反馈系数,移位寄存器有64节,移位原理同前馈滤波器。

(2)系数运算调整

抽头系数的调整可按上式来计算,其中 为 时刻前抽头系数向量, 为 时刻反馈抽头系数向量, 为输入数据向量, 为判决器输出向量, 为误差控制函数计算模块的输出。

对于前馈抽头系数,输入的前一个时刻的系数来自前馈系数移位寄存器输出的系数,每来一个时钟,系数调整一次。 为宽度12位,精度为10位的数据, 为宽度为九位,精度为0位的数据,两者输入到一个12×9乘法器相乘后,得到宽度为11+8+1=20位,精度为10位的数据。由于在误差控制模块中计算 时,只取了低9位,小数点右移了15位,现在把小数点左移15位得到宽度为26,精度为25的数据。截取高16位,得到宽度为16、精度为15的系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,这里系数极小,所以不必考虑进位,得到一个宽度为16位、精度为15位的差,即调整后的系数,输出到前馈系数移位寄存器。

对于反馈抽头系数,输入的前一个时刻的系数来自反馈系数移位寄存器输出的系数。每来一个时钟,系数调整一次。 为宽度为2、精度为0的数据, 为宽度9位、精度0位的数据,两者输入到一个2×9乘法器相乘后,得到宽度为1+8+1=10位、精度为0位的乘积。同样把小数点左移15位,得到系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,得到一个调整后的系数,宽度16位、精度15位。

4.5 FPGA实现

整个设计全部用verilog HDL语言实现,FPGA芯片采用XC2VP70,采用Synplify Pro 7.7进行综合,ncverilog 5.0进行功能仿真,ISE6.3生成布线文件。根据综合结果对设计进行了优化,最后系统显示最高频率可到80M,上板测试功能正常,系统延迟控制在35us范围以内,可以满足绝大多数高速无线数据通讯系统对均衡器的要求。

5 总结

本文作者创新点:针对高速无线数据通讯的实时性要求,提出采用FPGA来实现可配置均衡器的设计,在设计过程中采用自顶而下划分的设计方式,即方便了设计的需要,同时又满足了性能的要求,在实际项目中收到很好的效果。

- 数字下变频的FPGA实现(05-12)

- 用FPGA实现音频采样率的转换(02-07)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA实现变采样率FIR滤波器的研究(04-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)