基于FPGA的以太网视频广播接收系统的设计

时间:08-02

来源:互联网

点击:

一、引言

近年来,现场可编程门阵列(FPGA)技术以其独有的优势,在电子设计领域得到越来越广泛的应用。FPGA除具有集成度高、体积小、功耗低、电路简单、可靠性高等优点外,还有自身突出的优点,即“现场可编程性”,用户可以很方便地通过相应的软件,在较短时间内对FPGA内部逻辑反复设计或修改,直到满意为止。这就大大缩短了开发周期,提高了最终产品的性能。

以太网是最广泛使用的网络标准。它成为最受欢迎的技术,不仅因为其在市场上最低的NIC(网络接口卡)和HUB端口价格,还因为它具有维护简单、易于扩充等优点。

本文介绍的视频广播接收系统是基于标准以太网(10 Mbps)和快速以太网(100 Mbps)的系统。由于系统的主要部分采用了FPGA设计技术,使得系统的成本较低和开发周期较短,而且由于前端采用的是具有10M/100M兼容的芯片,并同时支持两种特性的以太网(全双工和半双工),有助于实现全双工和半双工以太网之间的无缝连接,从而使得该系统具有广阔的应用前景和实用性。

二、基本原理

系统实现中涉及到网络方面的许多相关技术和各种相关的协议、标准,下面作一简要介绍。

1.CSMA/CD协议

以太网用载波侦听多路访问/冲突检测(CSMA/CD)作为它的媒体访问控制协议,CSMA/CD定义了以太网节点为传输数据如何获得对网络媒体的访问。其工作过程如下:

(1)如果介质空闲,则传输数据,否则,转(2);

(2)如果介质忙,则坚持侦听,直到介质空闲,立即传送数据;

(3)如果在传送过程中,检测到冲突发生,发送一个短的阻塞码,以确保让所有终端都检测到冲突发生,然后停止发送;

(4)发送完阻塞码后,等待一个随机时间,再试图重新发送,即转(1)。

目前,实际使用较多的冲突检测方法是终端发送器把数据发送到线缆上,终端接收器又把数据接收回来和发送的数据比较,判别是否一致,若一致,没有冲突;若不一致,表示冲突发生。

2.以太网帧格式

当应用程序用UDP(TCP)传送数据时,数据被送入协议栈中,然后逐个通过每一层直到被当作一串比特流送入网络,其中每一层对收到的数据都要增加一些首部信息(有时还要增加尾部信息)。UDP传给IP的数据单元称作UDP报文段或简称为UDP段,IP传给网络接口层的数据单元称作IP数据报。

在OSI模型中,数据链路层传输的数据单位是帧。同样,以太网CSMA/CD也是通过帧来发送实际数据的。以太网802.3u的MAC子层定义了帧结构,如图1所示。

其中:前导码用于物理信号的同步,为7个字节的10101010序列和1个字节的10101011序列;目的地址和源地址使用的是MAC地址,前3个字节称为Block ID,它标志生产设备的厂家并由IEEE赋值;后3个字节称为设备ID,它由厂家赋值,而且总是唯一的;数据长度指要传送的数据的总长度;数据和填充字符可以从0到1 500字节不等,若实际数据小于所需的最小长度,MAC将追加一些可变的填充字符(PAD),以维持64字节的最小帧规模。若数据比1 500字节长,则更高层(一般是第三层)将把数据字段分成不同的帧进行传送;帧校验用来确保进行正确的传送,循环冗余校验(CRC)用来进行有效帧的检查。在以太网数据包的数据部分,包含了各种上层协议的首部。在本文的系统中,包含了IP首部和UDP首部。

3.介质无关接口(MII)

MII是一个用于互连控制器和收发器的全新介质无关接口,它是100 Mbit/s快速以太网开发工作的一个组成部分。此接口提供了新的物理连接机制以及控制器和收发器的功能划分。该接口主要由以下一些信号组成:

(1)发送信号

包括半字节宽(Nibble-wide)的发送数据信号,加上相关的发送时钟、发送允许信号和发送差错信号。数据用时钟同步,时钟率是数据率的1/4 (即100 Mbit/s以太网用25 MHz的时钟),发送信号用于将数据从控制器移动到收发器,然后编码并发送到LAN上。

(2)接收信号

包括半字节宽的接收数据,加上相关的接收时钟、接收数据有效信号和接收差错信号。数据用时钟同步,时钟率是数据率的1/4。接收信号用于将解码的数据从收发器移动到控制器。

(3)以太网控制信号

这些信号是由收发器生成的载波侦听和冲突检测信号,用于控制器做介质访问控制。它们只用于半双工模式,在全双工模式中被忽略。

(4)管理信号

包括一个串行管理I/O信号和相关的时钟信号。用于在控制器和收发器之间双向交换配置和控制的管理信息。

三、系统设计

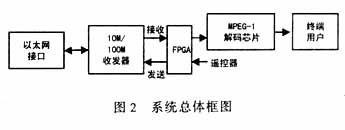

该系统实现的总体框图如图2所示。

其中以太网接口采用的是传统的RJ45接口,10M/100M收发器可以采用DM9101 单片实现,FPGA部分采用的是Xilinx公司的Spartan II系列的芯片,MPEG-1解码芯片采用了C-Cube公司的解码芯片。10M/100M收发器到FPGA之间采用MII标准的接口,FPGA到 MPEG-1解码芯片之间采用I2S形式的接口。

近年来,现场可编程门阵列(FPGA)技术以其独有的优势,在电子设计领域得到越来越广泛的应用。FPGA除具有集成度高、体积小、功耗低、电路简单、可靠性高等优点外,还有自身突出的优点,即“现场可编程性”,用户可以很方便地通过相应的软件,在较短时间内对FPGA内部逻辑反复设计或修改,直到满意为止。这就大大缩短了开发周期,提高了最终产品的性能。

以太网是最广泛使用的网络标准。它成为最受欢迎的技术,不仅因为其在市场上最低的NIC(网络接口卡)和HUB端口价格,还因为它具有维护简单、易于扩充等优点。

本文介绍的视频广播接收系统是基于标准以太网(10 Mbps)和快速以太网(100 Mbps)的系统。由于系统的主要部分采用了FPGA设计技术,使得系统的成本较低和开发周期较短,而且由于前端采用的是具有10M/100M兼容的芯片,并同时支持两种特性的以太网(全双工和半双工),有助于实现全双工和半双工以太网之间的无缝连接,从而使得该系统具有广阔的应用前景和实用性。

二、基本原理

系统实现中涉及到网络方面的许多相关技术和各种相关的协议、标准,下面作一简要介绍。

1.CSMA/CD协议

以太网用载波侦听多路访问/冲突检测(CSMA/CD)作为它的媒体访问控制协议,CSMA/CD定义了以太网节点为传输数据如何获得对网络媒体的访问。其工作过程如下:

(1)如果介质空闲,则传输数据,否则,转(2);

(2)如果介质忙,则坚持侦听,直到介质空闲,立即传送数据;

(3)如果在传送过程中,检测到冲突发生,发送一个短的阻塞码,以确保让所有终端都检测到冲突发生,然后停止发送;

(4)发送完阻塞码后,等待一个随机时间,再试图重新发送,即转(1)。

目前,实际使用较多的冲突检测方法是终端发送器把数据发送到线缆上,终端接收器又把数据接收回来和发送的数据比较,判别是否一致,若一致,没有冲突;若不一致,表示冲突发生。

2.以太网帧格式

当应用程序用UDP(TCP)传送数据时,数据被送入协议栈中,然后逐个通过每一层直到被当作一串比特流送入网络,其中每一层对收到的数据都要增加一些首部信息(有时还要增加尾部信息)。UDP传给IP的数据单元称作UDP报文段或简称为UDP段,IP传给网络接口层的数据单元称作IP数据报。

在OSI模型中,数据链路层传输的数据单位是帧。同样,以太网CSMA/CD也是通过帧来发送实际数据的。以太网802.3u的MAC子层定义了帧结构,如图1所示。

其中:前导码用于物理信号的同步,为7个字节的10101010序列和1个字节的10101011序列;目的地址和源地址使用的是MAC地址,前3个字节称为Block ID,它标志生产设备的厂家并由IEEE赋值;后3个字节称为设备ID,它由厂家赋值,而且总是唯一的;数据长度指要传送的数据的总长度;数据和填充字符可以从0到1 500字节不等,若实际数据小于所需的最小长度,MAC将追加一些可变的填充字符(PAD),以维持64字节的最小帧规模。若数据比1 500字节长,则更高层(一般是第三层)将把数据字段分成不同的帧进行传送;帧校验用来确保进行正确的传送,循环冗余校验(CRC)用来进行有效帧的检查。在以太网数据包的数据部分,包含了各种上层协议的首部。在本文的系统中,包含了IP首部和UDP首部。

3.介质无关接口(MII)

MII是一个用于互连控制器和收发器的全新介质无关接口,它是100 Mbit/s快速以太网开发工作的一个组成部分。此接口提供了新的物理连接机制以及控制器和收发器的功能划分。该接口主要由以下一些信号组成:

(1)发送信号

包括半字节宽(Nibble-wide)的发送数据信号,加上相关的发送时钟、发送允许信号和发送差错信号。数据用时钟同步,时钟率是数据率的1/4 (即100 Mbit/s以太网用25 MHz的时钟),发送信号用于将数据从控制器移动到收发器,然后编码并发送到LAN上。

(2)接收信号

包括半字节宽的接收数据,加上相关的接收时钟、接收数据有效信号和接收差错信号。数据用时钟同步,时钟率是数据率的1/4。接收信号用于将解码的数据从收发器移动到控制器。

(3)以太网控制信号

这些信号是由收发器生成的载波侦听和冲突检测信号,用于控制器做介质访问控制。它们只用于半双工模式,在全双工模式中被忽略。

(4)管理信号

包括一个串行管理I/O信号和相关的时钟信号。用于在控制器和收发器之间双向交换配置和控制的管理信息。

三、系统设计

该系统实现的总体框图如图2所示。

其中以太网接口采用的是传统的RJ45接口,10M/100M收发器可以采用DM9101 单片实现,FPGA部分采用的是Xilinx公司的Spartan II系列的芯片,MPEG-1解码芯片采用了C-Cube公司的解码芯片。10M/100M收发器到FPGA之间采用MII标准的接口,FPGA到 MPEG-1解码芯片之间采用I2S形式的接口。

FPGA 电子 电路 收发器 Xilinx 解码器 仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)