基于FPGA的以太网MAC子层协议设计实现

时间:07-31

来源:互联网

点击:

传统以PC为中心的互联网应用现已开始转向以嵌入式设备为中心. IA(internet appliance) 概念现在甚为流行,这表明互联网应用进入了嵌入式互联网的时代已经来临. 据网络专家预测,将来在互联网上传输的信息中,有70%来自小型嵌入式系统. 因此,对嵌入式系统接入Internet网络的研究是有必要的.

目前有两种方法可以实现单片机系统接入Internet.一种方法是利用NIC(网络控制/ 网卡) 实现网络接口,由单片机来提供所需的网络协议. 另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器) 来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据. 美国Seiko Instrument 公司生产的S7600A 就是具有这种结构的芯片. 与此同时,用FPGA实现单片机系统接入Internet的方法也日益受到人们的重视.

FPGA是现场可编程门阵列的缩写,是近年来发展迅速的大规模可编程器件,具有密度高,速度快,功耗小、使用方便等特点 ,在嵌入式系统设计中得到了广泛的应用. 以MCU 为核心,采用FPGA 设计实现外围电路,不仅可以使设计的电子产品小型化、集成化和实现高可靠性,还大大缩短了设计周期,减少了设计费用,降低了设计风险. 本文提出采用FPGA实现网络协议栈,着重介绍以太网MAC 子层协议的硬件实现方法.

1 以太网MAC 子层协议

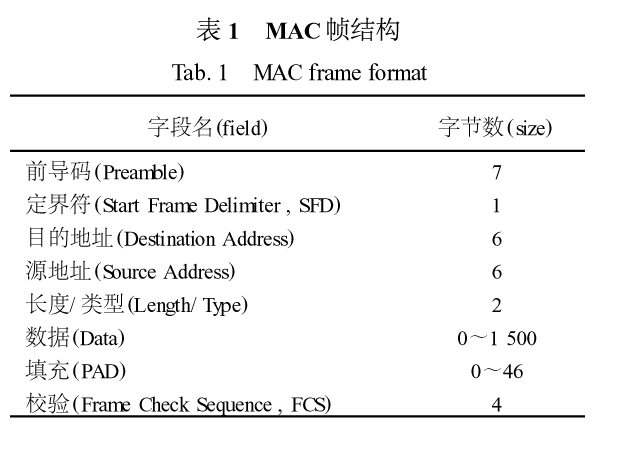

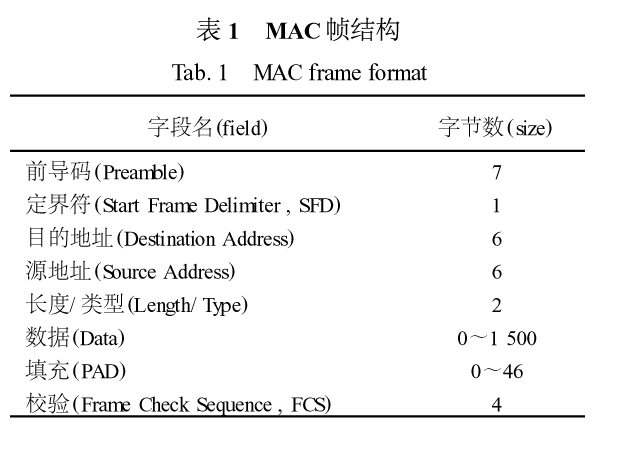

IEEE802协议标准系列中,数据链路层包括逻辑链路控制(LLC) 子层和媒体访问控制(MAC) 子层. 其中MAC 位于LLC 和物理层之间,它使LLC 适应于不同的媒体访问技术和物理媒体. MAC 单独作为一个子层,就不会因为媒体访问方法的改变而影响较高层次的协议. MAC 由数据拆装和媒体访问管理两个模块组成,完成数据帧的封装、解封、发送和接收功能.以太网数据帧封装格式如表1 所示,其中目的地址、源地址、长度/ 类型和数据4 个字段由上一层协议模块生成. 传送数据帧时,数据封装模块自动在待传输数据前面添加7 个字节的前导码和1 个字节的定界符,并在数据传送结束时加发4 个字节的循环冗余校验码,如果数据长度小于46 字节,则会自动进行数据填充以达到要求的最短长度. 接收数据帧时,数据拆装模块将自动丢弃前导码和定界符2 个字段.

媒体访问管理模块主要实现CSMA/CD(carrier sense multiple access with collision detection) 协议 . CSMA/CD 是一种分布式介质访问控制协议,使网中的多个站(节点) 可以共享传输介质. 发送数据帧时,节点首先进行载波监听,当介质空闲时开始发送帧. 如果在传输过程中与其他节点产生冲突,则正在传输的每个节点必须发出32 比特大小的阻塞信号来加强冲突,以便通知总线上各个站点已发生冲突,然后随机延时一段时间重新争用介质,再重新传送数据帧.

2 MAC 子层协议的FPGA 实现

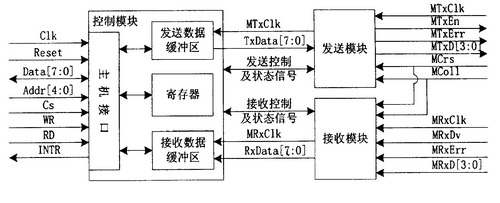

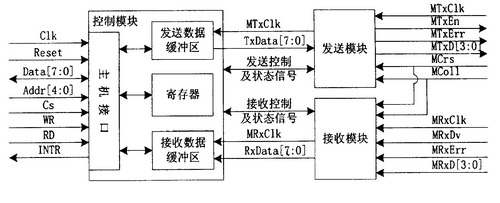

以太网MAC 子层协议的硬件结构框图如图1 所示,由控制模块、发送模块和接收模块3个部分组成. 由于小型嵌入式系统主要应用在集散控制系统中,信息交流多为“一问一答”式的半双工通信模式,同时为了降低硬件资源的开销,本模块仅支持半双工通信模式.

图1 硬件结构框图

2. 1 控制模块

该模块包含主机接口、寄存器、发送数据缓冲区及接收数据缓冲区4 个部分. 主机接口部分用以实现与MCU 之间的数据交换,采用8 位外部数据总线. 寄存器主要用于功能参数的设置及状态信息的存贮. 发送数据缓冲区是主机与发送模块之间的数据传输通道,接收数据缓冲区则是主机与接收模块之间的数据传输通道.

控制模块的工作时钟有两种选择方式,一种是直接由外部提供,另一种是外部时钟通过FPGA 片内的延迟锁相环进行倍频后供内部使用,用户可以根据系统设计实际需要自由选择.

数据缓冲区(发送数据缓冲区和接收数据缓冲区) 用作发送与接收数据的缓冲,以使主机的传输速度与本模块相匹配. 发送数据时,主机先将待发送的数据帧写入发送数据缓冲区,然后由发送模块将数据读出. 传统意义上的数据缓冲区由一块内部或外部RAM来实现,但这样需要设计实现一个复杂的控制状态机来管理主机、发送模块和接收模块3 个部分对RAM的读写. Spartan Ⅱ系列的FPGA 内部提供了丰富的块RAM资源,可以配置双端口RAM. 因此本文将发送缓冲区分成两个独立的部分,这样每个数据缓冲区便可以由双端口的RAM来实现,大大简化了设计,节省了硬件资源.

2. 2 发送模块

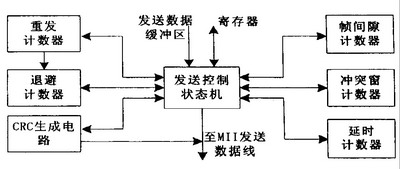

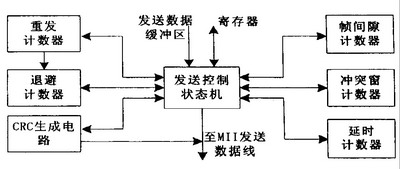

该模块主要实现CSMA/CD 协议,完成数据帧的传送,即以字节为单位从发送缓冲区读取数据,并将其转换成4 比特的半位元传送给以太网的物理层PHY芯片,结构框图如图2 所示.重发计数器用以存贮当前帧成功传输时的发送次数. 帧间隙计数器用以保证相邻两个帧之间保持一定的传输时间间隔. 冲突窗计数器用以判断当前所发生的冲突是否为后冲突(late collision) . 延时计数器用以存贮启动传输后等待总线空闲的时间,当超过一定时间后将放弃当前帧的传输.这4 个功能子模块都由1个计数器和1个比较器来实现. 退避计数器模块用以实现二进制指数退避算法,包括一个伪随机数生成器. CRC 生成电路用以实现数据帧的校验码序列,采用4 位数据线并行方式实现.

图2 发送模块结构框图

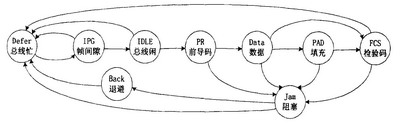

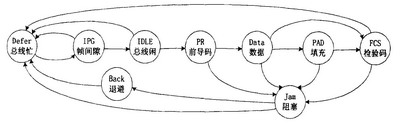

发送控制状态机是整个发送模块的核心,用以管理各个功能子模块,并使它们按照一定的时序协同工作,其状态图如图3 所示. 当总线被其他站点占用进行数据传输时,发送模块处于Defer 状态,如果此时数据准备好需要传输则启动延时计数器,经过规定的最大延时时间后总线仍被占用则放弃当前帧的传输. 当总线空闲后则进入IPG状态,经过最小帧间间隙时间自动进入空闲状态IDLE 并等待数据传输,此时如果数据准备好并且数据的长度大于46 字节则按照前导码、数据、校验序列的顺序进行数据帧的传输,否则按照前导码、数据、数据填充、校验序列的顺序进行数据帧的传输;在传输过程中,如果遇到冲突则进入Jam 状态,发送32 比特的阻塞信号加强冲突以保证网络的各个站点都可以检测到此次的冲突,如果此次冲突是后冲突则直接进入Defer状态,并丢弃当前帧,否则进入Back状态,随机延时一段时间后重新争用总线来传输当前帧.

图3 发送控制状态机

2. 3 接收模块

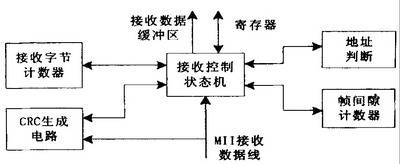

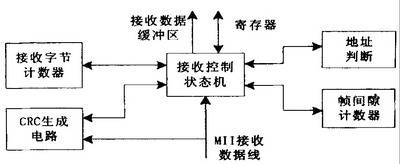

该模块主要完成数据帧的接收, 即从物理层PHY芯片接收4比特半位元数据,将其转化成以字节为单位的数据并存贮在接收数据缓冲区,结构框图如图4 所示.

图4 接收模块结构框图

图4中的地址判断子模块用以检查帧的目的地址字段是否与本站地址相匹配,如果不匹配,则说明不是发送给本站的而将它丢弃掉. 帧间隙计数器用以检测接收到的数据帧与前一帧之间是否满足最小帧间间隔的要求,如果不满足则将它丢弃. 接收字节计数器用以存贮接收帧的字节长度,判断接收帧长度是否满足要求(在最小帧长度与最大帧长度之间) . CRC 生成电路与发送模块一样采用4 位数据线并行方式实现.

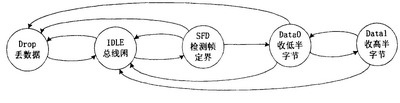

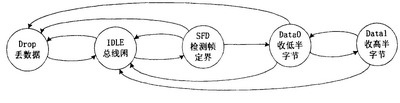

接收控制状态机是整个接收模块的核心,负责管理各个功能子模块,检测总线及实现接收数据帧的时序,其状态图如图5 所示. 通常接收模块处于IDLE 状态并监听总线的状态,当检测到以太网帧的前导码时自动进入SFD 状态,此时如果接收到以太网数据帧的帧定界符,并且与前一个数据帧之间的时间间隔大于最小帧间间隙,则接收模块进入数据接收状态开始接收数据. 处于Data0 状态时接收字节的低4 位,而处于Datal 状态时接收字节的高4 位,并在Data0 状态将接收到的完整字节数据存贮到接收数据缓冲区.如果接收的数据字节数超过允许的最大帧长度,则接收模块进入Drop 状态,此时丢弃后面的数据. 当全部数据传输完毕即总线处于空闲时,接收模块重新处于IDLE 状态,等待接收下一个数据帧.

图5 接收控制状态图

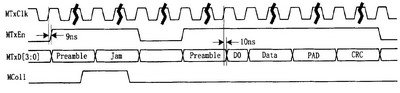

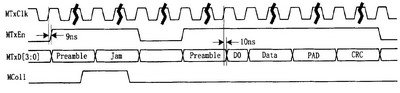

3 综合与仿真

本文采用Xilinx 公司的Spartan Ⅱ系列XC2S100PQ208芯片,整个设计全部采用Verilog HDL 硬件描述语言来实现,并在Foundation3. 1 的设计平台上完成整个模块的设计、综合、仿真、映射及布局布线. 图6为发送时序仿真的波形,从图中可以看出,当传输过程中发生冲突时继续发送32 比特的阻塞码,然后随机延时一段时间重新争用介质以传输数据,这说明本模块满足了CSMA/ CD 协议.

图6 发送时序仿真波形

4 结语

本文介绍了一种简易的基于FPGA 的以太网MAC 子层协议的设计方法. 通过本模块可以简单方便地实现小型嵌入式系统的Internet 网络接口,如果再结合基于FPGA 实现的TCP/ IP 协议栈及其他辅助功能模块,不仅可以使小型嵌入式系统接入网络更加简单,而且系统的集成度、稳定性将进一步得到提高.

目前有两种方法可以实现单片机系统接入Internet.一种方法是利用NIC(网络控制/ 网卡) 实现网络接口,由单片机来提供所需的网络协议. 另外一种方法是利用具有网络协议栈结构的芯片和PHY(物理层的接收器) 来实现网络接口,主控制器只负责往协议栈结构芯片的某个寄存器里放上适当的数据. 美国Seiko Instrument 公司生产的S7600A 就是具有这种结构的芯片. 与此同时,用FPGA实现单片机系统接入Internet的方法也日益受到人们的重视.

FPGA是现场可编程门阵列的缩写,是近年来发展迅速的大规模可编程器件,具有密度高,速度快,功耗小、使用方便等特点 ,在嵌入式系统设计中得到了广泛的应用. 以MCU 为核心,采用FPGA 设计实现外围电路,不仅可以使设计的电子产品小型化、集成化和实现高可靠性,还大大缩短了设计周期,减少了设计费用,降低了设计风险. 本文提出采用FPGA实现网络协议栈,着重介绍以太网MAC 子层协议的硬件实现方法.

1 以太网MAC 子层协议

IEEE802协议标准系列中,数据链路层包括逻辑链路控制(LLC) 子层和媒体访问控制(MAC) 子层. 其中MAC 位于LLC 和物理层之间,它使LLC 适应于不同的媒体访问技术和物理媒体. MAC 单独作为一个子层,就不会因为媒体访问方法的改变而影响较高层次的协议. MAC 由数据拆装和媒体访问管理两个模块组成,完成数据帧的封装、解封、发送和接收功能.以太网数据帧封装格式如表1 所示,其中目的地址、源地址、长度/ 类型和数据4 个字段由上一层协议模块生成. 传送数据帧时,数据封装模块自动在待传输数据前面添加7 个字节的前导码和1 个字节的定界符,并在数据传送结束时加发4 个字节的循环冗余校验码,如果数据长度小于46 字节,则会自动进行数据填充以达到要求的最短长度. 接收数据帧时,数据拆装模块将自动丢弃前导码和定界符2 个字段.

媒体访问管理模块主要实现CSMA/CD(carrier sense multiple access with collision detection) 协议 . CSMA/CD 是一种分布式介质访问控制协议,使网中的多个站(节点) 可以共享传输介质. 发送数据帧时,节点首先进行载波监听,当介质空闲时开始发送帧. 如果在传输过程中与其他节点产生冲突,则正在传输的每个节点必须发出32 比特大小的阻塞信号来加强冲突,以便通知总线上各个站点已发生冲突,然后随机延时一段时间重新争用介质,再重新传送数据帧.

2 MAC 子层协议的FPGA 实现

以太网MAC 子层协议的硬件结构框图如图1 所示,由控制模块、发送模块和接收模块3个部分组成. 由于小型嵌入式系统主要应用在集散控制系统中,信息交流多为“一问一答”式的半双工通信模式,同时为了降低硬件资源的开销,本模块仅支持半双工通信模式.

图1 硬件结构框图

2. 1 控制模块

该模块包含主机接口、寄存器、发送数据缓冲区及接收数据缓冲区4 个部分. 主机接口部分用以实现与MCU 之间的数据交换,采用8 位外部数据总线. 寄存器主要用于功能参数的设置及状态信息的存贮. 发送数据缓冲区是主机与发送模块之间的数据传输通道,接收数据缓冲区则是主机与接收模块之间的数据传输通道.

控制模块的工作时钟有两种选择方式,一种是直接由外部提供,另一种是外部时钟通过FPGA 片内的延迟锁相环进行倍频后供内部使用,用户可以根据系统设计实际需要自由选择.

数据缓冲区(发送数据缓冲区和接收数据缓冲区) 用作发送与接收数据的缓冲,以使主机的传输速度与本模块相匹配. 发送数据时,主机先将待发送的数据帧写入发送数据缓冲区,然后由发送模块将数据读出. 传统意义上的数据缓冲区由一块内部或外部RAM来实现,但这样需要设计实现一个复杂的控制状态机来管理主机、发送模块和接收模块3 个部分对RAM的读写. Spartan Ⅱ系列的FPGA 内部提供了丰富的块RAM资源,可以配置双端口RAM. 因此本文将发送缓冲区分成两个独立的部分,这样每个数据缓冲区便可以由双端口的RAM来实现,大大简化了设计,节省了硬件资源.

2. 2 发送模块

该模块主要实现CSMA/CD 协议,完成数据帧的传送,即以字节为单位从发送缓冲区读取数据,并将其转换成4 比特的半位元传送给以太网的物理层PHY芯片,结构框图如图2 所示.重发计数器用以存贮当前帧成功传输时的发送次数. 帧间隙计数器用以保证相邻两个帧之间保持一定的传输时间间隔. 冲突窗计数器用以判断当前所发生的冲突是否为后冲突(late collision) . 延时计数器用以存贮启动传输后等待总线空闲的时间,当超过一定时间后将放弃当前帧的传输.这4 个功能子模块都由1个计数器和1个比较器来实现. 退避计数器模块用以实现二进制指数退避算法,包括一个伪随机数生成器. CRC 生成电路用以实现数据帧的校验码序列,采用4 位数据线并行方式实现.

图2 发送模块结构框图

发送控制状态机是整个发送模块的核心,用以管理各个功能子模块,并使它们按照一定的时序协同工作,其状态图如图3 所示. 当总线被其他站点占用进行数据传输时,发送模块处于Defer 状态,如果此时数据准备好需要传输则启动延时计数器,经过规定的最大延时时间后总线仍被占用则放弃当前帧的传输. 当总线空闲后则进入IPG状态,经过最小帧间间隙时间自动进入空闲状态IDLE 并等待数据传输,此时如果数据准备好并且数据的长度大于46 字节则按照前导码、数据、校验序列的顺序进行数据帧的传输,否则按照前导码、数据、数据填充、校验序列的顺序进行数据帧的传输;在传输过程中,如果遇到冲突则进入Jam 状态,发送32 比特的阻塞信号加强冲突以保证网络的各个站点都可以检测到此次的冲突,如果此次冲突是后冲突则直接进入Defer状态,并丢弃当前帧,否则进入Back状态,随机延时一段时间后重新争用总线来传输当前帧.

图3 发送控制状态机

2. 3 接收模块

该模块主要完成数据帧的接收, 即从物理层PHY芯片接收4比特半位元数据,将其转化成以字节为单位的数据并存贮在接收数据缓冲区,结构框图如图4 所示.

图4 接收模块结构框图

图4中的地址判断子模块用以检查帧的目的地址字段是否与本站地址相匹配,如果不匹配,则说明不是发送给本站的而将它丢弃掉. 帧间隙计数器用以检测接收到的数据帧与前一帧之间是否满足最小帧间间隔的要求,如果不满足则将它丢弃. 接收字节计数器用以存贮接收帧的字节长度,判断接收帧长度是否满足要求(在最小帧长度与最大帧长度之间) . CRC 生成电路与发送模块一样采用4 位数据线并行方式实现.

接收控制状态机是整个接收模块的核心,负责管理各个功能子模块,检测总线及实现接收数据帧的时序,其状态图如图5 所示. 通常接收模块处于IDLE 状态并监听总线的状态,当检测到以太网帧的前导码时自动进入SFD 状态,此时如果接收到以太网数据帧的帧定界符,并且与前一个数据帧之间的时间间隔大于最小帧间间隙,则接收模块进入数据接收状态开始接收数据. 处于Data0 状态时接收字节的低4 位,而处于Datal 状态时接收字节的高4 位,并在Data0 状态将接收到的完整字节数据存贮到接收数据缓冲区.如果接收的数据字节数超过允许的最大帧长度,则接收模块进入Drop 状态,此时丢弃后面的数据. 当全部数据传输完毕即总线处于空闲时,接收模块重新处于IDLE 状态,等待接收下一个数据帧.

图5 接收控制状态图

3 综合与仿真

本文采用Xilinx 公司的Spartan Ⅱ系列XC2S100PQ208芯片,整个设计全部采用Verilog HDL 硬件描述语言来实现,并在Foundation3. 1 的设计平台上完成整个模块的设计、综合、仿真、映射及布局布线. 图6为发送时序仿真的波形,从图中可以看出,当传输过程中发生冲突时继续发送32 比特的阻塞码,然后随机延时一段时间重新争用介质以传输数据,这说明本模块满足了CSMA/ CD 协议.

图6 发送时序仿真波形

4 结语

本文介绍了一种简易的基于FPGA 的以太网MAC 子层协议的设计方法. 通过本模块可以简单方便地实现小型嵌入式系统的Internet 网络接口,如果再结合基于FPGA 实现的TCP/ IP 协议栈及其他辅助功能模块,不仅可以使小型嵌入式系统接入网络更加简单,而且系统的集成度、稳定性将进一步得到提高.

嵌入式 单片机 FPGA MCU 电路 电子 总线 比较器 仿真 Xilinx Verilog 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)