基于FPGA的数控振荡器的设计与实现

时间:07-24

来源:互联网

点击:

数控振荡器的仿真结果及性能分析

利用Altera公司的QuartusII软件,采用VHDL硬件描述语言对上述数控振荡器结构进行描述,在Modlesim上通过功能仿真,结果正确后综合出电路网表,最后将程序下载至Altera公司生产的Stratix器件EP1S20B780C6实现。

由于设计中采用了Stratix器件,该器件的32位加减器工作频率可以达到90MHz以上,为产生高速的正交信号提供高速可靠的的工作时钟。考虑到NCO的工作时钟瓶颈是在相位累加器,因此可以根据具体需要缩减相位累加器的位数来提高NCO的工作时钟。本文设计的NCO工作时钟为100MHz,相位累加器的位数为16位,输入的频率控制字为4CCCH,根据公式:

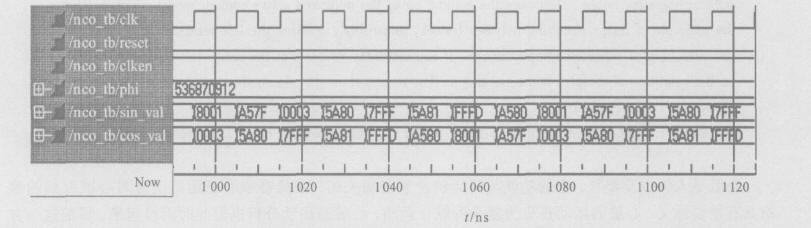

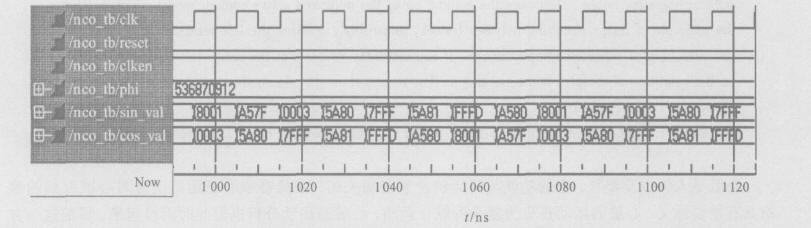

其中:Φword为输入的频率控制字;fclk为工作时钟;N为相位累加器位数,可算出NCO输出的正余弦信号的频率;fout为30MHz ;频率分辨率Δf ≈1.5 kHz。频率分辨率说明了若通过输入频率控制字来改变输出正余弦信号的频率时,可以达到1.5 kHz 的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。当然,NCO输出频率的上限要受到Nyquist定律的限制,即fout的最大值为fclkP2,实际设计一般不大于0.4fclk。图3为数控振荡器的部分仿真时序图。

图3 NCO的部分仿真时序图

结语

研究了正交数字混频器中数控振荡器的设计与实现方法,着重分析了如何在FPGA器件中利用CORDIC迭代算法产生正余弦信号。结果表明,基于CORDIC迭代算法的数控振荡器,仅用移位寄存器和加法器就可产生正余弦信号,不但省去了传统NCO庞大的存储器资源,而且保留了一般数控振荡器频率分辨率高、频率变化速度快、相位可连续线性变化、生成的正弦P余弦信号正交特性好等特点,非常适用于在正交数字混频器中进行高速高精度的数字调制解调。

利用Altera公司的QuartusII软件,采用VHDL硬件描述语言对上述数控振荡器结构进行描述,在Modlesim上通过功能仿真,结果正确后综合出电路网表,最后将程序下载至Altera公司生产的Stratix器件EP1S20B780C6实现。

由于设计中采用了Stratix器件,该器件的32位加减器工作频率可以达到90MHz以上,为产生高速的正交信号提供高速可靠的的工作时钟。考虑到NCO的工作时钟瓶颈是在相位累加器,因此可以根据具体需要缩减相位累加器的位数来提高NCO的工作时钟。本文设计的NCO工作时钟为100MHz,相位累加器的位数为16位,输入的频率控制字为4CCCH,根据公式:

其中:Φword为输入的频率控制字;fclk为工作时钟;N为相位累加器位数,可算出NCO输出的正余弦信号的频率;fout为30MHz ;频率分辨率Δf ≈1.5 kHz。频率分辨率说明了若通过输入频率控制字来改变输出正余弦信号的频率时,可以达到1.5 kHz 的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。当然,NCO输出频率的上限要受到Nyquist定律的限制,即fout的最大值为fclkP2,实际设计一般不大于0.4fclk。图3为数控振荡器的部分仿真时序图。

图3 NCO的部分仿真时序图

结语

研究了正交数字混频器中数控振荡器的设计与实现方法,着重分析了如何在FPGA器件中利用CORDIC迭代算法产生正余弦信号。结果表明,基于CORDIC迭代算法的数控振荡器,仅用移位寄存器和加法器就可产生正余弦信号,不但省去了传统NCO庞大的存储器资源,而且保留了一般数控振荡器频率分辨率高、频率变化速度快、相位可连续线性变化、生成的正弦P余弦信号正交特性好等特点,非常适用于在正交数字混频器中进行高速高精度的数字调制解调。

振荡器 FPGA 电路 滤波器 无线电 仿真 Altera Quartus VHDL 相关文章:

- 数字下变频的FPGA实现(05-12)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的相检宽带测频系统的设计(06-08)

- ACEX 1K系列CPLD配置方法探讨(06-09)