用CAM实现OC-48线速字符串匹配的FPGA设计

时间:07-22

来源:互联网

点击:

互联网络蓬勃发展的今天,在网络入侵检测系统(NIDS)中,大部分的网络入侵检测设备几乎都依赖于一些基于特征码检测的字符串匹配算法,而字符串匹配算法的实现几乎都是由软件来实现的。目前应用比较成功的实例有,Snort软件使用字符串匹配算法对包含特征码的数据包进行检测。但是软件在内容字节流中进行搜索匹配时,需要在不同的处理单元中/内搬移或读取数据,这对于高速实现线速(OC-48)的检测系统来说,带来了很大的处理负荷。因此,如果采用硬件在数据包进入内存之前实现字符串匹配这一功能,将大大减少后端软件操作的处理负载。

基于IXP2400和FPGA的系统结构

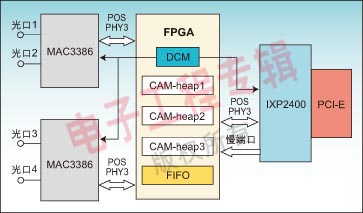

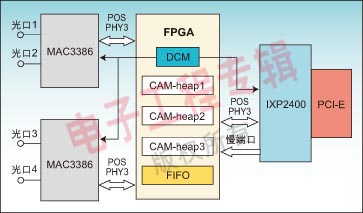

IXP2400是英特尔公司推出的第二代网络处理器芯片,大量应用于宽带接入、防火墙、NIDS和负载均衡等系统中,它能满足OC-48网络线速的处理要求。玉衡铱达公司设计开发的骨干网络监控系统采用了IXP2400作为数据包主处理器,FPGA作为协处理器的硬件架构来实现,系统结构框图如图1所示。

如图1所示,系统外接了4个千兆光口,用以接收和发送数据包,它是整个监控系统和骨干网络的交际通道。光口数据包通过光模块进入PMC-Sierra公司的MAC3386芯片。接收数据包时,以太网帧数据包从千兆光口进入MAC3386,MAC3386对数据包进行解码后通过POS PHY3接口进入FPGA的FIFO单元,同时对进入FPGA的数据包进行模式字符串(Pattern-String)的匹配操作,处理后的数据包通过POS PHY3接口传输到IXP2400的MSF单元进行下一步的处理。发送时,FPGA只需要将IXP2400发送来的数据包通过POS PHY3接口传输给MAC3386,MAC3386对数据包进行编码后发送给光模块,光模块通过光口将数据包发送出去。IXP2400提供了一组数据总线来访问外部设备寄存器,IXP2400中称之为慢端口(Slow Port)。在这里,和FPGA相连的慢端口总线的一部分功能是作为写入FPGA的模式字符串通道。

图1:基于IXP2400和FPGA的系统结构示意图。

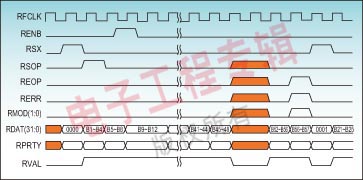

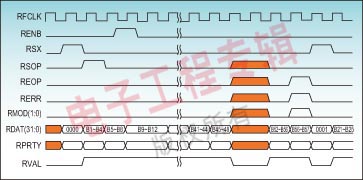

POS PHY3是一种标准化的网络传输接口,接口数据传输速率为2.5Gbps,最大支持OC-48的传输速率接口。POS PHY3包括接收和发送两组32位总线,工作频率为104MHz,峰值吞吐率为3.2Gbps。支持2.5Gbps数据包的全双工操作。POS PHY3接口接收时序图如图2所示。

图2:POS PHY3接口接收逻辑时序图。

该时序图描述了POS PHY3接口接收数据包时,数据流在POS PHY3总线上的传输方式和相关的控制信号关系。关于更进一步的详细描述可以参考POS PHY3接口标准文档。

系统采用时钟同步设计,在时钟上升沿进行数据采样,与FPGA相连的MAC3386、IXP2400的工作时钟由FPGA的DCM单元提供,可以保证数据采集的同步和稳定性。

CAM的设计

本设计中,由于要实现几路32B的模式字符串匹配,需要占用大量的RAM存储单元,同时还得为数据包缓存FIFO保留一定的存储单元,综合几家FPGA芯片厂商RAM的存储容量,决定选用赛灵思的Virtex2或Virtex Pro系列的FPGA芯片,因为对于相同规模的逻辑资源和寄存器资源来说, Virtex2或Virtex Pro系列的FPGA芯片的RAM容量比其他厂商都要多几倍。

FPGA中,与RAM存储单元相关的资源有三类:Block RAM、LUT、寄存器。这三类资源可以通过配置和粘合逻辑(Glue Logic)实现为不同类型和位宽大小的单端口/双端口RAM、ROM、CAM、FIFO等。FPGA中CAM的实现和配置非常灵活,CAM是实现模式字符串模式匹配的核心资源。

CAM即内容可寻址存储器。CAM这种存储器在其每个存储单元都包含了一个内嵌的比较逻辑,CAM基于内容寻址,通过硬件电路并行查找,实现快速匹配。一般来说在一个时钟周期内,写入CAM的待比较数据和其内部存储的每一个数据进行比较,并返回与端口数据相同的内部数据存储的地址和是否匹配的标识符。CAM的这种并行处理特性使得它在数据分选领域倍受青睐,被广泛应用在以太网网址搜寻、路由器中的地址交换表、高速数据处理等方面。

CAM对于高速的数据包模式字符串匹配查找操作来说,我们需要足够快的时间来完成,如果按照POS PHY3接口标准来说,必须保证寄存器建立(Setup)时间和CAM一次查找匹配时间之和小于1个周期10ns(一般情况下,FPGA设计中的保持(Hold Up)时间都可以满足,可以不予考虑)。根据FPGA芯片厂商数据手册提供的性能基准数据,我们配置CAM存储器选用的资源是Block RAM,配置的地址匹配类型选择的是非编码地址的多匹配方式(Multi Match Unencoded),选用该项配置的CAM32_32完成一次匹配查找的操作时间为7ns左右,CAM32_32的配置大小是32位位宽,32个存储单元的地址深度。

对于POS PHY3的接口标准来说,数据传输操作周期为10ns,根据性能基准数据,我们因此除去寄存器的建立时间(<2ns),完成一次CAM匹配操作是完全可以和POS PHY3的接口标准相匹配的。根据数据包在POS PHY3接口的传输字节情况和实际设计需要,我们设计了一个CAM-heap来完成数据包的一路32B模式字符串的匹配操作。一个CAM-heap是由4个相同结构和配置的CAM32_32组成。CAM32_32是根据设计需要由自己配置定义的,其配置端口示意图如图3所示。

图3:CAM32_32端口示意图。

基于IXP2400和FPGA的系统结构

IXP2400是英特尔公司推出的第二代网络处理器芯片,大量应用于宽带接入、防火墙、NIDS和负载均衡等系统中,它能满足OC-48网络线速的处理要求。玉衡铱达公司设计开发的骨干网络监控系统采用了IXP2400作为数据包主处理器,FPGA作为协处理器的硬件架构来实现,系统结构框图如图1所示。

如图1所示,系统外接了4个千兆光口,用以接收和发送数据包,它是整个监控系统和骨干网络的交际通道。光口数据包通过光模块进入PMC-Sierra公司的MAC3386芯片。接收数据包时,以太网帧数据包从千兆光口进入MAC3386,MAC3386对数据包进行解码后通过POS PHY3接口进入FPGA的FIFO单元,同时对进入FPGA的数据包进行模式字符串(Pattern-String)的匹配操作,处理后的数据包通过POS PHY3接口传输到IXP2400的MSF单元进行下一步的处理。发送时,FPGA只需要将IXP2400发送来的数据包通过POS PHY3接口传输给MAC3386,MAC3386对数据包进行编码后发送给光模块,光模块通过光口将数据包发送出去。IXP2400提供了一组数据总线来访问外部设备寄存器,IXP2400中称之为慢端口(Slow Port)。在这里,和FPGA相连的慢端口总线的一部分功能是作为写入FPGA的模式字符串通道。

图1:基于IXP2400和FPGA的系统结构示意图。

POS PHY3是一种标准化的网络传输接口,接口数据传输速率为2.5Gbps,最大支持OC-48的传输速率接口。POS PHY3包括接收和发送两组32位总线,工作频率为104MHz,峰值吞吐率为3.2Gbps。支持2.5Gbps数据包的全双工操作。POS PHY3接口接收时序图如图2所示。

图2:POS PHY3接口接收逻辑时序图。

该时序图描述了POS PHY3接口接收数据包时,数据流在POS PHY3总线上的传输方式和相关的控制信号关系。关于更进一步的详细描述可以参考POS PHY3接口标准文档。

系统采用时钟同步设计,在时钟上升沿进行数据采样,与FPGA相连的MAC3386、IXP2400的工作时钟由FPGA的DCM单元提供,可以保证数据采集的同步和稳定性。

CAM的设计

本设计中,由于要实现几路32B的模式字符串匹配,需要占用大量的RAM存储单元,同时还得为数据包缓存FIFO保留一定的存储单元,综合几家FPGA芯片厂商RAM的存储容量,决定选用赛灵思的Virtex2或Virtex Pro系列的FPGA芯片,因为对于相同规模的逻辑资源和寄存器资源来说, Virtex2或Virtex Pro系列的FPGA芯片的RAM容量比其他厂商都要多几倍。

FPGA中,与RAM存储单元相关的资源有三类:Block RAM、LUT、寄存器。这三类资源可以通过配置和粘合逻辑(Glue Logic)实现为不同类型和位宽大小的单端口/双端口RAM、ROM、CAM、FIFO等。FPGA中CAM的实现和配置非常灵活,CAM是实现模式字符串模式匹配的核心资源。

CAM即内容可寻址存储器。CAM这种存储器在其每个存储单元都包含了一个内嵌的比较逻辑,CAM基于内容寻址,通过硬件电路并行查找,实现快速匹配。一般来说在一个时钟周期内,写入CAM的待比较数据和其内部存储的每一个数据进行比较,并返回与端口数据相同的内部数据存储的地址和是否匹配的标识符。CAM的这种并行处理特性使得它在数据分选领域倍受青睐,被广泛应用在以太网网址搜寻、路由器中的地址交换表、高速数据处理等方面。

CAM对于高速的数据包模式字符串匹配查找操作来说,我们需要足够快的时间来完成,如果按照POS PHY3接口标准来说,必须保证寄存器建立(Setup)时间和CAM一次查找匹配时间之和小于1个周期10ns(一般情况下,FPGA设计中的保持(Hold Up)时间都可以满足,可以不予考虑)。根据FPGA芯片厂商数据手册提供的性能基准数据,我们配置CAM存储器选用的资源是Block RAM,配置的地址匹配类型选择的是非编码地址的多匹配方式(Multi Match Unencoded),选用该项配置的CAM32_32完成一次匹配查找的操作时间为7ns左右,CAM32_32的配置大小是32位位宽,32个存储单元的地址深度。

对于POS PHY3的接口标准来说,数据传输操作周期为10ns,根据性能基准数据,我们因此除去寄存器的建立时间(<2ns),完成一次CAM匹配操作是完全可以和POS PHY3的接口标准相匹配的。根据数据包在POS PHY3接口的传输字节情况和实际设计需要,我们设计了一个CAM-heap来完成数据包的一路32B模式字符串的匹配操作。一个CAM-heap是由4个相同结构和配置的CAM32_32组成。CAM32_32是根据设计需要由自己配置定义的,其配置端口示意图如图3所示。

图3:CAM32_32端口示意图。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)