基于FPGA的雷达脉冲压缩系统设计

时间:07-18

来源:互联网

点击:

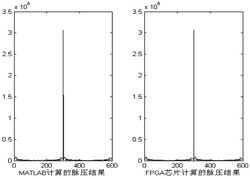

图4 1024点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

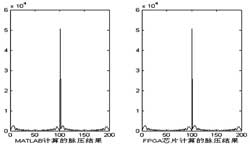

图5 512点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

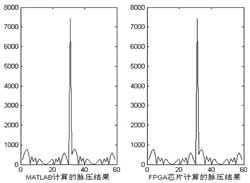

图6 256点脉冲压缩状态FPGA计算结果与MATLAB计算结果对比图

图4至图6分别对应时宽为60μs、20μs、6μs,带宽均为5M的线性调频信号。其中,左图对应MATLAB的计算结果,右图为FPGA芯片的输出结果。可以看到,FPGA芯片的输出结果和MATLAB仿真结果吻合。经测试验证结果良好,最大误差不超过-76db,在内部时钟频率80MHz条件下,完成1024点FFT 运行时间为146μs ,满足了雷达系统实时处理要求,达到了满意的效果。

- 数字下变频的FPGA实现(05-12)

- 用FPGA实现音频采样率的转换(02-07)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA实现变采样率FIR滤波器的研究(04-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)