标准单元ASIC/FPGA的权衡与结构化ASIC

时间:07-17

来源:互联网

点击:

现在有各种各样的硅资源供您选择,供应商们正在调整其标准组件产品系列以满足您的需求。

要点

● 标准单元ASIC 和FPGA 的权衡为结构化ASIc新兴公司打开了一个有争议的市场缺口。

● 结构化ASIC不只是改名换姓的门阵列,而是反映了目前的市场现实和硅片功能。

● 平台ASIC是具有硬件定制功能的ASSP。

● RapidWorx大大降低了ASIC开发工具套件的成本,而Quartus II则使其达到了FPGA工具的水平——这是一件极好的事情。

● 竞争者对手的反应是各种各样的,其它的解决办法即将出现。

看来您已认定,采取购买并组装现成的专用标准产品(ASSP),如嵌入式控制器、外设芯片等,然后再编写您自己的软件这种做法将不能使您设计的产品与您竞争对手的产品有足够大的差别。因此,您会决定选择芯片级设计。两大硅平台竞争对手及其各自的折衷方案已经在各种工业论坛上引起广泛的争论。不过如果您刚涉足这场争论,则很有必要了解下述有关争论的概要。

多种制造FPGA的深亚微米工艺,如Xilinx公司最新Spartan-3系列产品采用的90纳米工艺(参考文献1),使每块芯片上的门电路数量变得越来越大。如果您的设计使用FPGA的嵌入式存储器阵列和扩散式模拟及数字功能模块,如DLL、PLL、乘法累加器、串行器/解串行器(SERDES)电路、高速I/O缓存器,在某些情况下甚至是CPU芯核和相关外设,则FPGA的可用功能是极大的。您可以根据设计的需求来订购少量或大量的FPGA,而且不必向供应商支付NRE(非经常工程)费用。供应商已经安排并调试芯片的逻辑平面、存储器平面、信号路由平面以及电源平面。

一旦您的设计完成,你便可在几秒钟到几分钟之内拥有一块实用的芯片。一般说来,你用来开发和调试设计的工具要比用于开发调试专用集成电路(ASIC)的工具便宜许多。(然而,如果Hier设计公司售价为25,000 美元的PlanAhead代表未来工业趋势的话,FPGA工具组的平均价格将会上涨)。但是,无论FPGA变得多么密集,FPGA的面积效率仍然要比用可比工艺制造的标准单元ASIC低一到两个数量级。FPGA,尤其是基于占用大量硅面积的、每个单元六个晶体管的静态存储器(SRAM)的查寻表(LUT)和配置元件技术的FPGA,其功耗要比对等的ASIC大得多。

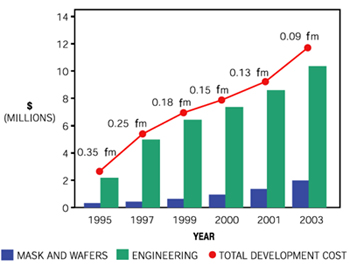

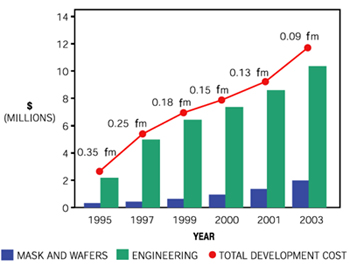

遗憾的是,ASIC的很多优点也带来相应的缺点。由于芯片按照摩尔定律光刻线路发展,NRE费用、最少订购数量以及每席开发工具套件的费用都将猛涨(图1)。ASIC的最少订购数量反映了供应商能够在生产线上生产并仍可获利的最少的用户专用晶圆。芯片的裸芯片越大,所需的最小订购数量就越小,而且您还会看到为什么改用线宽更小的光刻工艺和更大的晶圆后能大大提高这种最小批量需求。

图1 标准单元ASIC掩膜集、非经常性工程(NRE)和工具集三种费用以指数形式增长,这驱使大量潜在用户考虑各种替代办法(由Altera公司提供)。

电源电压下降、信号耦合以及深亚微米布线效应会造成种种故障,查找、修理这些故障所需的时间加上布线主导的时序收敛,都会延长标准单元ASIC的开发周期。甚至在当您认为您的设计业已完成时,您还不得不等待设计通过漫长的生产、测试以及包装等工序,然后才能取回芯片,而且,如果您设计的芯片不工作或者不再能够满足快速变化的市场需求,那就会招致成本和时间延迟的成倍增加。用标准单元ASIC进行设计需要大量的时间、劳力和金钱;正如最近的分析报告所指出的那样,造成市场向FPGA急速转移的就是这三个因素。但是对于门电路数量或芯片批量达到几十万的设计或者对于性能要求或功率要求非常严格的设计来说,标准单元的ASIC仍然是唯一的技术选择。

传统的解决方案

对此怎么做出选择呢?为了回答这一问题,首先比较一下FPGA和ASIC的基本硅标准组件,即两者的逻辑单元和布线结构。FPGA的逻辑单元都是粗粒的,从各种各样的多路复用器和分立逻辑门到一个或多个LUT,全都是粗颗粒的,并且通常由触发器作补充。Actel公司的 ProASIC FPGA目前能提供业界最细颗粒的逻辑模块。FPGA供应商设计其器件的内部逻辑模块布线,从而将所需的可由用户配置的布线层数减到最少;这样,设计编译和布局布线软件面临的主要挑战就是高效利用逻辑模块问题。您得到的芯片具有大多未编程的逻辑模块间布线资源;对于基于非熔断闪存芯片来说,这些资源您可以在系统加电之前配置,而对于基于SRAM的FPGA来说,则可在系统启动之时及之后配置(如果您的设计支持的话)。

标准单元ASIC逻辑模块与FPGA的逻辑模块相比颗粒要细得多。顾名思义,“标准单元”都采用按相同标准尺寸来制造晶体管和芯片上的其他结构。(这种同质性就是标准单元与完全定制芯片的主要差异)。然而,正如“专用”这一名称所示,ASIC的布局以及器件的时钟、电源和信号布线都是您实现方法专用的。因此,芯片的金属化层和多晶硅层对每个用户来说全都是独一无二的,而且供应商在将器件运送给您之前预先对布线进行了配置,使您在系统生产和随后的运作过程中不必具备硬件定制能力。在这种情况下,开发软件不是主要侧重于使每个逻辑模块内的设计实现方法高效率,就像更粗颗粒的FPGA一样,但却要侧重于逻辑模块互连的高效率。

从历史看,另一种ASIC——门阵列——介于FPGA和标准单元ASIC这两个极端之间。与FPGA类似,门阵列的布线网格是通用而又预定的。和标准单元一样,这种布线网格专门设计配置在芯片生产的最后几个阶段进行,而且供应商有时将细颗粒的逻辑单元阵列称为“双输入‘与非’门之海”。近几年,曾经被广泛应用的门阵列已经逐渐消失,随着FPGA逐步蚕食其领地,门阵列已经越来越明显地成为万事通而无专长现象的牺牲品。就从订购到使用的周转时间而言,门阵列比标准单元快得还不够,无法夺取大量FPGA的业务。而且,门阵列的性能和硅片面积效率太差,使它们无法取代很多标准单元。

要点

● 标准单元ASIC 和FPGA 的权衡为结构化ASIc新兴公司打开了一个有争议的市场缺口。

● 结构化ASIC不只是改名换姓的门阵列,而是反映了目前的市场现实和硅片功能。

● 平台ASIC是具有硬件定制功能的ASSP。

● RapidWorx大大降低了ASIC开发工具套件的成本,而Quartus II则使其达到了FPGA工具的水平——这是一件极好的事情。

● 竞争者对手的反应是各种各样的,其它的解决办法即将出现。

看来您已认定,采取购买并组装现成的专用标准产品(ASSP),如嵌入式控制器、外设芯片等,然后再编写您自己的软件这种做法将不能使您设计的产品与您竞争对手的产品有足够大的差别。因此,您会决定选择芯片级设计。两大硅平台竞争对手及其各自的折衷方案已经在各种工业论坛上引起广泛的争论。不过如果您刚涉足这场争论,则很有必要了解下述有关争论的概要。

多种制造FPGA的深亚微米工艺,如Xilinx公司最新Spartan-3系列产品采用的90纳米工艺(参考文献1),使每块芯片上的门电路数量变得越来越大。如果您的设计使用FPGA的嵌入式存储器阵列和扩散式模拟及数字功能模块,如DLL、PLL、乘法累加器、串行器/解串行器(SERDES)电路、高速I/O缓存器,在某些情况下甚至是CPU芯核和相关外设,则FPGA的可用功能是极大的。您可以根据设计的需求来订购少量或大量的FPGA,而且不必向供应商支付NRE(非经常工程)费用。供应商已经安排并调试芯片的逻辑平面、存储器平面、信号路由平面以及电源平面。

一旦您的设计完成,你便可在几秒钟到几分钟之内拥有一块实用的芯片。一般说来,你用来开发和调试设计的工具要比用于开发调试专用集成电路(ASIC)的工具便宜许多。(然而,如果Hier设计公司售价为25,000 美元的PlanAhead代表未来工业趋势的话,FPGA工具组的平均价格将会上涨)。但是,无论FPGA变得多么密集,FPGA的面积效率仍然要比用可比工艺制造的标准单元ASIC低一到两个数量级。FPGA,尤其是基于占用大量硅面积的、每个单元六个晶体管的静态存储器(SRAM)的查寻表(LUT)和配置元件技术的FPGA,其功耗要比对等的ASIC大得多。

遗憾的是,ASIC的很多优点也带来相应的缺点。由于芯片按照摩尔定律光刻线路发展,NRE费用、最少订购数量以及每席开发工具套件的费用都将猛涨(图1)。ASIC的最少订购数量反映了供应商能够在生产线上生产并仍可获利的最少的用户专用晶圆。芯片的裸芯片越大,所需的最小订购数量就越小,而且您还会看到为什么改用线宽更小的光刻工艺和更大的晶圆后能大大提高这种最小批量需求。

图1 标准单元ASIC掩膜集、非经常性工程(NRE)和工具集三种费用以指数形式增长,这驱使大量潜在用户考虑各种替代办法(由Altera公司提供)。

电源电压下降、信号耦合以及深亚微米布线效应会造成种种故障,查找、修理这些故障所需的时间加上布线主导的时序收敛,都会延长标准单元ASIC的开发周期。甚至在当您认为您的设计业已完成时,您还不得不等待设计通过漫长的生产、测试以及包装等工序,然后才能取回芯片,而且,如果您设计的芯片不工作或者不再能够满足快速变化的市场需求,那就会招致成本和时间延迟的成倍增加。用标准单元ASIC进行设计需要大量的时间、劳力和金钱;正如最近的分析报告所指出的那样,造成市场向FPGA急速转移的就是这三个因素。但是对于门电路数量或芯片批量达到几十万的设计或者对于性能要求或功率要求非常严格的设计来说,标准单元的ASIC仍然是唯一的技术选择。

传统的解决方案

对此怎么做出选择呢?为了回答这一问题,首先比较一下FPGA和ASIC的基本硅标准组件,即两者的逻辑单元和布线结构。FPGA的逻辑单元都是粗粒的,从各种各样的多路复用器和分立逻辑门到一个或多个LUT,全都是粗颗粒的,并且通常由触发器作补充。Actel公司的 ProASIC FPGA目前能提供业界最细颗粒的逻辑模块。FPGA供应商设计其器件的内部逻辑模块布线,从而将所需的可由用户配置的布线层数减到最少;这样,设计编译和布局布线软件面临的主要挑战就是高效利用逻辑模块问题。您得到的芯片具有大多未编程的逻辑模块间布线资源;对于基于非熔断闪存芯片来说,这些资源您可以在系统加电之前配置,而对于基于SRAM的FPGA来说,则可在系统启动之时及之后配置(如果您的设计支持的话)。

标准单元ASIC逻辑模块与FPGA的逻辑模块相比颗粒要细得多。顾名思义,“标准单元”都采用按相同标准尺寸来制造晶体管和芯片上的其他结构。(这种同质性就是标准单元与完全定制芯片的主要差异)。然而,正如“专用”这一名称所示,ASIC的布局以及器件的时钟、电源和信号布线都是您实现方法专用的。因此,芯片的金属化层和多晶硅层对每个用户来说全都是独一无二的,而且供应商在将器件运送给您之前预先对布线进行了配置,使您在系统生产和随后的运作过程中不必具备硬件定制能力。在这种情况下,开发软件不是主要侧重于使每个逻辑模块内的设计实现方法高效率,就像更粗颗粒的FPGA一样,但却要侧重于逻辑模块互连的高效率。

从历史看,另一种ASIC——门阵列——介于FPGA和标准单元ASIC这两个极端之间。与FPGA类似,门阵列的布线网格是通用而又预定的。和标准单元一样,这种布线网格专门设计配置在芯片生产的最后几个阶段进行,而且供应商有时将细颗粒的逻辑单元阵列称为“双输入‘与非’门之海”。近几年,曾经被广泛应用的门阵列已经逐渐消失,随着FPGA逐步蚕食其领地,门阵列已经越来越明显地成为万事通而无专长现象的牺牲品。就从订购到使用的周转时间而言,门阵列比标准单元快得还不够,无法夺取大量FPGA的业务。而且,门阵列的性能和硅片面积效率太差,使它们无法取代很多标准单元。

FPGA Quartus 嵌入式 Xilinx 电路 集成电路 Altera 电压 EDA Atmel 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)