标准单元ASIC/FPGA的权衡与结构化ASIC

时间:07-17

来源:互联网

点击:

掩膜

可编程FPGA

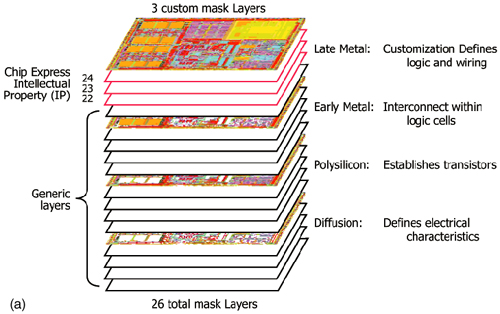

受到业务流失警示的一些ASIC供应商把FPGA窍门宝典的一些经验和门阵列的以往教训结合在一起,提出了结构化的ASIC。有人也将这种方法称为模块化阵列或结构化阵列。供应商和供应商之间存在大量的技术差别,但是简单的讲,结构化的ASIC是具有类似FPGA粗颗粒逻辑单元的门电路阵列派生产品,因而需要更少的可由用户配置的金属层和通孔层(图2)。供应商需要处理时钟树和电源平面布线。一个类比能够有助于对结构化ASIC设计的理解:在软件编程的早期,微处理器的速度非常慢,存储器非常昂贵,因此低级而又高效的汇编语言和更为低级的机器代码占据了支配地位。

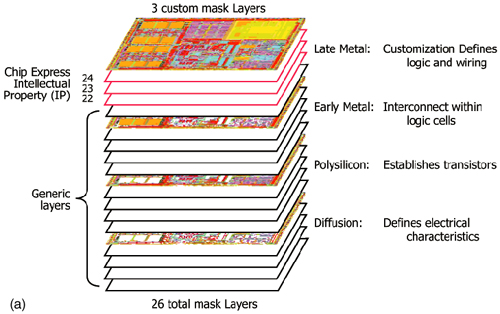

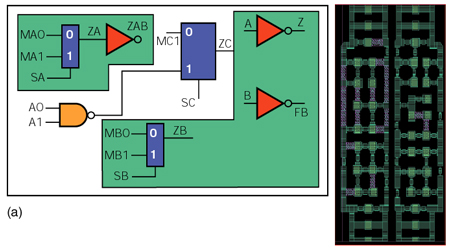

图2 通过减少用户专用掩膜的数量(a ,由ChipExpress公司提供)和金属层和通孔层(b ,由Lightspeed Semiconductor公司提供),结构化ASIC供应商声称能增强其产品的灵活性并降低每个用户的费用。

随着CPU运行速度的加快和存储器价格的下降,更高级的软件语言取代了以前的汇编语言和机器代码。它们对资源的使用效率较低,但是好在现在效率并不显得那么重要。然而,面市时间却日益重要,而高级语言在这一方面出类拔萃。由于同样的原因,VHDL和Verilog日益成为将电路变成芯片的硬件工程师们选择的设计输入方法,而更耗时的原理图输入技术则放弃使用。结构化ASIC供应商大胆地假定,将会出现一个硅平台市场,尽管硅平台可能比标准单元的效率低,面市时间比FPGA长,但是也没有那些竞争产品的所有缺点(图3)。因为芯片的掩膜——简便地说,常常也是最昂贵的掩膜——所占的百分比很大,这对于多个用户设计来说是很普通的,所以每个用户的NRE费用就会减少,周转时间就会缩短,而且你还能更容易地使由此产生的平台适应不断演进的工业标准,和适应硬件修改最少的派生芯片(图4)。

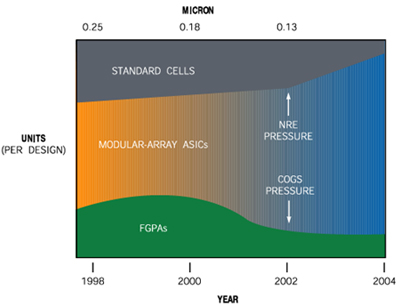

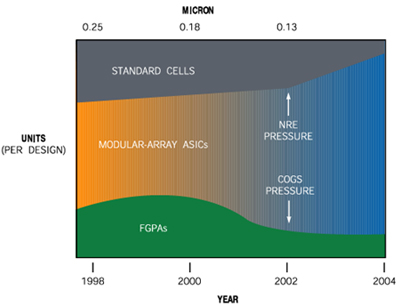

图3 结构化ASIC厂商的陈述都用图来表明他们的产品填补了标准单元ASIC和FPGA之间的空白。竞争对手则声称结构化ASIC芯片只不过是试图使濒临死亡的门阵列复活,这种尝试是注定要失败的(由Lightspeed Semiconductor公司提供)。

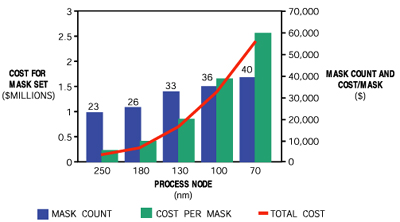

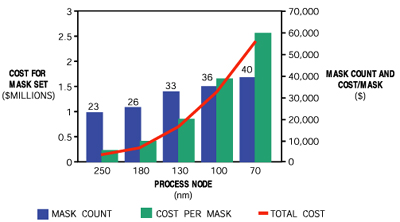

图4 掩膜集成本的增加,既反映了深亚微米工艺的每个掩膜的复杂程度逐渐增加,又反映了要求用深亚微米工艺制造芯片的掩膜制造商数量不断增加(由Lightspeed Semiconductor公司提供)。

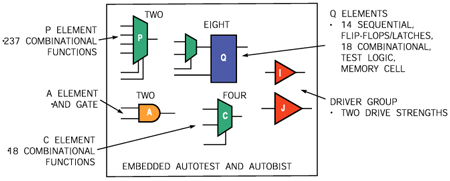

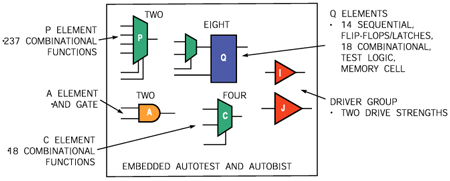

现在正在吹捧结构化ASIC器件的公司中有AMI Semiconductor公司, Chip Express公司, Faraday Technology公司, Fujitsu公司, Lightspeed Semiconductor公司, NEC公司, 和ViASIC公司。在这些公司中,目前只有AMI公司目前没有把自己定位为范围广泛的硅片供应商;该公司正在坚持向FPGA转换的有利地位,但是使用的是一种结构化ASIC基础,而不是过去的门阵列平台。相反,Lightspeed Semiconductor公司曾短暂扩入Xilinx FPGA降价市场,现已退出这一市场,将精力集中在传统的ASIC上(参考文献2)。Chip Express 公司的结构化ASIC采用各种备选方案中最细颗粒的逻辑模块;该公司估计其器件的每个逻辑模块将包含三到四个门电路,视具体设计而定。其他供应商的大多数逻辑模块能实现20~40个门的设计(图5)。

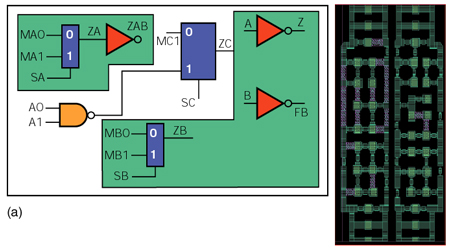

图5 结构化ASIC逻辑单元横跨从细颗粒(a)到粗颗粒( b )两种极端工艺方法(由Chip Express 公司和 Lightspeed Semiconductor公司提供)。

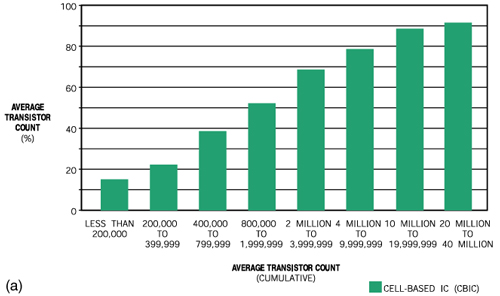

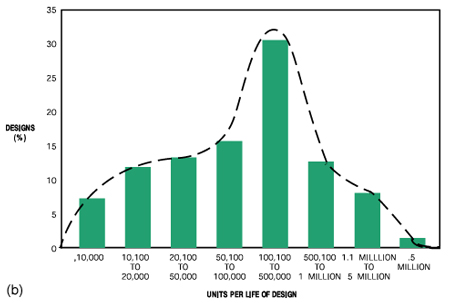

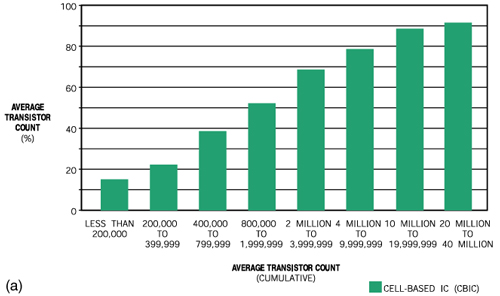

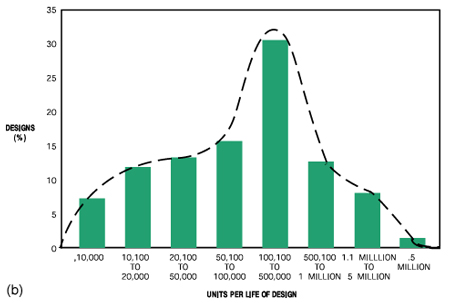

结构化ASIC供应商用各种混合的工艺制造芯。这种多样性反映了每个厂商都试图想在潜在的用户大蛋糕上占有自己单独的一份。供应商及其代工工厂摊消了他们用来开发后沿的易于理解的成品率高的0.18-微米、 0.25-微米、和0.35-微米工艺的生产设施与设备费用。您能用这些工艺实现的设计规模有个上限,但是相关的供应商指出:分析报告显示具有1百万门以下的ASIc设计占很大的百分比,同时有数据显示用户使用的ASIC设计,其中不足100000件批量的占50%(图6)。

图6 具有少量到中等数量的晶体管和门电路的设计覆盖了大多数ASIC市场(a), 大多数用户也以中小批量使用ASIC(b)( 由Xilinx 公司和 Leopard Logic 公司提供)。

在工艺技术另一端的是Fujitsu、NEC等公司。Fujitsu 公司现已将0.11微米结构化ASIC工艺投产,0.09微米工艺也将于2004年投产。NEC公司预示他们的90纳米工艺也将在2004年下半年投产。使工艺适合于设计是一种微妙的平衡行为,也涉及到了解设计的I/O缓冲器数量;供应商和用户希望发生的最后的事情是裸芯片在对最小尺寸起限制作用的I/O环路

内包含未被使用、从而浪费硅资源的区域。复杂封装的成本逐渐增加也使得封装内各种硅片的成本成比例地不相关。

结构化ASIC供应商声称从设计完成到第一个样品供使用的标准单元周转时间要从几个月缩短到几个星期。这种延迟不是从布局布线网表到FPGA提供的硅资源的几秒钟到几分钟的迟后时间,但是ASIC拥护者声称这种比较在某种意义上是苹果和桔子的比较。他们指出,随着FPGA和其内部的设计越来越复杂,工程师们为了实现区域(这个区域适合吗)和时间(它运行的足够快吗)收敛所花费的时间是指数增加的。工程师们认为,由于ASIC具有比FPGA更快的设计基础,所以花在模拟和重新设计方面的时间比较少,用结构化ASIC进行开发的总周期可能也因此而比用FPGA的更短。

可编程FPGA

受到业务流失警示的一些ASIC供应商把FPGA窍门宝典的一些经验和门阵列的以往教训结合在一起,提出了结构化的ASIC。有人也将这种方法称为模块化阵列或结构化阵列。供应商和供应商之间存在大量的技术差别,但是简单的讲,结构化的ASIC是具有类似FPGA粗颗粒逻辑单元的门电路阵列派生产品,因而需要更少的可由用户配置的金属层和通孔层(图2)。供应商需要处理时钟树和电源平面布线。一个类比能够有助于对结构化ASIC设计的理解:在软件编程的早期,微处理器的速度非常慢,存储器非常昂贵,因此低级而又高效的汇编语言和更为低级的机器代码占据了支配地位。

图2 通过减少用户专用掩膜的数量(a ,由ChipExpress公司提供)和金属层和通孔层(b ,由Lightspeed Semiconductor公司提供),结构化ASIC供应商声称能增强其产品的灵活性并降低每个用户的费用。

随着CPU运行速度的加快和存储器价格的下降,更高级的软件语言取代了以前的汇编语言和机器代码。它们对资源的使用效率较低,但是好在现在效率并不显得那么重要。然而,面市时间却日益重要,而高级语言在这一方面出类拔萃。由于同样的原因,VHDL和Verilog日益成为将电路变成芯片的硬件工程师们选择的设计输入方法,而更耗时的原理图输入技术则放弃使用。结构化ASIC供应商大胆地假定,将会出现一个硅平台市场,尽管硅平台可能比标准单元的效率低,面市时间比FPGA长,但是也没有那些竞争产品的所有缺点(图3)。因为芯片的掩膜——简便地说,常常也是最昂贵的掩膜——所占的百分比很大,这对于多个用户设计来说是很普通的,所以每个用户的NRE费用就会减少,周转时间就会缩短,而且你还能更容易地使由此产生的平台适应不断演进的工业标准,和适应硬件修改最少的派生芯片(图4)。

图3 结构化ASIC厂商的陈述都用图来表明他们的产品填补了标准单元ASIC和FPGA之间的空白。竞争对手则声称结构化ASIC芯片只不过是试图使濒临死亡的门阵列复活,这种尝试是注定要失败的(由Lightspeed Semiconductor公司提供)。

图4 掩膜集成本的增加,既反映了深亚微米工艺的每个掩膜的复杂程度逐渐增加,又反映了要求用深亚微米工艺制造芯片的掩膜制造商数量不断增加(由Lightspeed Semiconductor公司提供)。

现在正在吹捧结构化ASIC器件的公司中有AMI Semiconductor公司, Chip Express公司, Faraday Technology公司, Fujitsu公司, Lightspeed Semiconductor公司, NEC公司, 和ViASIC公司。在这些公司中,目前只有AMI公司目前没有把自己定位为范围广泛的硅片供应商;该公司正在坚持向FPGA转换的有利地位,但是使用的是一种结构化ASIC基础,而不是过去的门阵列平台。相反,Lightspeed Semiconductor公司曾短暂扩入Xilinx FPGA降价市场,现已退出这一市场,将精力集中在传统的ASIC上(参考文献2)。Chip Express 公司的结构化ASIC采用各种备选方案中最细颗粒的逻辑模块;该公司估计其器件的每个逻辑模块将包含三到四个门电路,视具体设计而定。其他供应商的大多数逻辑模块能实现20~40个门的设计(图5)。

图5 结构化ASIC逻辑单元横跨从细颗粒(a)到粗颗粒( b )两种极端工艺方法(由Chip Express 公司和 Lightspeed Semiconductor公司提供)。

结构化ASIC供应商用各种混合的工艺制造芯。这种多样性反映了每个厂商都试图想在潜在的用户大蛋糕上占有自己单独的一份。供应商及其代工工厂摊消了他们用来开发后沿的易于理解的成品率高的0.18-微米、 0.25-微米、和0.35-微米工艺的生产设施与设备费用。您能用这些工艺实现的设计规模有个上限,但是相关的供应商指出:分析报告显示具有1百万门以下的ASIc设计占很大的百分比,同时有数据显示用户使用的ASIC设计,其中不足100000件批量的占50%(图6)。

图6 具有少量到中等数量的晶体管和门电路的设计覆盖了大多数ASIC市场(a), 大多数用户也以中小批量使用ASIC(b)( 由Xilinx 公司和 Leopard Logic 公司提供)。

在工艺技术另一端的是Fujitsu、NEC等公司。Fujitsu 公司现已将0.11微米结构化ASIC工艺投产,0.09微米工艺也将于2004年投产。NEC公司预示他们的90纳米工艺也将在2004年下半年投产。使工艺适合于设计是一种微妙的平衡行为,也涉及到了解设计的I/O缓冲器数量;供应商和用户希望发生的最后的事情是裸芯片在对最小尺寸起限制作用的I/O环路

内包含未被使用、从而浪费硅资源的区域。复杂封装的成本逐渐增加也使得封装内各种硅片的成本成比例地不相关。

结构化ASIC供应商声称从设计完成到第一个样品供使用的标准单元周转时间要从几个月缩短到几个星期。这种延迟不是从布局布线网表到FPGA提供的硅资源的几秒钟到几分钟的迟后时间,但是ASIC拥护者声称这种比较在某种意义上是苹果和桔子的比较。他们指出,随着FPGA和其内部的设计越来越复杂,工程师们为了实现区域(这个区域适合吗)和时间(它运行的足够快吗)收敛所花费的时间是指数增加的。工程师们认为,由于ASIC具有比FPGA更快的设计基础,所以花在模拟和重新设计方面的时间比较少,用结构化ASIC进行开发的总周期可能也因此而比用FPGA的更短。

FPGA Quartus 嵌入式 Xilinx 电路 集成电路 Altera 电压 EDA Atmel 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)