赛灵思UltraScale架构:业界首款ASIC级All Programmable架构

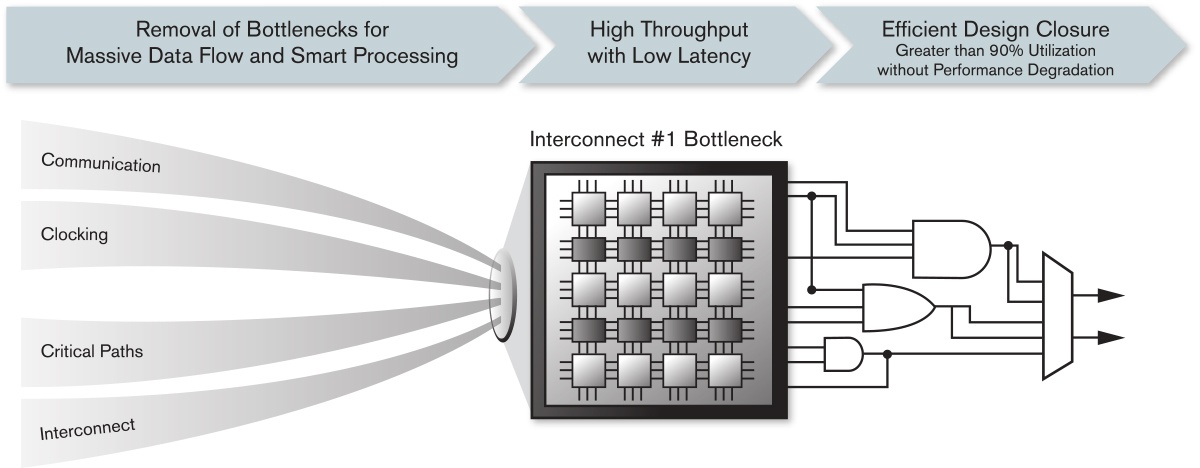

现在,人们需要采用一种创新型架构来管理数百Gbps的系统性能,以实现全线速下的智能处理能力,并扩展至Tb级性能和每秒10亿次浮点运算水平。实现上述要求的必要条件并非仅仅是改善每个晶体管或系统模块的性能,或者增加系统模块数量这么简单,而是要从根本上提高通信、时钟、关键路径以及互连性能,以满足行业新一代高性能应用(如下图所示)对海量数据流和智能数据包、DSP或图像处理等的要求。

图1 ASIC级可编程架构的必备条件

UltraScale™ 架构通过在完全可编程的架构中应用最先进的ASIC 技术,可应对上述这些挑战。该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈,即互连问题。

图2:ASIC级可编程架构的必备条件

UltraScale™架构具有无与伦比的高集成度、高容量和ASIC级系统性能,可满足最严苛应用的要求。UltraScale架构经过精调可提供大规模布线能力并且与Vivado®设计工具进行了协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。

为您量身定做的新一代架构

赛灵思对UltraScale架构进行了数百项设计提升,并将这些改进实现有机结合,让设计团队能够打造出比以往功能更强、运行速度更快、单位功耗性能更高的系统。

UltraScale架构与Vivado™设计套件结合使用可提供如下这些新一代系统级功能:

· 针对宽总线进行优化的海量数据流,可支持数Tb级吞吐量和最低时延

· 高度优化的关键路径和内置高速存储器,级联后可消除DSP和包处理中的瓶颈

· 增强型DSP slice包含27x18位乘法器和双加法器,可以显著提高定点和IEEE 754标准浮点算法的性能与效率

· 第二代3D IC系统集成的晶片间带宽以及最新3D IC宽存储器优化接口均实现阶梯式增长

· 类似于ASIC的多区域时钟,提供具备超低时钟歪斜和高性能扩展能力的低功耗时钟网络

· 海量I/O和存储器带宽,用多个硬化的ASIC级100G以太网、Interlaken和PCIe® IP核优化,可支持新一代存储器接口功能并显著降低时延

· 电源管理可对各种功能元件进行宽范围的静态与动态电源门控,实现显著节能降耗

· 新一代安全策略,提供先进的AES比特流解密与认证方法、更多密钥模糊处理功能以及安全器件编程

· 通过与Vivado工具协同优化消除布线拥塞问题,实现了90%以上的器件利用率,同时不降低性能或增大时延

系统设计人员将这些系统级功能进行多种组合,以解决各种问题。下面的宽数据路径方框图可以很好地说明这一问题。

图3:海量数据流挑战

图中,高速数据流(Tbps级的汇聚速率)从左侧进入再从右侧流出。可通过运行速度为数Gbps的高速SerDes收发器进行I/O传输。一旦以数Gbps速度传输的串行数据流进入芯片,就必须扇出,以便与片上资源的数据流、路由和处理能力相匹配。新一代系统要求使用极高的数据速率,因此时钟歪斜、大量总线布置以及系统功耗管理方面的挑战会达到令人生畏的程度。

UltraScale架构提供类似ASIC时钟功能

多亏UltraScale 架构提供类似ASIC的多区域时钟功能,使得设计人员现在可以将系统级时钟放在整个晶片的任何最佳位置上,从而使系统级时钟歪斜降低多达50%。将时钟驱动的节点放在功能模块的几何中心并且平衡不同叶节点时钟单元(leaf clock cell)的时钟歪斜,这样可以打破阻碍实现多Gb系统级性能的一个最大瓶颈。UltraScale架构的类似ASIC时钟功能消除了时钟放置方面的一切限制并且能够在系统设计中实现大量独立的高性能低歪斜时钟资源,而这正是新一代设计的关键要求之一。这是与前几代可编程逻辑器件所采用的时钟方案的最大不同之处,而且实现了重大改进。

新一代路由:从容应对海量数据流挑战

UltraScale架构的新一代互连功能与Vivado软件工具进行了协同优化,在可编程逻辑布线方面取得了真正的突破。赛灵思将精力重点放在了解和满足新一代应用对于海量数据流、多Gb智能包处理、多Tb吞吐量以及低时延方面的要求。通过分析我们得出一个结论,那就是在这些数据速率下,互连问题已成为影响系统性能的头号瓶颈。

我们来做个类比。位于市中心的一个繁忙十字路口,交通流量的方向是从北到南,从南到北,从东到西,从西到东,有些车辆正试图掉头,所

UltraScale架构 All Programmable Vivado 赛灵思 ASIC 相关文章:

- UltraScale可编程架构如何解决互连问题?(06-09)

- 常见问题解答:Xilinx采用首个ASIC级UltraScale可编程架构(06-09)

- 赛灵思ASIC级UltraScale架构要素及相关说明(06-09)

- Xilinx UltraScale:为您未来架构而打造的新一代架构(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- 全面了解英特尔融合现实Alloy 要完爆VR/AR?(07-20)