UltraScale可编程架构如何解决互连问题?

时间:06-09

来源:电子发烧友网

点击:

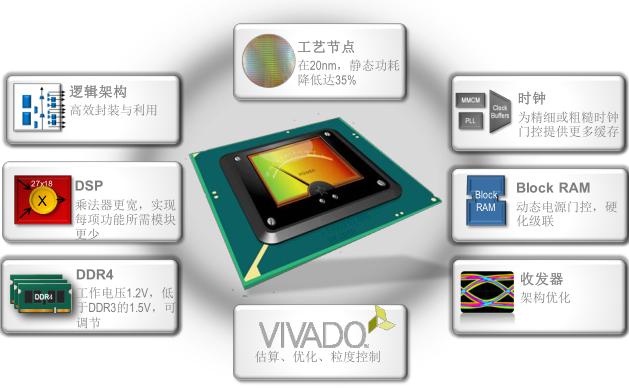

赛灵思UltraScale 架构:行业第一个ASIC 级可编程架构,可从20nm平面晶体管结构(planar)工艺向16nm乃至FinFET晶体管技术扩展,从单芯片(monolithic)到3D IC扩展。它不仅能解决整体系统吞吐量扩展限制的问题和时延问题,而且直接应对先进节点芯片性能方面的最大瓶颈问题——互连。

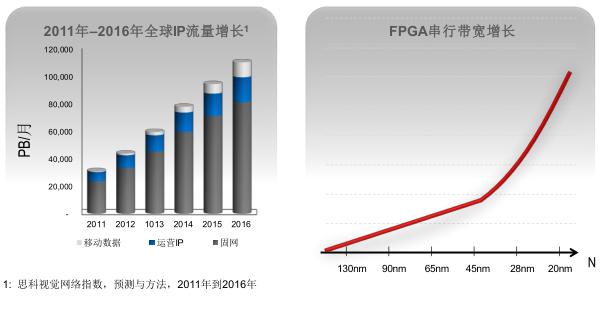

据思科视觉网络指数统计及预测分析,2011年-2016年全球IP流量快速增长,2013年达到将近6万PB/月,预计2016年将接近12万PB每月。快速增长的IP流量驱动着FPGA器件对带宽和数据流的需求,FPGA串行带宽的增长,对工艺技术同样有着紧密的联系,因此对工艺技术的需求日益增加。

ASIC级可编程架构从四大方面来解决互连问题

事实上,UltraScale架构能够从布线、时钟、关键路径及电源等四方面解决影响先进节点芯片性能方面的最大瓶颈问题——互连。

我们可以用交通堵塞问题来形容UltraScale架构所起的作用。形象地说,没使用UltraScale架构之前,有限的道路会导致主线堵塞;而有了UltraScale架构,就像右图实现智能分流一般,带来了实现"智能交通流"的新方法,从而从根本上解决了"交通堵塞"的问题,即互连问题。

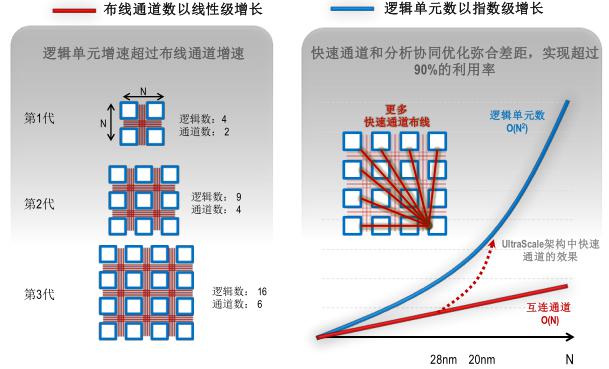

(1)增加真实有效的布线通道,有助于应对不断增加的复杂性

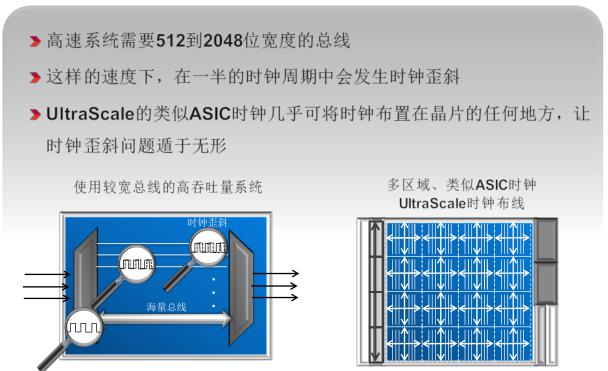

(2)类似ASIC时钟可最大化性能裕量,实现最高吞吐量

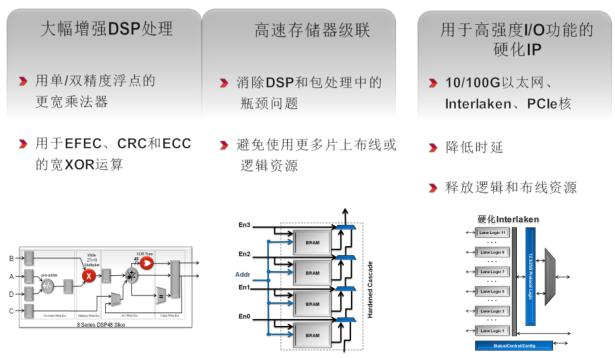

(3)高度优化的关键路径消除DSP和包处理的瓶颈问题

(4)新一代电源管理功能实现性能的飞跃

UltraScale架构 20nm 3DIC asic fpga 相关文章: