利用FPGA的自身特性实现随机数发生器

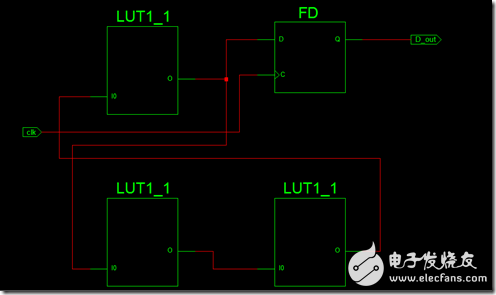

图2. 3个反相器组成的振荡器外加一个D触发器

ChipScope的观察

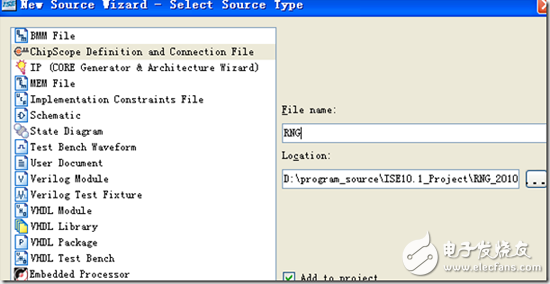

首先对管脚以及时钟进行约束,为了通过ChipScope观察随机数的输出序列,还需要添加ICON以及ILA IP core。操作如下,在ISE窗口左侧的source栏中右键选择new source,然后见到New Source Wizard窗口。输入一个名字,然后点击OK。然后在Source窗口中看到生成的cdc source file。接下来就是配置触发信号、观察信号、时钟信号等属性。

图3. New Source Wizard

这里不细说如何配置,具体见参考文献3。

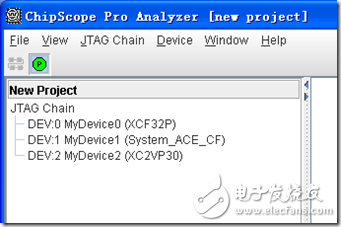

在这里,观察的RNG输出信号同时作为触发信号来配置。配置完后编译实现。然后再Process栏中选择Analyze Design Using ChipScope 同时连接Virtex-II Pro板子并且上电。进入ChipScope Pro Analyzer界面后点击工具栏中的OPEN Cable/Search JTAG Chain,然后看到JTAG Chain上的三个设备。右键选中FPGA芯片(XC2VP30),选择配置,选中刚才生成的bit文件。配置完成后会出现图5的信号列表。

图5中Trigger Setup是触发配置,Waveform 是波形列表。

图4. JTAG Chain

图5. 信号观察列表

双击 Waveform打开波形观察窗口,因为触发信号就是需要观察的信号,所以这里不用设置触发。在工具栏中点击 ,你就可以观察到随机数的输出波形了,图6。肉眼观察信号比较随机,但是没有定性的测试。

随机数的测试

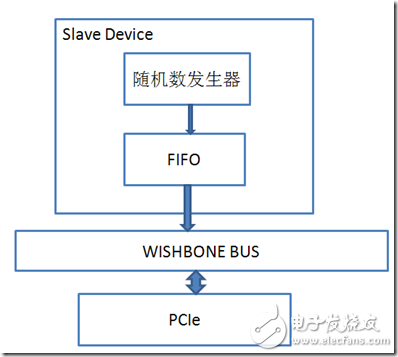

常用的测试随机数的工具有ENT[4],DIEHARD[5]等。而这些工具需要大量的随机数(最好是10M以上的数据)才可以测试,而用ChipScope最多一次只能才是65536bit的数据,这样的测试肯定是不行的。所以将同样的设计放到了PCIeV4base,这个板子具有PCIe插槽,用的是Virtex-4的FPGA芯片。PC机通过PCIe桥接芯片读取数据,这样很方便得到大量的随机数数据。

具体的原理图,图7。看起来有些麻烦,涉及到了FIFO,Wishbone上添加从设备,以及Linux下PCIe的编程,幸好相关的东西已经有实例和SDK提供,只要做一些修改就可以了。

图7. 随机数发生器作为WISHBONE BUS的从设备的原理图

最后通过软件得到15MB的数据。然后通过ENT工具进行测试,测试的结果如下:

D:\Document\RNG\ent>ent out

Entropy = 7.999890 bits per byte.

Optimum compression would reduce the size

of this 16777212 byte file by 0 percent.

Chi square distribution for 16777212 samples is 2563.57, and randomly

would exceed this value less than 0.01 percent of the times.

Arithmetic mean value of data bytes is 127.5056 (127.5 = random).

Monte Carlo value for Pi is 3.141033445 (error 0.02 percent).

Serial correlation coefficient is -0.000568 (totally uncorrelated = 0.0).

测试的结果分析,得到随机数比较理想。

fpga 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)