利用FPGA的自身特性实现随机数发生器

本文主要介绍利用FPGA的自身的特性实现随机数发生器,在Virtex-II Pro开发板上用ChipScope观察随机数序列,以及在PCIe4Base(基于Virtex-4 FPGA)上实现。

基本的原理

随机数在计算机科学中的密码学中有着重要的用途,常常被用作密钥的来源。随机数包括伪随机数以及真随机数。伪随机数是通过一定的算法计算得出,具有类似于随机数的统计特征,这样的发生器称为伪随机数发生器。而真随机数是通过物理现象产生,例如使用电子元件的噪声、核裂变等等作为噪声源[2],这样的随机数发生器叫做物理随机数发生器,也叫做真随机数发生器(TRNG:Ture Random Number Generator)。

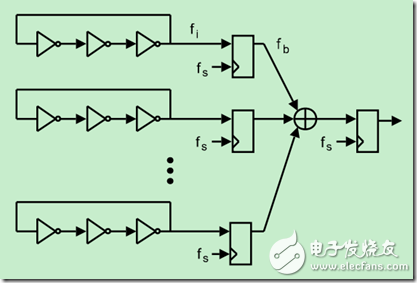

基于FPGA的随机数发生器基本原理是利用奇数个反相器组成振荡器作为随机数发生器的噪声源,因为由于FPGA自身的特性--信号传输存在抖动,所以多个反相器组成振荡器输出也不是很稳定的时钟信号,每个振荡器输出不是相同的,这样成为了理想的噪声源,见图1。振荡器输出通过D触发器进行采样输出,采样频率是fs,然后多个采样输出结果经过异或门之后再通过一个D触发器进行采样,采样频率还是fs。这样简单的随机数发生器就完成了。

图1.随机数发生器原理图[1]

实现

根据前面所述的原理图,进行如下设计:抽样频率是fs为50MHz,用3个反相器组成一个振荡器,共用了25个振荡器。因为整个结构很简单,这里就不多讲述,主要想说的是振荡器的描述。为了避免综合器将振荡器进行一定的优化从而背离当初的设计,所以在代码中添加了属性语句,用于保证网络不被优化掉。见28至31行,36至39行。

1: library IEEE;

2: use IEEE.STD_LOGIC_1164.ALL;

3: use IEEE.STD_LOGIC_ARITH.ALL;

4: use IEEE.STD_LOGIC_UNSIGNED.ALL;

5: ---- Uncomment the following library declaraTIon if instanTIaTIng

6: ---- any Xilinx primiTIves in this code.

7: library UNISIM;

8: use UNISIM.VComponents.all;

9:

10: entity Ring_osc_3 is

11: port ( clk : in STD_LOGIC;

12: D_out : out STD_LOGIC

13: );

14: end Ring_osc_3;

15:

16: architecture Behavioral of Ring_osc_3 is

17: ---------------------------------------

18: -- Interial signal in the Ring_OSC

19: ---------------------------------------

20: signal delay1 : std_logic;

21: signal delay2 : std_logic;

22: signal delay3 : std_logic;

23:

24: ---------------------------------------------------------------------

25: --Attributes to stop delay logic from being optimised.

26: ---------------------------------------------------------------------

27: attribute keep : string;

28: attribute keep of delay1 :signal is "true";

29: attribute keep of delay2 :signal is "true";

30: attribute keep of delay3 :signal is "true";

31:

32: ---------------------------------------------------------------------

33: --Attributes to stop trim logic from being optimised

34: ---------------------------------------------------------------------

35: attribute s : string;

36: attribute s of delay1 : signal is "true";

37: attribute s of delay2 : signal is "true";

38: attribute s of delay3 : signal is "true";

39: 40: ---------------------------------------

41: --Code start

42: ---------------------------------------

43:

44: begin

45: --osc_out is the last invertor output,

46: --and also the output feeds back to the first invertor

47: --invertor 1

48: inv_lut1: LUT1

49: generic map (init => X"1")

50: port map (

51: I0 => delay1,

52: O => delay2);

53:

54: --invertor 2

55: inv_lut2: LUT1

56: generic map (init => X"1")

57: port map (

58: I0 => delay2,

59: O => delay3);

60:

61: --invertor 3

62: inv_lut3: LUT1

63: generic map (init => X"1")

64: port map (

65: I0 => delay3,

66: O => delay1);

67:

68: --D Flip-flop

69: D_ff : FD

70: port map (

71: D => delay3,

72: Q => D_out,

73: C => clk);

74:

75: end Behavioral;

振荡器最后综合出来的结果是(图2):

fpga 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)