ZedBoard学习手记(二) 开发自定义AXI总线外设IP核

时间:02-11

来源:网络整理

点击:

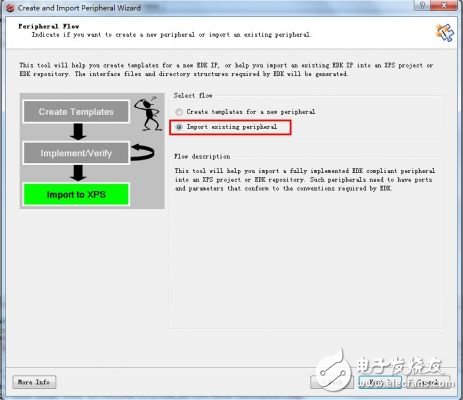

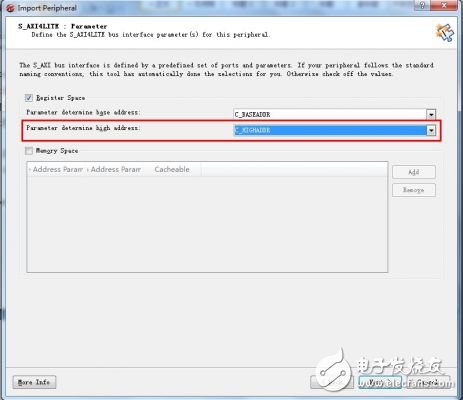

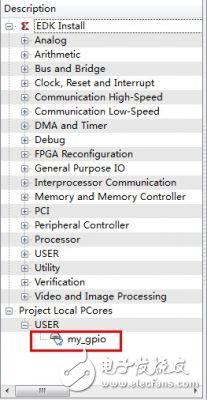

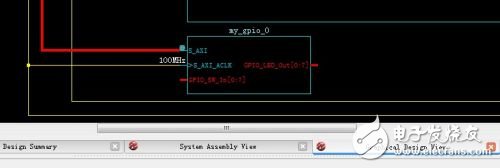

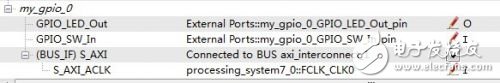

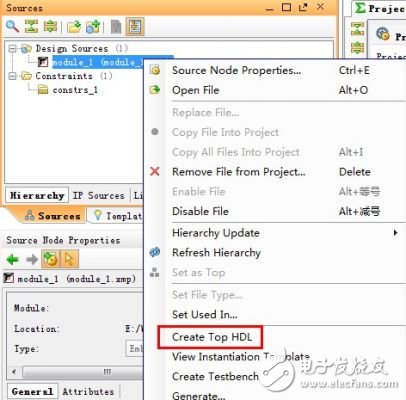

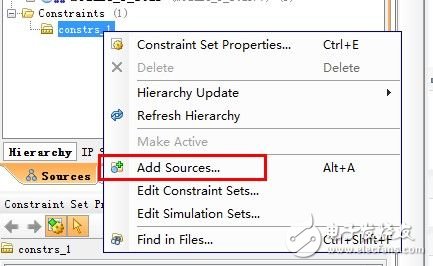

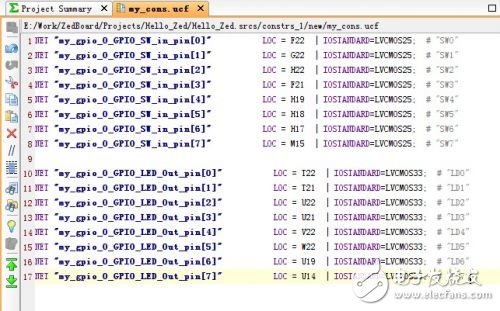

我们的自定义IP已经在列表中了,但是这个时候将IP添加到工程中,刚才进行的编辑并不生效,GPIO端口并没有显示在IP核的框图中,这点兔子没有搞明白是为什么,可能要手动修改MPD文件吧。于是我选择将这个IP再添加一次(不得已而为之,有什么好办法望不吝赐教),还是刚才的方法,只不过这回选择导入已有的外设,这种方法也可以用于导入其他已有的IP核。