ZedBoard学习手记(二) 开发自定义AXI总线外设IP核

时间:02-11

来源:网络整理

点击:

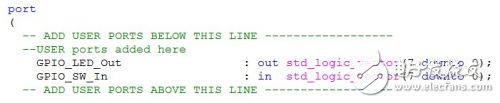

user_logic中除了一些定义和信号连接以外,就是两个always块,第一个实现AXI总线向用户寄存器写入数据,第二个则是总线从寄存器中读取数据。需要注意的是,这里的AXI总线已经通过Xilinx的AXI Lite IP Interface进行了中转,到用户这里就变成了非常简单的读写逻辑。为了控制板上的硬件,我们定义两组信号和相应的寄存器:SW_In信号连接8个Switch,LED_Out连接8个LED。input [7:0] SW_In;output [7:0] LED_Out; 在这里,规定寄存器0为SwTIch状态寄存器,寄存器1为LED控制寄存器。添加一个always块,使写入寄存器1的数据在LED_Out上更新。 always @( posedge Bus2IP_Clk ) begin if ( Bus2IP_Resetn == 1'b0 ) begin LED_Out <= 0; end else begin LED_Out[7:0] <= slv_reg1[7:0]; end end // LED_OUTPUT_PROC 同时添加逻辑让Switch的状态通过简单的同步(不是去抖啊)写入寄存器0。 // implement slave model register read mux always @( slv_reg_read_sel or slv_reg0 or slv_reg1 ) begin case ( slv_reg_read_sel ) 2'b10 : slv_ip2bus_data <= slv_reg0; 2'b01 : slv_ip2bus_data <= slv_reg1; default : slv_ip2bus_data <= 0; endcase end // SLAVE_REG_READ_PROC always @( posedge Bus2IP_Clk ) begin if ( Bus2IP_Resetn == 1'b0 ) begin SW_Reg0 <= 0; SW_Reg1 <= 0; slv_reg0 <= 0; end else begin SW_Reg0 <= SW_In; SW_Reg1 <= SW_Reg0; slv_reg0[7:0] <= SW_Reg1[7:0]; end end // SWTICH_INPUT_PROC 之后还要修改读写逻辑,将case ( slv_reg_write_sel )下的2'b10项注释掉,令寄存器0只读(对写入的数据Not Care),寄存器1则可以读写。如此,我们的用户逻辑就完成了,简单吧。别忘了还要在my_gpio.vhd中为用户逻辑添加端口,两组信号在整个IP的对外接口中分别命名为GPIO_LED_Out和GPIO_SW_In。

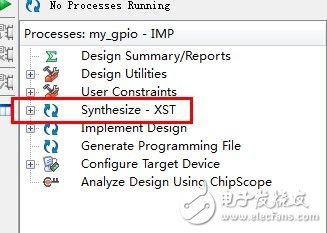

回到XPS界面,

回到XPS界面,