玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯

电子发烧友网核心提示:ZedBoard开发板上的Zynq是一个ARM PS(processing system, 双核A9 + 存储管理 + 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 开发一样。不同的是ARM PS是可配置,因而硬件信息是不固定的。这也是zynq灵活性的一个表现。电子发烧友网编辑现为读者整合《玩转赛灵思Zedboard开发板》系列文章,其中包括在ZedBoard开发板上的一些应用实例。其内容包括:

玩转赛灵思Zedboard开发板(1):ZedBoard详解

玩转赛灵思Zedboard开发板(2):ZedBoard最简单的测试工程

本文为玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯,内容精彩,敬请对电子发烧友网保持密切关注。基于Zynq PL的流水灯是使用PL做流水灯实验,目的是为了熟悉在不使用ARM PS情况下,只对Zynq PL的编程方法;同时掌握Xilinx PlanAhead工具的使用方法。本文给出流水灯实现过程的详细步骤截图。更多赛灵思(Xilinx)Zedboard基础知识、相关手册以及应用实例将陆续推出,以飨读者,敬请期待。【本文的完整工程文件下载:见本文最后。】

硬件平台:Digilent ZedBoard;开发环境:Windows XP 32 bit;软件:XPS 14.2 +PlanAhead 14.2。

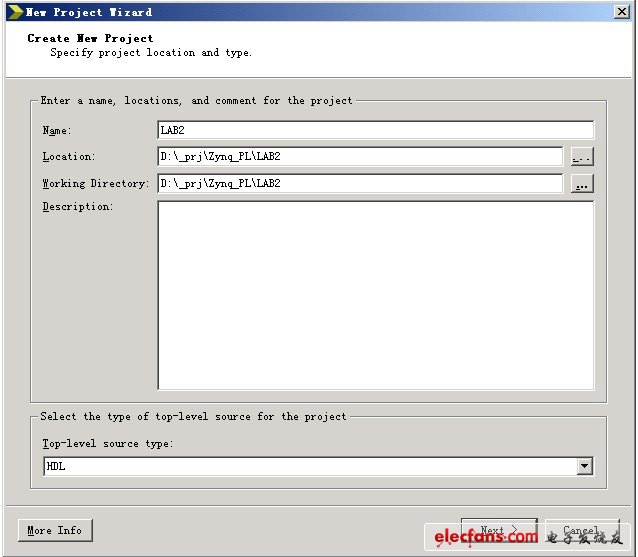

一.新建工程LAB2

如下图,新建工程文件LAB2,若对新建工程文件不熟练,可参考《玩转赛灵思Zedboard开发板(2):最简单的测试工程》中的实例介绍。

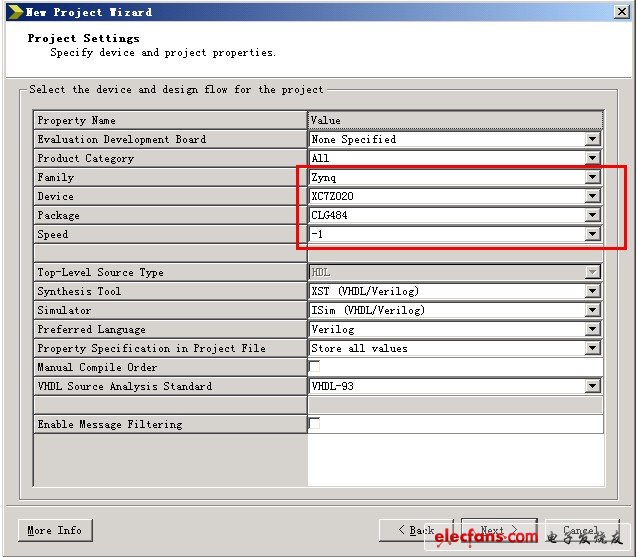

二.项目设置中,需要将芯片选为Zynq

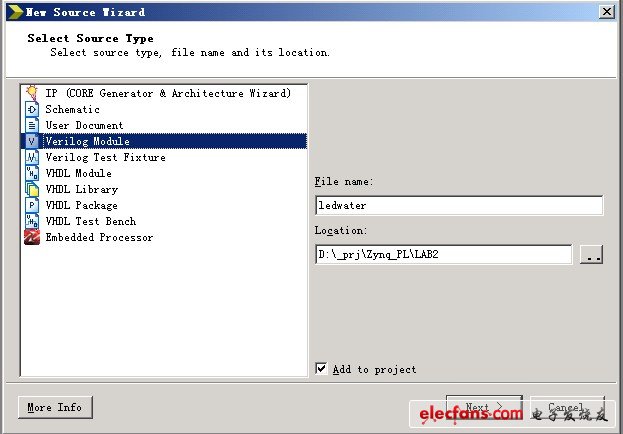

三.选择文件类型为verilog,名称就ledwater

之后会提示引脚信息,默认空就可以。

四.verilog源代码

通过verilog代码来实现。进入ISE后,添加源文件,内容如下

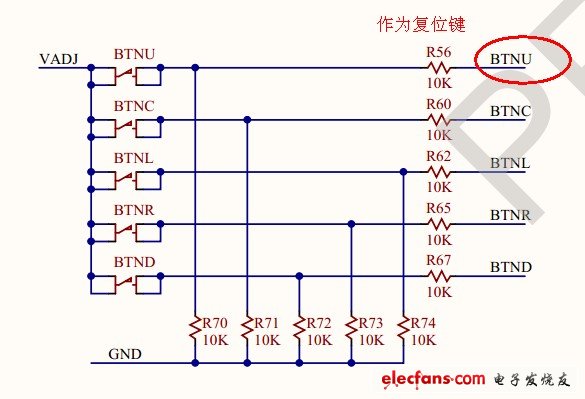

这里设定BTNU为复位,GCLK是时钟

五.ZedBoard引脚约束设定

查看ZedBoard的原理图,可以知道BTNU默认是低电平。

为了实现rst下降沿复位,第38句使用了一次取反

assign rst = ~BTNU;

小灯的移位采用"左移1位+右移N-1"模式,第29行可以看出来

LD_reg <=(LD_reg>>1)|(LD_reg<<7);

设定引脚约束,ucf内容如下。LOC表示引脚锁定,IOSTANDARD表明引脚电平。完整的ucf文件可以从Diligent官方网站上下载

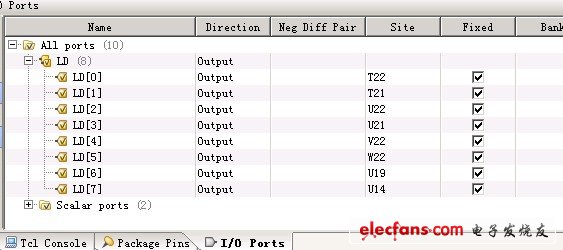

使用PlanAhead I/O pin planing(post synthesis)可以看到引脚约束的结果

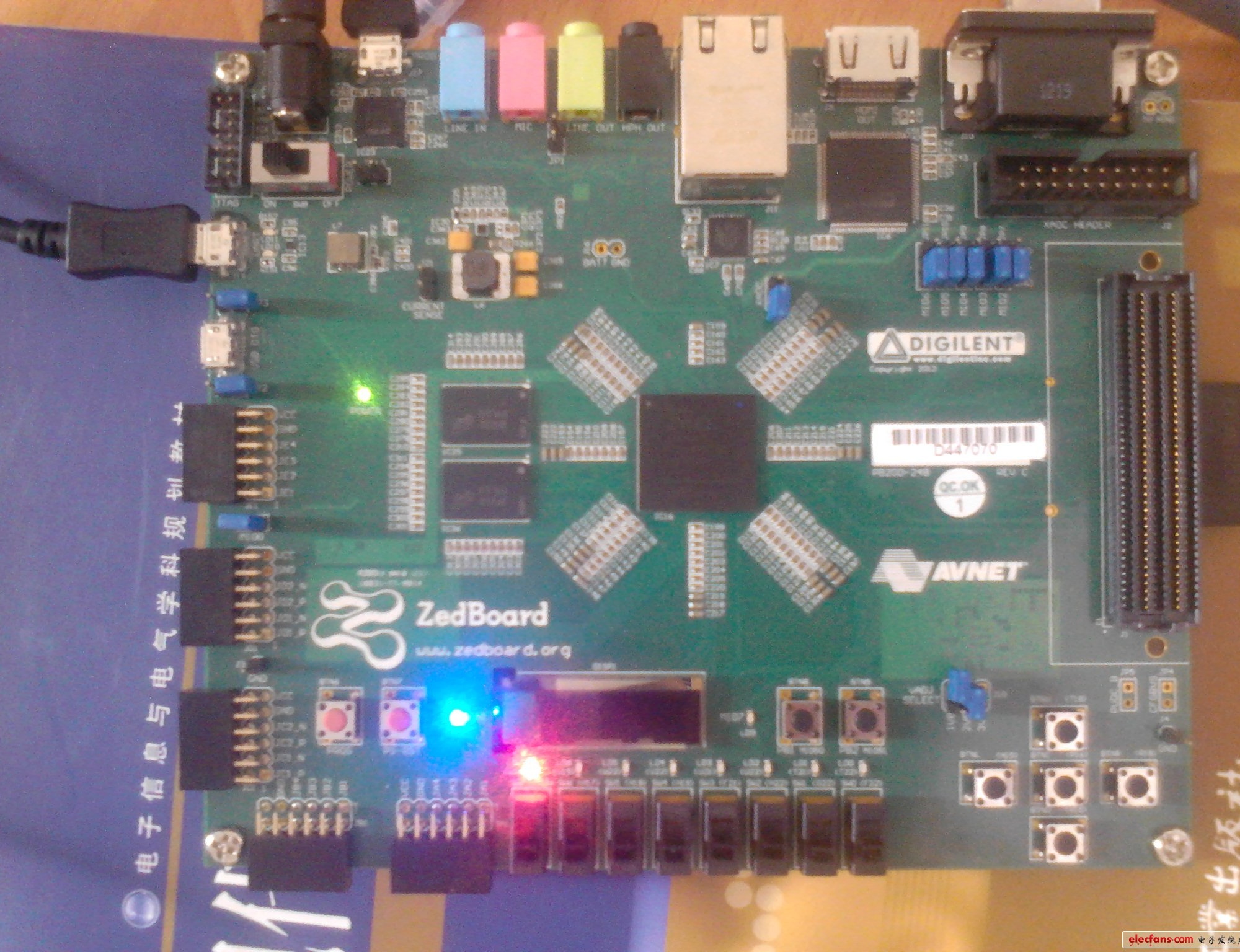

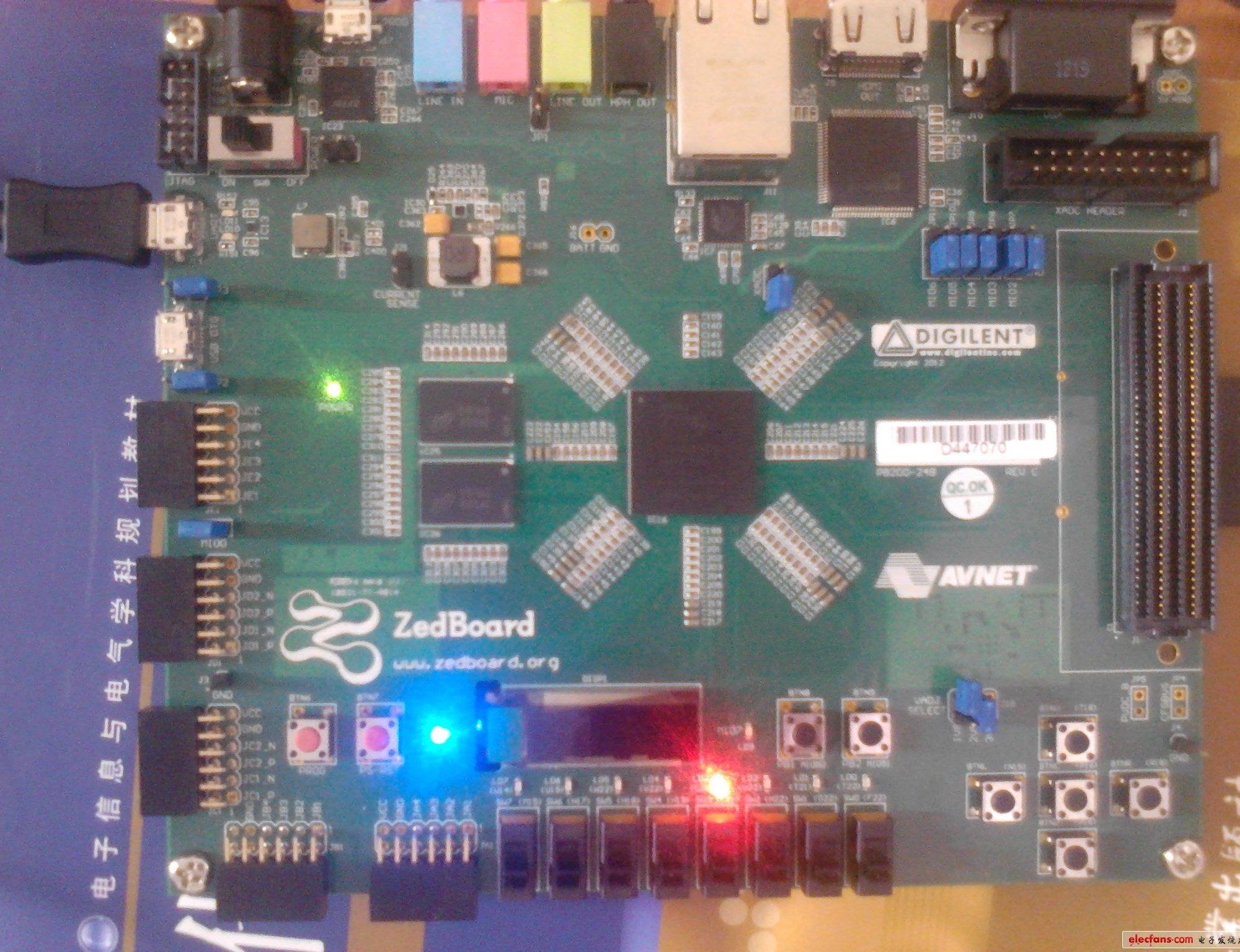

六.流水灯实现效果展示

下载之后能看到板子上LD0~LD7流水效果

完整工程文件下载:一步一步学ZedBoard:使用PL做流水灯(完整工程文件下载)(即:LAB2.rar)

——电子发烧友网整理,转载请注明出处!