使用ADSP-CM408F ADC控制器的电机控制反馈采样时序

C过载,或造成无效的ADC数据。它们包括:

· 触发溢出。当前帧结束前便触发下一次事件。

· DMA带宽。帧结束所需的时间长于用户定义时间。

· 存储器错误。ADC数据写操作失败。

· 事件冲突。处理现有事件时发生新事件。

· 事件错失。事件未处理。

这些错误均可按需配置为内核的中断源,并且它们都会置位ADCC_ERRSTAT寄存器。在电机控制应用中,尤其在电流反馈测量中,与事件错失、存储器和触发溢出有关的错误对于监控核心应用非常重要,因为错误或错失的电流环路数据可能会导致控制环路的不稳定。事件冲突在流水线操作中非常普遍,通常影响不大,除非FIFO已满。

ADCC模块、触发路由和存储器设置

使用ADC之前,需执行一系列步骤来设置ADCC模块以及触发路由单元和数据缓冲器。完成配置后,假定采用DMA数据访问模式,则DMA引擎会自动将主ADC数据传输至存储器,供主应用程序进行内部访问。当数据就绪时,ADCC产生中断,以便处理器执行控制算法并更新PWM调制器寄存器。

图17显示ADCC、CPU、SRAM、PWM和外部信号之间所需的互连,可用于在典型电机控制应用中捕捉电机电流反馈以及其他模拟监控信号。在本例中,编码器正弦和余弦信号、散热片温度和直流总线电压作为额外监控输入示例提供。

设置ADCC以便正确处理信号反馈的三个步骤如下所示:

1. ADCC事件配置。

2. 中断和触发路由。

3. 数据访问和存储器分配。

下列子段落描述正确设置系统所需的步骤与相应的寄存器配置。

图17. 典型电机控制应用中的系统互连

ADCC事件配置

ADCC事件的配置示例如图17所示,该示例包括为每个事件分配定时器、ADC接口和通道、时间偏移以及同步采样开关。这可以通过多种方法实现;图16以及表3所示为其中的一种可能情况。该示例采用全部两个定时器,仅供参考。

对于此示例,事件可连接至一个定时器,因为所有事件的定时都与PWM SYNC脉冲有关。

在诸如双轴电机控制算法这类用例中,可能必须同时使用两个定时器,因为该用例采用两组PWM输出以及相应的PWM sync脉冲。

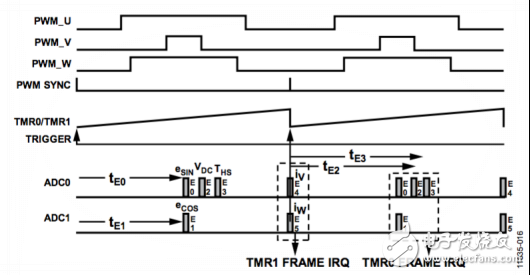

图16. 电机控制应用中的典型ADCC

表3. 示例应用的事件配置

相位电流iV和iW在发生PWM sync脉冲触发后立即同步采样,它们关联至TMR1。定时器1帧立即通过DMA传输至存储器,且新的电流样本可供主应用程序使用。在PWM周期中的较晚时刻,新的事件帧采样并关联至TMR0。

编码器正弦和余弦信号同步采样,紧随其后的是直流总线电压和散热片温度信号。

对三个ADC0信号进行流水线处理,以最大化吞吐速率。然后,将TMR0帧通过DMA传输至存储器。

这些参数的配置需设置ADCC_EVCTLnn事件控制寄存器和ADCC_EVTnn事件时间寄存器,nn表示每个事件的编号。提供本节内容涉及的驱动程序API,简化该过程。

中断和触发路由

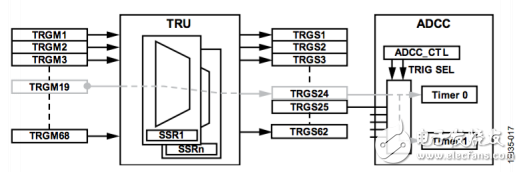

在图17中的示例中,所有事件时间均参考PWM周期;因此,两个定时器都由PWM SYNC脉冲触发。PWM sync脉冲作为硬件触发与ADCC定时器相关联的前提是配置TRU,使PWM sync脉冲作为主触发信号与ADCC触发从机相关联。随后,ADCC定时器必须与ADCC触发相关联。

图18显示相应触发路由的概念图;该路由涉及触发主机19 (PWM0 SYNC)与触发从机24 (ADCC_TRIG0)之间的连接,本例中该连接可通过将主机编号写入适当的从机选择寄存器TRU_SSR24来实现。之后,通过在ADC_CTL寄存器中为TRIGSEL位设置相应的值,将ADCC_TRIG0触发路由至两个定时器。

图18. 从PWM SYNC至ADCC定时器的触发路由

此触发路由配置可以提供硬件的直连链路,将PWM时序与ADC采样相关联,而不会在路径上产生软件延迟。触发主机也可从其他源路由,如GPIO引脚中断、定时器和计数器事件。如此配置便可提供精确同步,比如与ADSP-CM408F控制的其他转换器进行采样同步。

此外,完整的ADCC定时器帧能作为触发主机与其他外设或核心从机相关联。

由于本例中采用了DMA传输模式,因此所有事件中断都应当在ADCC_EIMSK寄存器中屏蔽。同样,提供驱动程序API,用来在寄存器中设置适当的中断服务例程,实现DMA模式下的帧中断。

利用触发路由提供增强型精确采样时序

像上文所述那样,要从当前采样时序中移除片选脉宽滞后,需要稍微不同的触发路由配置。在此情况中,ADCC定时器是通过GP定时器触发器触发的,而该触发器本身是通过PWM sync触发的。此序列可参见图11。

数据访问和存储器分配

如图14和图15所示,可通过读取内核MMR访问ADC数据,或通过DMA传输使其能在SRAM中访问。在

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)