使用ADSP-CM408F ADC控制器的电机控制反馈采样时序

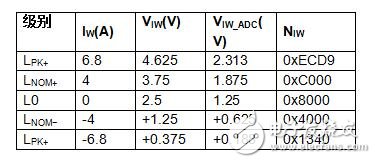

图4. 电流反馈信号幅度

表1. 电流反馈信号幅度

本示例采用连接LEM®,的CAS 6-NP霍尔效应传感器,其初级匝数为3,具有0 V至5 V输出,后接增益为0.5的信号调理电路。

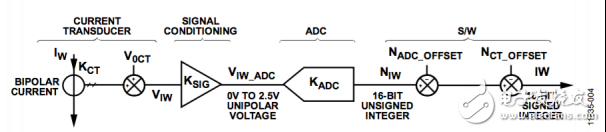

图5. 电流反馈路径的调整关系

ADC时序考虑因素

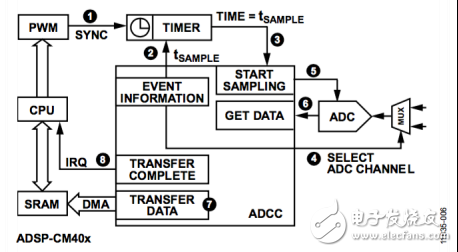

以PWM周期同步采样事件对于精确电流反馈而言非常重要。ADCC采用PWM周期工作的概念时序如图6所示。下列事件序列由PWM SYNC脉冲触发。

1. PWM sync脉冲触发定时器,以便启动。

2. ADCC不断将事件信息中的采样时间与定时器时间比较。

3. 完成定时器匹配,ADCC计划ADC操作。

4. ADC变为可用后,ADCC便使用事件信息选择适当的通道。

5. ADCC触发ADC转换序列,ADC采样并转换数据。

6. 数据回流至ADCC。

7. ADCC将数据通过DMA传输至存储器位置(LSB优先)。

8. 产生中断(IRQ),提醒CPU数据样本可用。

图6. ADCC操作序列

ADCC事件时序

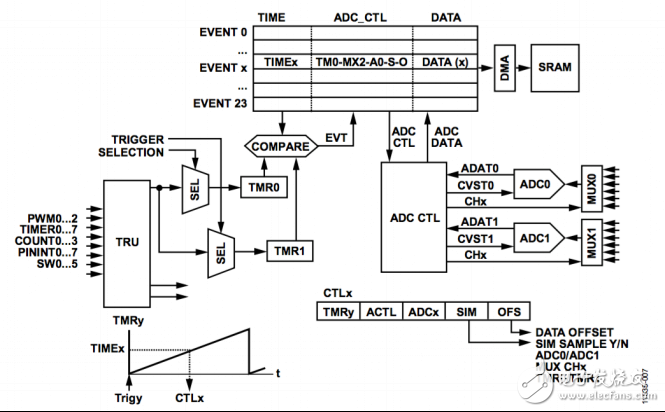

控制器管理最多24个采样事件的配置和时序。这些事件的时序受触发限制,该触发会启动两个定时器(TMR0或TMR1)中的其中一个,并在定时器启动后启动一个事件时间。

如图7所示,触发源可从一系列外设或处理器事件中选取,如PWM SYNC脉冲、定时器或I/O引脚中断。每次事件都与一个事件号码(以Event x表示)、一个事件时间(以TIMEx表示)、控制信息(以CTLx表示)及其结果数据相关联。事件控制信息(图7中以CTLx表示)包含每个采样事件的信息,如ADC接口和通道号、所用的ADC定时器、同步采样选择,以及相关事件ADC数据的存储器失调。ADCC使用该信息对正确的ADC通道(CHx)进行多路复用处理、初始化ADC转换(CVST0/CVST1信号)并将正确的数据传输至适当的事件数据寄存器中。

然后,可设置DMA传输,将每次事件的ADC数据移入SRAM中。完成所有事件和后续DMA传输之后,便产生一个中断,通知主应用代码新ADC数据可用。

图7. ADCC模块功能框图

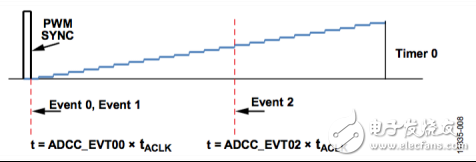

例如,图8显示与ADC定时器0有关的3个采样事件。PWM sync脉冲触发定时器,事件时间与每一次事件相关联。

事件0和事件1是同步采样事件,事件时间寄存器中的事件时间置零。事件2稍后发生,并同样由事件2时间寄存器确定,表示为ADC时钟周期(tACLK)的倍数。若事件2是与定时器0关联的最终事件,则定时器将在事件处理完成后停止运行,以降低功耗。

图8. 事件时序

ADC操作时序

ADCC控制器触发采样事件后,ADC操作本身具有一个转换时间延迟。图9显示单次ADC事件与每个ADC接口相关联,且使能两次事件同步采样的情况。

有三个独立的转换周期与ADC操作有关。

1. 写入8位控制字,选择ADC读取通道(ADCC_EVTCTL.CTLWD)。

2. 置位转换脉冲,使能ADC采样和转换。

3. 让16位ADC数据回流至ADCC。

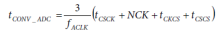

ADCC提供这3个事件相位的片选和选通时钟信号。ADCC与ADC的接口为串行接口,采用双通道位操作。因此,每个CS脉冲期间提供的最小时钟周期数(ADCC时序控制寄存器的NCK段)为8。其他重要的设置有:ADC时钟频率、转换周期片选信号之间的最小延迟(tCSCS)(ACLK周期内),以及CS边沿和ACLK边沿之间的最小延迟(tCSCK和tCKCS)。因此,单个同步采样信号对的ADC转换周期时间tCONV_ADC可表示为:

其中,fACLK表示ADCC时钟频率。

ADCC时钟由处理器系统时钟(fSYSCLK)通过ACKdiv分频(在时序控制寄存器ADCC_TCA中)在内部产生,计算如下:

其结果是系统时钟来源于处理器内核时钟(fCORECLK)。当fCORECLK为fSYSCLK的整数倍时,获得最佳系统性能。完成ADC转换后,额外延迟是因为ADC数据通过DMA传输至数据存储器,并最终由中断请求服务将数据帧准备就绪,供主应用程序使用。因此,在应用中,从触发(例如,PWM SYNC脉冲)到数据可用的总时间为:

tCONV_TOTAL = tCONV_ADC + tDMA + tIRQ

其中:

tDMA是DMA传输的平均时间。

tIRQ是中断请求服务的平均时间。

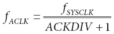

图9. 单次事件同步采样的转换时间

典型时序设置见表2。表中还列出了对时序的一些约束条件。获得正确ADC性能的绝对约束条件是,允许的ADC采样和转换周期(tCONV_ADC/3)必须至少为380 ns。单个同步采样事件的时序结果如图10所示,该结果与电机绕组电流的采样有关(注意,该图为了突出示例而略为夸大)。

图10. 采样延迟时间

采用这些设置时,在所需的电流波形采样点与实际采样点之间存在450 ns失调。该值等于一个片选脉宽(200 ns + 25 ns + 0 ns)加两次片选之间的脉宽(225 ns)。 该结果造成平均电机绕组电流和实际采样电流之间的ΔiSAMP产生差异,在时序调度中需加

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)