使用ADSP-CM408F ADC控制器的电机控制反馈采样时序

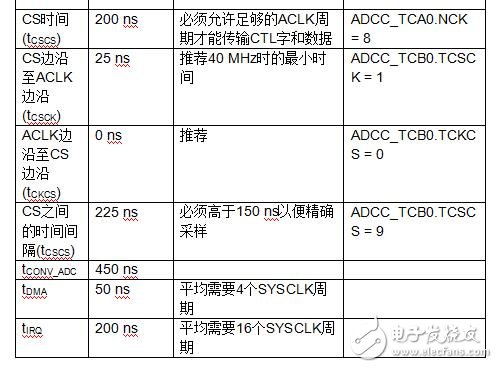

采用这些设置时,在所需的电流波形采样点与实际采样点之间存在450 ns失调。该值等于一个片选脉宽(200 ns + 25 ns + 0 ns)加两次片选之间的脉宽(225 ns)。 该结果造成平均电机绕组电流和实际采样电流之间的ΔiSAMP产生差异,在时序调度中需加以考虑,虽然在1 kHz的典型电流控制环路带宽环境中,这表示不超过0.2°的相移。此外,对于10 kHz的典型PWM频率,ADC数据从产生PWM SYNC脉冲(表2中的设置)起,在不足2%的可用PWM周期时间内可供应用程序使用。如果在事件发生时ADC处于空闲状态,则4至5个SYSCLK周期的额外延迟将存在于事件激活的时刻与ADC开始工作的时刻之间。

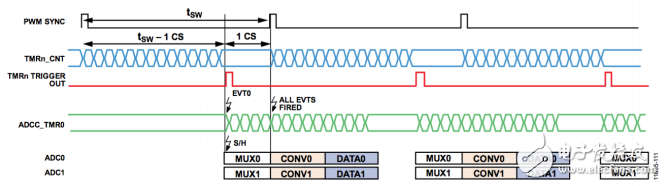

图11. 采样时刻调整的实现

表2. 典型ADC设置的时序设定

采样时刻调整

可能需要进一步提高电机电流采样时刻的精度并消除所需采样时刻和实际采样时刻之间的450 ns失调。精度提高后对低电感伺服电机等应用案例或者采用较高开关频率的情况特别有益。要消除这一较小的时间偏移量,一种方法是使用通用(GP)定时器在PWM sync脉冲前一个ADCC片选脉宽处创建触发。这可以通过从前一PWM sync脉冲触发GP定时器来实现,如图11所示。使用此方法时,在PWM周期结束前安排任何采样事件时必须谨慎。所有采样事件必须在下一周期开始前一个片选脉宽处完成(图11中的EVT0标记)。

ADC流水线

当新事件开始与ADC正在处理的现有事件重叠时,ADCC将新事件作为待处理事件存储在8深先进先出(FIFO)缓冲器中,该缓冲器可用于所有ADC接口。写入激活事件的控制字后,ADCC立即开始写入首个待处理事件的控制字,同时进入激活事件的采样阶段。同样,第一个待处理事件的控制字阶段执行完成后,便进入第二个待处理事件的控制字阶段。以这种方式,ADCC可在每个ADC接口上通过流水线方式交错处理三个并行事件。因此,事件能以紧凑高效的方式排列。

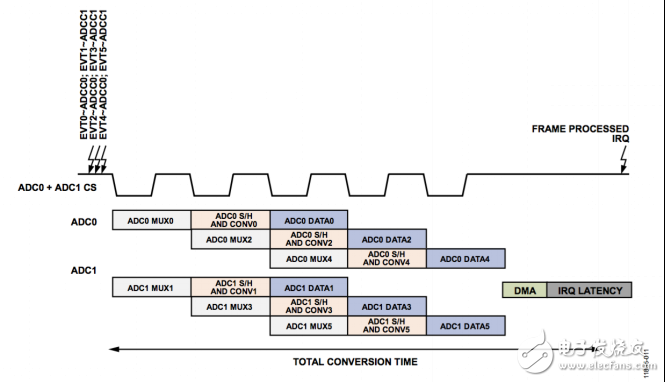

配置事件时序使事件以上述流水线方式处理,可获得最高的ADC吞吐速率。该流水线如图13所示。图中,三对同步采样事件的触发时间间隔很短。

图中,三对同步采样事件的触发时间间隔很短。ADCC开始处理事件0和事件1,同时将事件2至事件5存储在FIFO中。然后,ADC资源变得可用时,便会对这些事件进行处理。

从图7可知,在CS某次置位期间,ADCC会处理全部6个事件以及每个事件的多个阶段,并且两次连续采样之间的时间间隔仅为18个ACLK周期。该时间间隔相当于表2设置中的450 ns,且可通过提高ACLK频率进一步降低。若要在电机控制应用内最大化ADC带宽,最好的方法是有意识地将所有与PWM周期相关的采样事件以流水线方式处理。该方法可以确保新的ADC样本能在PWM周期中可能的最早时刻准备就绪。要实施图13中显示的流水线,则需要所有事件时间均接近零,即紧跟在PWM SYNC脉冲后。

建议在两个事件时间寄存器ADCC_EVTnn(nn表示0到24的寄存器编号)中存储的事件时间之间允许一个最小1 ACLK周期,实现正确调度。

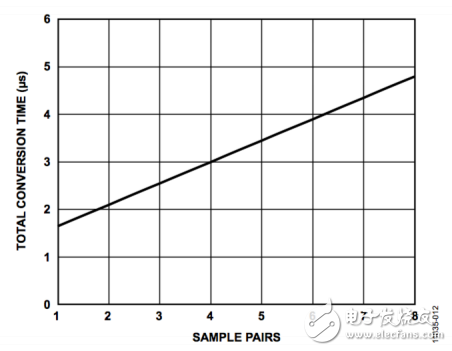

图12中显示使用流水线操作时的总转换时间,包括起始延迟、DMA传输和中断服务,可用于采用表2中所示时序设置的各种同步采样对数目。

图12. 不同采样对数目的总转换时间

图13. ADC中的流水线事件

ADC数据访问

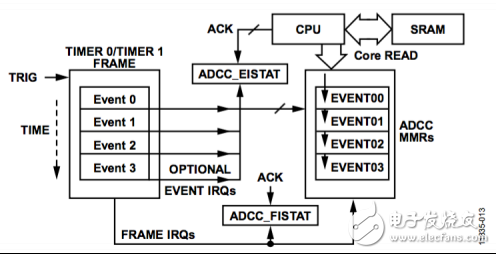

目前为止,本文中的示例都假定ADC数据采用自动DMA传输从存储器中访问。从ADCC存储器映射寄存器(MMR)的内核读数中直接访问数据是可行的,如图14所示。注意,图14中的ACK表示确认信号,而非模拟时钟。

图14 内核模式的ADC数据访问

在内核模式下,CPU通过事件或帧中断获取有关新数据就绪的信号,这些中断可按需独立屏蔽或解除屏蔽。该模式下还具有额外的灵活性:在整个事件帧结束前,一旦完成独立事件,即可对其进行读取。内核模式的缺点是中断服务以及MMR读访问所需的总延迟比DMA模式下要高。采用优化的内核和时钟分频比设定,则在每个中断服务的最高延迟情况下,每次MMR读操作将花费10至12个SYSCLK周期。

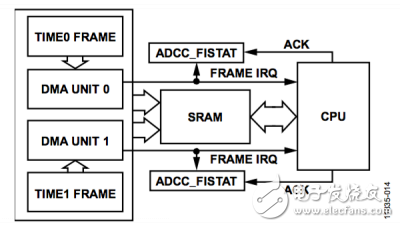

图15显示了DMA模式下的数据访问。

在这种情况下,DMA传输仅在完成一个定时器帧后才会发生,且帧中断信号仅在完成DMA传输后才发给CPU。

图15. DMA模式下的ADC数据访问

两种情况下,EISTAT和FISTAT寄存器都在激活后提供事件和帧中断的状态指示,且必须在下一次触发前经由CPU清零相关位确认,否则将标记一次触发溢出条件。

ADCC数据故障检测

ADCC提供多个故障状态寄存器位,发生数据故障时可置位;ADCC事件时序和/或不确定事件序列设置不当时,就有可能发生数据故障。这些故障可能使ADC

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)