基于千兆网的FPGA多通道数据采集系统设计

FPGA丰富的逻辑资源、充沛的I/O引脚以及较低的功耗,被广泛应用于嵌入式系统和高速数据通信领域。现如今,各大FPGA生产厂商为方便用户的设计和使用,提供了较多的、可利用的IP核资源,极大地减少了产品的开发周期和开发难度,从而使用户得以更专注地构思各种各样创意且实用的功能,而不是把大量时间浪费在产品的调试和验证中。

千兆以太网技术在工程上的应用是当前的研究热点之一。相比于其他RS-232或RS-485等串口通信,千兆以太网更加普及和通用,可以直接与Internet上的其他终端相连;相比于百兆网络,千兆以太网传输速度更快、传输距离更远,再结合UDP/IP协议栈,可以更方便地与上位机进行通信。

本文结合FPGA和千兆以太网灵活与快速的优势,设计了一个多通道并支持不同格式的数据采集系统。为了更好地为上位机软件所支持,搭建了一个简单的UDP/IP数据通道来完成数据到上位机的高速传输。同时,为了克服UDP这类不可靠的、面向无连接的协议带来的数据错误和缺失问题,使用一块DDR2SDRAM芯片来缓存各通道数据,在应用层制定了与上位机交互及丢包处理的通信协议,从而保证了采集数据到达上位机的可靠性。

1 系统总体结构

系统的设计目标是为了让不同通道、不同格式的数据都能通过同一个网络通道被快速无误地传递给上位机,由于设备与上位机运行状态的不同,采集数据速率的变化,甚至网线质量,使传输过程中的错误和丢包情况在所难免,所以需要有适当的机制和存储器缓存来保证传输的可靠性。

图1所示即为本系统的总体结构,除了使用一块DDR2 SDRAM芯片之外,网络模型中物理层的功能由一块PHY芯片来完成。目前一般PHY芯片均能兼容10Mbit·s-1、100Mbit·s-1、1 000 Mbit·s-13种速率的以太网传输,并向上层提供多种接口,如MII、GMII、RGMII和TBI接口等,对于上位机一侧则直接是普通的RJ45网口插槽。物理层接收数据链路层的并行数据,并将其转换为原始的比特流;同时也将原始比特流转化成并行数据,提交给数据链路层。

2 FPGA模块功能

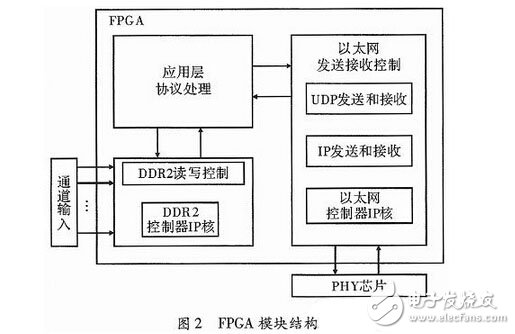

FPGA模块通过响应上位机的指令,完成数据采集、打包、传输、丢包重传等工作。所有工作的基础是MAC子层、网络层、传输层等OSI参考模型各层协议的可靠实现,每一层都按照标准接口向上一层提供特定服务,而把如何实现这些服务的细节对上一层加以屏蔽。

图2显示了系统FPGA模块的具体结构,以及各个子模块之间的关系。为缩短设计周期,提高设计质量,在模块中分别调用了Altera公司现有的以太网控制器IP核和DDR2控制器IP核资源。

2.1 DDR2读写控制

若不考虑网络中丢包的情况,数据一边采集,一边打包向上位机发送,是不需要外部存储器来缓存的。但是在实际测试中发现,目前普通配置的PC机无法承受千兆以太网的快速传输能力,丢包很常见,尤其是增加到多个通道时,设备向上位机的输出能力加大,丢包率也立即随之升高。所以,使用一片DDR2 SDRAM缓存各通道的数据是必要的。

设计中直接调用Altera公司提供的DDR2 SDRAM控制器,并选用一块它可以驱动的芯片来提高工作效率。芯片可使用的缓存空间是要重点关注的。每个通道都要分配固定的缓存区域,所以要将有限的内存空间作合理的划分。如果是图像数据,单个通道至少要有缓存两帧以上的空间。DDR2读写控制模块直接调用DDR2 SDRAM控制器IP核,但由于该IP核提供给用户端的接口使用不方便,需要按照其文档上介绍的时序来进行突发式读写。

本模块的功能主要是协调各通道采集数据的写入和读出。如图3所示,写操作时,各通道的数据首先用FPGA资源进行缓存,然后写入控制状态机通过轮询的方式依次检查各个通道已经缓存的数据量,如果足够一次突发写,则将其写入SDRAM芯片的相应通道块中,然后再检查下一通道;读操作时,读出控制状态机也依次检查各个通道写入SDRAM芯片的数据量,如果足够一次突发读,则将其读出,通过网络发送出去。

基于以上控制方式,设计对各通道的数据格式是不作限制,如图1中所示,可以是PAL、Camera Link、VGA等各种格式的图像或组合,只是在采集之前向上位机报告各个通道的数据信息。但需要说明的是,这些数据的带宽总和理论上不应超过千兆以太网的最大传输速率,这是采用轮询方式得以成功的前提。其实,如今普通PC机的处理能力远远不能达到这个最大限制,当速度到达100 Mbit·s-1时,上位机丢包就已经很严重。如果是将采集的数据在上位机上显示,最多可能只有70~80 Mbit·s-1;如果还要将数据写入硬盘,那数据率则

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)