专家支招:如何快速解决隔离FPGA设计中的错误

lify Pro/Premier 软件中生成时钟同步报告projectName_async_clk.rpt.csv:

Synplify Pro/Premier GUI:Analysis->Timing Analyst并选择Generate Asynchronous Clock Report 选项。

采用TCL命令: set_option -reporting_async_clock

正确的方法是确保您充分且全面地对设计进行约束,而且不会过度约束(过度会导致运行时间延长,生成关键路径错误报告)。确保您已完全指定多周期和错误路径,并且已为得到的时钟设置了约束(set_multicycle_path,set_false_path)。

缩短调试时间

实施潜在的RTL或约束故障解决方案可能需要好几个小时才能看出结果。我们来看看如何利用分级"分治法"设计方法和"错误继续"功能在单次综合迭代中发现多个错误,从而减少迭代次数。

为缩短运行时间,模块化流程必不可少。这种流程支持设计保存,能锁定已经证明有效的设计部分。支持模块化流程的工具能帮助您在进行综合前创建RTL分区,也就是编译点。一些软件还能帮助设计人员将有故障的设计部分变成黑盒子,彻底将该部分导出并作为独立的设计子项目进行再加工。一旦解决问题,子项目还能够以网表形式通过自下而上的流程或用作为RTL通过自上而下的流程整合回原设计,甚至还能综合利用自上而下和自下而上两种流程。

要集成和调试大型设计,应尽早在设计进程中发现错误的说明。举例来说,"错误继续"功能可提供涉及每个综合通过信息的组合错误报告。"错误继续"能容许非致命的非语法HDL编译问题和某些映射错误,因此设计人员可在每次综合迭代中分析并完成尽可能多的设计内容。为了在带有 SynplifyPro/Premier GUI 的Synplify Premier 软件中调用"错误继续"功能,应启用项目视图左侧的Continue-on-Error 选项。

在TCL中:set_option –continue_on_error 1

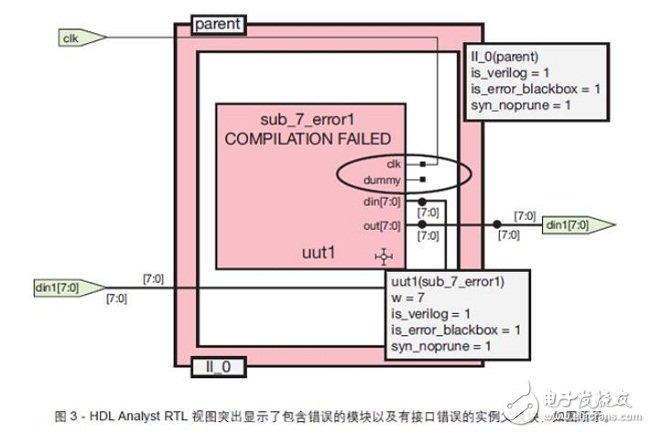

用属性is_error_blackbox=1 标记故障模块和带接口错误的实例父模块,如图3 所示。

用TCL找到所有"故障实例":

c_list [find -hier -inst * -filter

@is_error_blackbox==1]

用TCL列出所有"故障模块":

get_prop -prop inst_of [find -hier -inst

* -filter @is_error_blackbox==1]

要查看将被关入黑盒子或导出的故障模块,请查找HDLAnalyst RTL视图中的红色块(图3)。

通过导出模块隔离问题

您可将故障模块作为完全独立的综合项目导出,以便专门对该模块进行调试。导出过程会产生隔离的综合项目,其中包含所有该模块的源文件、语言标准和编译库,以及所含文件的目录路径和路径顺序,以达到对该模块进行单独综合与调试的目的。如前一节所示,出现错误的模块会自动在设计数据库中标出错误属性,并在设计原理图中突出显示,便于对该模块进行查找和提取。

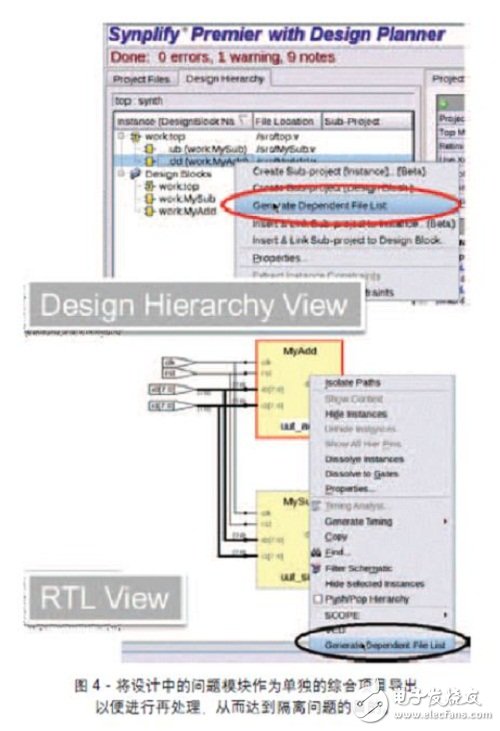

为了导出模块及其所有相关源文件进行隔离调试,应首先在Synplify Pro/Premier 软件GUI 中(图4)的设计分级视图或RTL视图中选择设计模块或实例,然后点击右键并在弹出菜单中选择"Generate Dependent File List"。

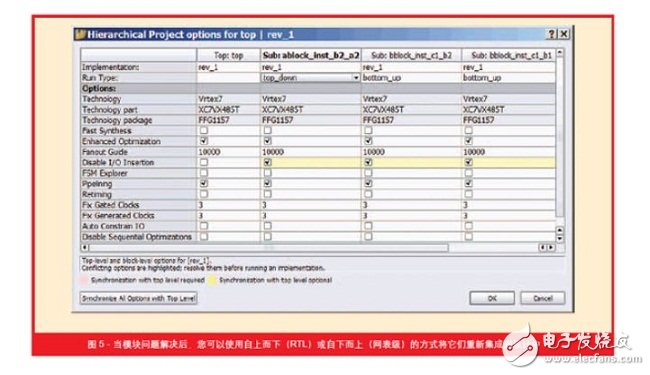

将每个分级模块的错误进行修复后,您可将其再集成到设计中,既可作为RTL在整个设计环境中重新综合(自上而下的综合流程),也可作为网表(自下而上的流程)进行综合(见图5)。

要满足时序要求就不可避免地要用到设计分级,这可能会带来挑战。层级界限可能会限制性能,除非为设计的每个层级分区建立时序预算。使用RTL分区(也称为手动锁定编译点)时,一些工具能自动设置时序预算。Synplify Pro/Premier 软件还能提供自动编译点,能创建自动分区,比方说通过多处理加速运行速度。预算功能为每个RTL分区建立接口逻辑模型(ILM),这样软件就能知道如何满足每个分区的时序目标。这样,您可为每个编译点指定一个约束文件,从而覆盖手动锁定编译点自动时序预算。

Synopsy 近期进行的全球用户调查发现,59% 的设计人员认为"设计规范的正确性"是最重要的设计挑战之一。这个挑战会造成设计延期,最坏情况下可能导致设计失败。设计工具必须能尽早捕捉到错误,并就设计工作提供更高的可视化,确保设计规范得到有效验证和修复。这些工具还必须就提出的设计修复方案提供反馈途径。

作者:Synopsys公司资深产品营销经理Angela Sutton

- 将音频编解码器植入28nm高级移动多媒体芯片系统(10-18)

- 将数据转换器IP集成到系统芯片简化设计技术(04-27)

- 探索性数据分析(EDA)及其应用(10-18)

- 霍尼韦尔“互联网+医疗”解决方案亮相2016中华医院信息网络大会(04-27)

- 基于EDA或FPGA的IP保护的实现(09-16)

- 基于MC8051 IP核和FPGA的频率计设计(11-24)