将音频编解码器植入28nm高级移动多媒体芯片系统

概述

音频处理对于手机、平板电脑等消费电子应用和其他大量生产的产品非常重要。面积和功耗往往是关键设计标准,而市场要求有高质量高保真(Hi-Fi)音频效果。将经过硅验证和优化的音频IP集成实现特定的音频功能,有助降低当今多媒体芯片系统的功耗、面积和成本。

随着设计逐渐过渡到28纳米工艺技术,集成音频功能这一挑战变得愈加复杂,原因是模拟电路并不遵循摩尔定律,也不会随着工艺发展而尺寸减小。采用28纳米工艺的晶圆成本会比65纳米或40纳米工艺技术高出许多。数字电路遵循摩尔定律,虽然晶圆成本提高,但是它的性能和密度也提升了。音频编解码器采用的模拟电路一般使用IO器件,因此不会像数字电路那样使用内核器件(core device)而减小尺寸。这样晶圆成本增加的同时,模拟电路固有性能并没有改善,面积也没有减小,因此必须开发新的架构以减少总面积。例如,采用65纳米技术、面积为2.5平方毫米的音频编解码器,在采用28毫米技术后面积需要减小至1.9平方毫米才能使硅成本保持相同。就是这25%面积的减小构成了对高级工艺节点音频编解码器的关键挑战。

本文研究了将音频功能集成在28纳米移动多媒体芯片系统上所面临的主要系统及技术挑战,以及如何通过以下技术应对这些挑战:

·利用摩尔定律,将部分功能从模拟改由数字来实现;

·灵活设计,支持芯片系统通用参考时钟的音频采样速率;

·做好好电源电压降低和性能之间的平衡;

· 深入了解芯片系统之外的系统功能划分;

认识到有措施可使系统成本最小化,设计人员和系统架构师将能够发现成本、功能和性能之间的有效平衡,使他们能够嵌入音频IP解码器解决方案,从而帮助他们的SOC在竞争中胜出。

音频编解码器基本知识

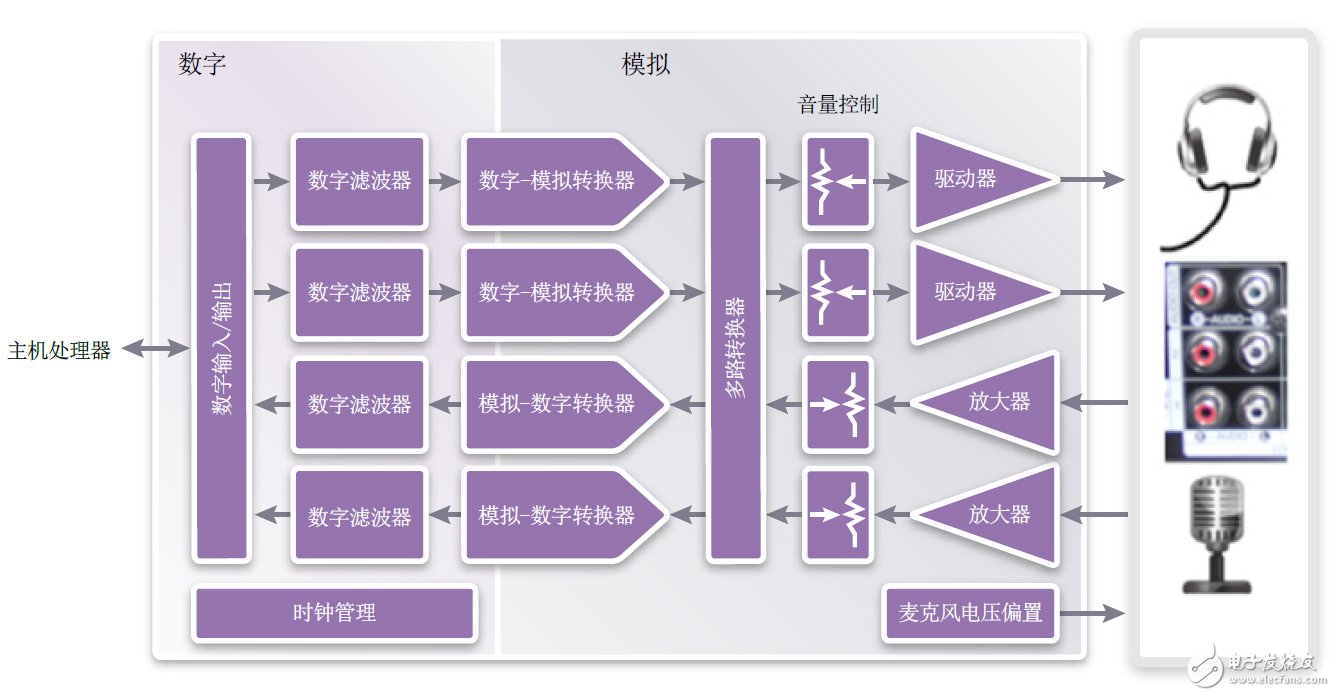

音频编解码器主要由两类数据转换器模块组成,即用于录音的模拟-数字转换器(ADC)和用于回放的数字-模拟换器(DAC)。对于立体声或多声道解码器,这些模块会被分别复制。图1是典型的立体声音频编解码器框图。 图中文录音声道包括具有音量控制的放大器,可将小信号麦克风和大信号线缆调整到模拟-数字转换器的输入范围。回放声道包括能够直接驱动耳机或小型扬声器放大,每路都分别具有音量控制功能。此外还有提供麦克风偏置的低噪音电源。

数字电路有多个部分构成,最重要的是数字音频滤波器,它可将数据速率转换为数据转换器的过采样时钟,并消除音频带外的高频噪声。时钟管理也很重要,它可确保不同速率的模块彼此保持同步,并支持多种采样速率。

图1:音频编解码器功能性框图

音频编解码器基本知识

开发高效的28纳米音频编解码器的第一步是利用更先进的工艺减少面积和提高总体性能。采用28纳米技术后数字性能显著改善,因此,明智的音频工程师会接受而不是反对向高级节点迁移。结果就是系统架构在数字域实现尽可能多的功能。通过将更多的信号处理从模拟域转到数字域,包括音量调节、混合和切换,音频编解码器可以利用先进工艺。结果是,数据转换器移到离外界接口更近的地方,从而简化了模拟布局,其他功能则保留在数字域,而数字域受益于先进工艺。

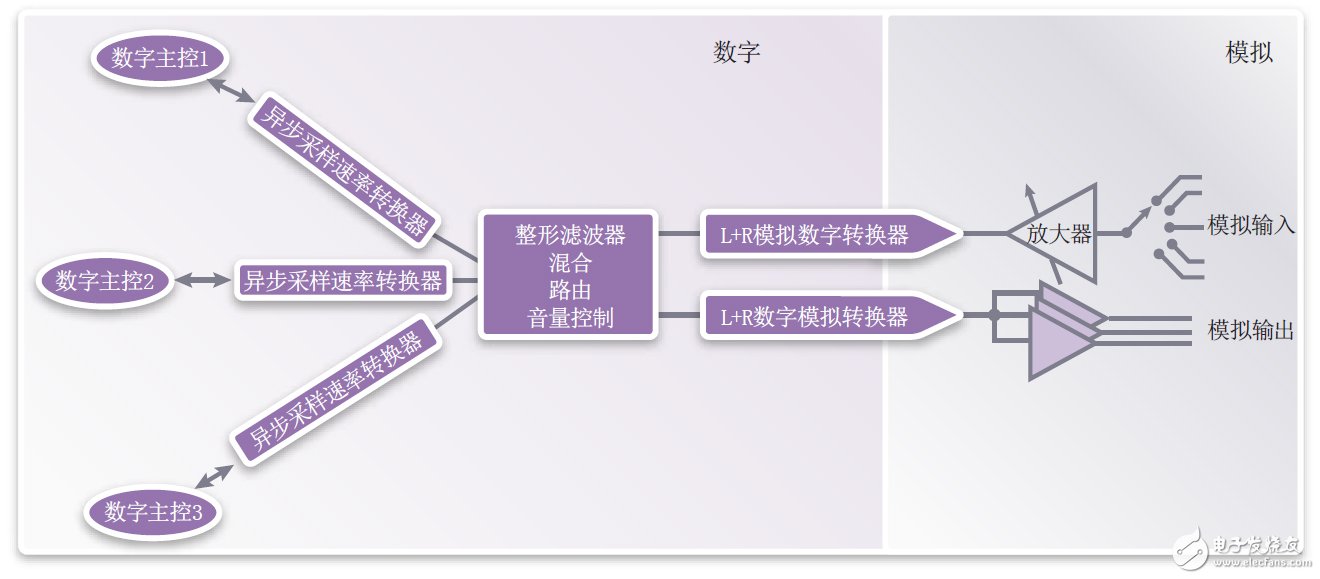

通过将更多信号处理从模拟域迁移到数字域,音频编解码器可提高符合摩尔定律的数字电路比例,并减少模拟电路比例。这产生了以数字为中心的新架构。在这种新架构中,所有信号处理都在数字模块执行,周边模拟电路包括数据转换器和异步采样速率转换器(ASRC),见图2。ASRC技术将在下一部分详细介绍。

现代移动多媒体系统有可能有多个数字主控,全部在各自的时钟域运行。例如,基带处理器将管理与蜂窝式无线电的通讯,应用处理器将管理来自系统闪存的媒体文件,而蓝牙集成电路(IC)可连接数量不限的蓝牙周边设备。每个数字主控都分别按照异步时钟速率运行。因此,这一系统中的音频编解码器不仅在数字域和模拟域之间架起了桥梁,而且还在数字生态系统中不同时钟域之间进行互动通讯。

图2:伴随数字音频主控进行以数字为中心的音频处理

灵活设计支持多个时钟速率

大量数字主控和时钟域给音频编解码器,特别是对高度集成的28纳米芯片系统造成了又一个挑战。按不同标准速率对数字音频采样,如表1所示。音频编解码器上数据转换器要求的时钟取决于音频数据采样速率和主机应用于芯片系统上的时钟。由于存在多种音频采样速率和各种主机时钟,它们的组合相当复杂。数字滤波器可为解决这一问题发挥重要作用,原因是它们可以处理数字音频接口和音频数据转换器之间的数据

- 将数据转换器IP集成到系统芯片简化设计技术(04-27)

- 专家支招:如何快速解决隔离FPGA设计中的错误(07-15)

- 10G以太网系统中的并行CRC编解码器的设计(02-11)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)